Logisim [Русский]

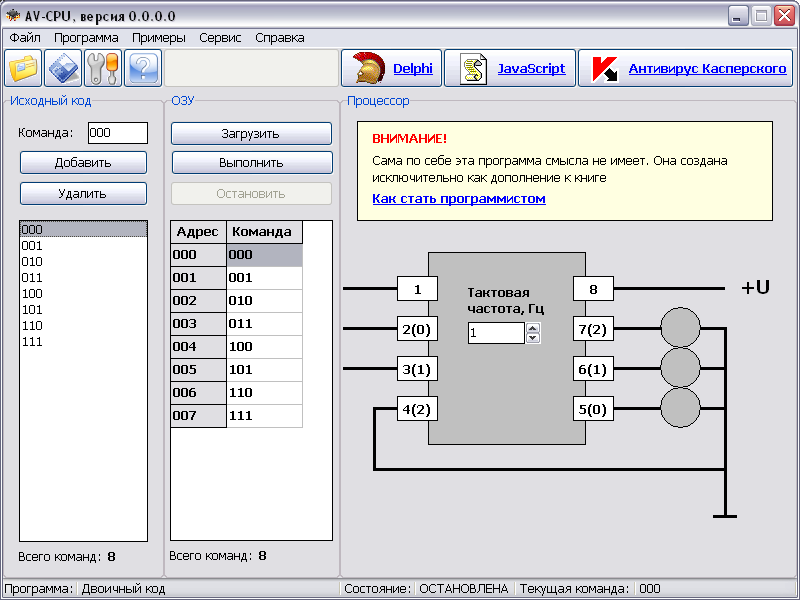

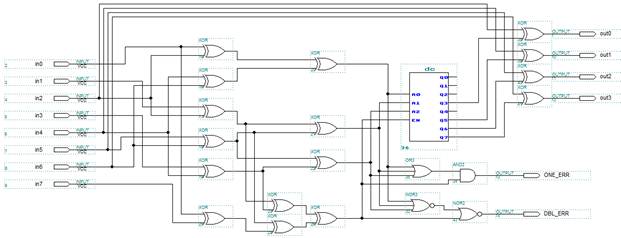

Снимок экрана Logisim 2.7.1

Обновление: Теперь доступен Logisim 2.7.1. Изменения по сравнению с предыдущими версиями. (21 марта 2011)

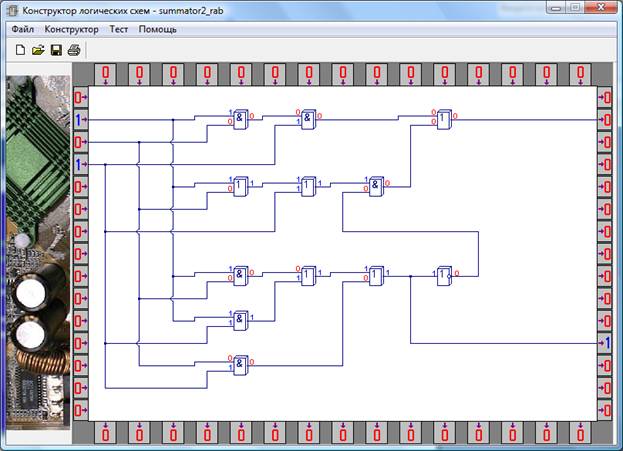

Logisim — это образовательный инструмент для разработки и моделирования цифровых логических схем. Благодаря простому интерфейсу панели инструментов и моделированию схем по ходу их проектирования, Logisim достаточно прост, чтобы облегчить изучение основных понятий, связанных с логическими схемами. При возможности постройки больших схем из меньших подсхем и рисования пучков проводов одним перетаскиванием мыши, Logisim может быть использован (и используется) для проектирования и моделирования целых процессоров в образовательных целях.

Logisim используется студентами колледжей и университетов по всему миру во многих типах курсов, начиная от краткого курса по логике в обзорном изучении информатики в общеобразовательных учреждениях, кончая курсами по организации ЭВМ и полными курсами по архитектуре компьютеров.

Logisim — программное обеспечение с открытым исходным кодом и работает под управлением Windows, Linux и Macintosh.

[Инструкции по загрузке Logisim]

[Документация на русском языке]

Использование русского перевода

Перевод на русский язык интерфейса программы и всей документации входит в состав стандартного выпуска Logisim (переводчик — Илья Лилов). Для использования русского перевода:

- После запуска Logisim, выберите пункт Preferences… из меню File. (На Macintosh выберите из меню Logisim.)

- Выберите вкладку International в окне Preferences.

- Выберите Russian из выпадающего меню Language.

Комментарии

Отчеты об ошибках, пожелания и вопросы (на английском языке, пожалуйста!) приветствуются на странице Logisim на SourceForge.net. Вы также можете связаться с Карлом Берчем (Carl Burch), основным разработчиком, прямо через cburch@cburch. com.

com.

Пишем эмулятор простых логических схем

from itertools import product

from copy import deepcopy

class Element:

"""

input_w -- количество входных проводов

output_w -- количество выходных проводов

type -- тип элемента ('составной' или 'NAND')

"""

def __init__(self, input_w, output_w, type='составной'):

# инициализируем нулями массивы входов и выходов

self.input = [0] * input_w

self.output = [0] * output_w

# указываем тип элемента

self.type = type

# создаём список для внутренних элементов

self.elements = []

# создаём список соединяющих проводов

self.wires = []

def push_element(self, element):

# проталкиваем элемент в список

self.elements.append(element)

# и возвращаем его номер в списке

return len(self.elements) - 1

def connect_wire(self, wire_a, wire_b):

# добавляем провод в список

self.

connect_wire(('in_self', 0), ('in', nand_id, 0))

# соединяем нулевой вход элемента NOT и первый вход у NAND

not_e.connect_wire(('in_self', 0), ('in', nand_id, 1))

# соединяем выходы

not_e.connect_wire(('out', nand_id, 0), ('out_self', 0))

# + можно сделать проверку на корректность результатов

not_e.input[0] = 0

not_e.execute()

assert(not_e.output[0] == 1)

not_e.input[0] = 1

not_e.execute()

assert(not_e.output[0] == 0)

""" Реализация AND """

# создадим элемент AND (два входа и один выход)

and_e = Element(2, 1)

# добавим NOT и NAND

not_id = and_e.push_element(deepcopy(not_e))

nand_id = and_e.push_element(deepcopy(nand_e))

# теперь соединяем провода

# B = X NAND Y

and_e.connect_wire(('in_self', 0), ('in', nand_id, 0))

and_e.connect_wire(('in_self', 1), ('in', nand_id, 1))

# A = NOT B

and_e.connect_wire(('out', nand_id, 0), ('in', not_id, 0))

# result = A

and_e.connect_wire(('out', not_id, 0), ('out_self', 0))

# и делаем проверку

for signal in product(range(2), repeat=2):

and_e.input = list(signal)

and_e.

signal[1], signal[0] and signal[1]]

assert(hadd_e.output == prof)

""" Сумматор """

# создаём сумматор (три входа и два выхода)

add_e = Element(3, 2)

# добавляем элементы

ha_id_1 = add_e.push_element(deepcopy(hadd_e))

ha_id_2 = add_e.push_element(deepcopy(hadd_e))

or_id = add_e.push_element(deepcopy(or_e))

# и соединяем провода

# я думаю вы сможете найти схему полного сумматора на двух полусумматорах

# и разобраться в этом коде!

add_e.connect_wire(('in_self', 0), ('in', ha_id_1, 0))

add_e.connect_wire(('in_self', 1), ('in', ha_id_1, 1))

add_e.connect_wire(('in_self', 2), ('in', ha_id_2, 1))

add_e.connect_wire(('out', ha_id_1, 0), ('in', ha_id_2, 0))

add_e.connect_wire(('out', ha_id_1, 1), ('in', or_id, 0))

add_e.connect_wire(('out', ha_id_2, 1), ('in', or_id, 1))

add_e.connect_wire(('out', ha_id_2, 0), ('out_self', 0))

add_e.connect_wire(('out', or_id, 0), ('out_self', 1))

# делаем финальную проверку по таблице истинности

table = [

# X Y Z S C

[0, 0, 0, 0, 0],

[1, 0, 0, 1, 0],

[0, 1, 0, 1, 0],

[1, 1, 0, 0, 1],

[0, 0, 1, 1, 0],

[1, 0, 1, 0, 1],

[0, 1, 1, 0, 1],

[1, 1, 1, 1, 1]

]

for x, y, z, s, c in table:

add_e.

input = [x, y, z]

add_e.execute()

assert(add_e.output == [s, c])

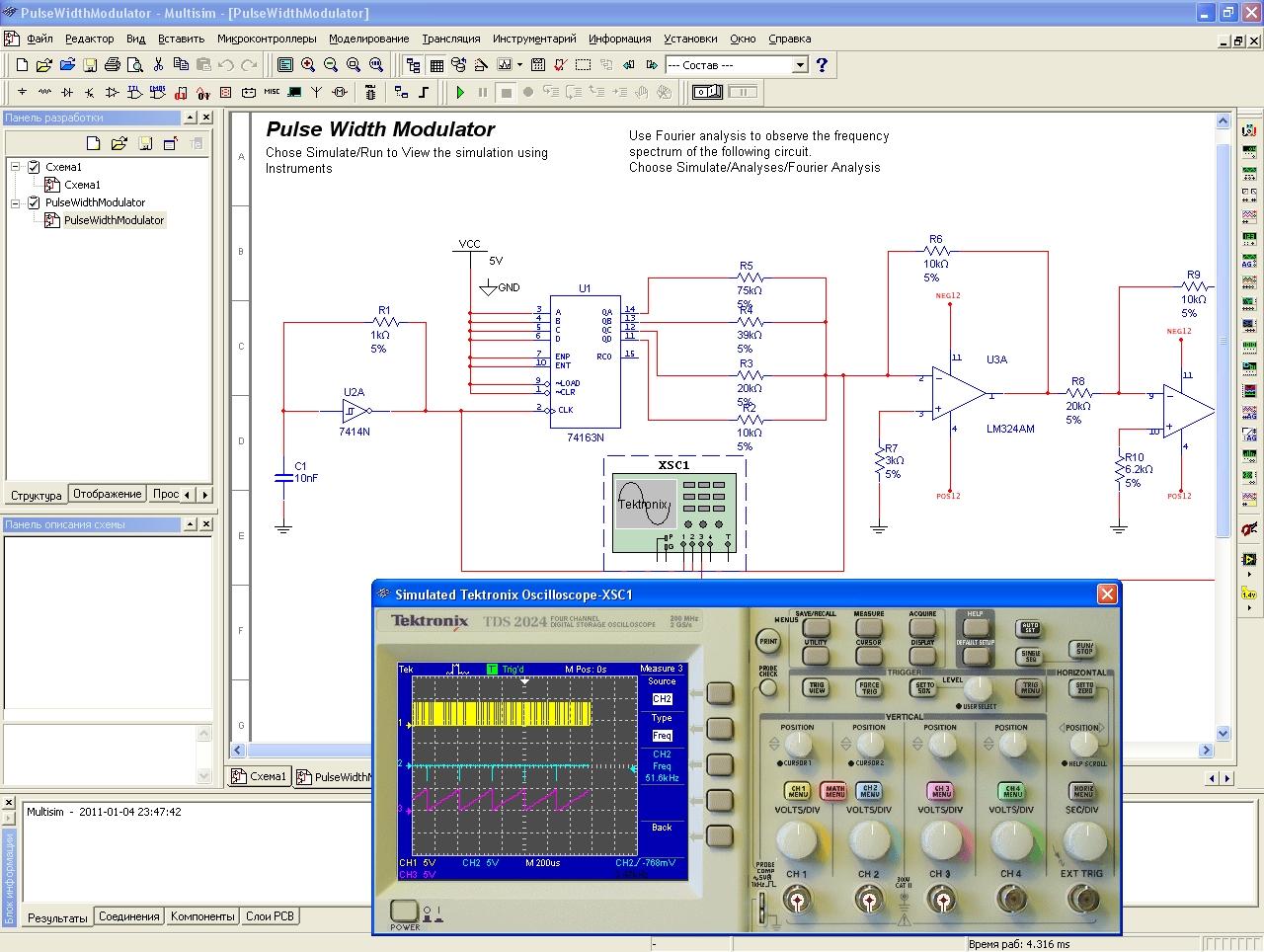

Популярный симулятор электрических схем под Windows для виртуального анализа.

MultisimMultisim — возможно самая продвинутая программа для создания и симулирования электронных схем и печатных плат.

Программа multisim — это целая лаборатория схемотехнического моделирования,

которая предназначена для разработки принципиалок и проектирования печатных плат на профессиональном уровне.

Multisim имеет простой удобный интерфейс и позволяет с легкостью моделировать сложные принципиальные схемы и

проектировать многослойные печатные платы. Просто нужно программу multisim установить на ваш компьютер.

Установка multisim выполняется быстро и просто. На этом сайте вы можете скачать бесплатно и на хорошей скорости.

Последняя версия multisim имеет новейшую графическую среду моделирования и новый эмулятор микроконтроллера.

В новой версии multisim значительно увеличен размер базы данных компонентов, а также увеличена производительность

и скорость компоновки элементов и разводки частей с помощью нового инструмента Ultiboard.

Программа multisim имеет новую возможность программно подключать к уже собранной электронной схеме виртуальные приборы,

переключатели, потенциометры для мониторинга изменения электронных величин в реальном времени.

Новый русский multisim скачать бесплатно

Программа multisim

инструмент устранения расходимости

параметризованные модели SPICE

вывод на электронные представления начальных условий

расширена функциональность электрического пробника

глубокий анализ схеммных решений с расширенными возможностями

совместная имитация микроконтроллера и MCU модуля

увеличение объема и качества базы компонентов

1200 новых компонентов от ведущих производителей

новые биполярные источники тока и напряжения

жидкокристаллические графические индикаторы

обозначение одним символом базовых логических компонентов

применение передовых методов моделирования

высокая скорость обработки объемной информации

эталонная точность и углубленный анализ

пригодна для использования в домашних условиях

успешно заменяет дорогое оборудование

возможно добавление новых электронных моделей

имеет простой в использовании интерфейс

способна имитировать работу компьютерной периферии

имитирует основные контрольно-измерительные приборыПрограмма представляет собой электронный конструктор, позволяющий

имитировать на экране монитора процессы сборки электросхем,

исследовать особенности их работы, проводить измерения физических

величин так, как это делается в реальном физическом эксперименте. Профессионалы знают, что программа для составления электрических схем помогает при настройке микроконтроллеров. Если Вы неудачно установили: Перед переустановкой почистите реестр от лицензий. Запускаем regedit.exe и ищем «national»; найденные ключи, только (!) если относятся к этой проге (сразу видно будет) удаляем. Доп. информация: National Instruments выпустила новые версии программных пакетов NI Multis 11 и NI Ultiboard 11. Симулятор последней версии программы обладает повышенной функциональностью, новыми возможностями пользовательского интерфейса и поддерживают более 300 новых компонентов от лидирующих мировых производителей. Благодаря новым возможностям разработка и создание прототипов электрических схем может проводиться гораздо быстрее и с большей точностью.

Профессионалы знают, что программа для составления электрических схем помогает при настройке микроконтроллеров. Если Вы неудачно установили: Перед переустановкой почистите реестр от лицензий. Запускаем regedit.exe и ищем «national»; найденные ключи, только (!) если относятся к этой проге (сразу видно будет) удаляем. Доп. информация: National Instruments выпустила новые версии программных пакетов NI Multis 11 и NI Ultiboard 11. Симулятор последней версии программы обладает повышенной функциональностью, новыми возможностями пользовательского интерфейса и поддерживают более 300 новых компонентов от лидирующих мировых производителей. Благодаря новым возможностям разработка и создание прототипов электрических схем может проводиться гораздо быстрее и с большей точностью.

С помощью конструктора можно:

— изучать зависимость сопротивления проводников от удельного

сопротивления его материала, длины и поперечного сечения;

— изучать законы постоянного тока — закон Ома для участка цепи и закон Ома

для полной цепи;

— изучать законы последовательного и параллельного соединения

проводников, конденсаторов и катушек;

— изучать принципы использования предохранителей в электронных схемах;

— изучать законы выделения тепловой энергии в электронагревательных и

осветительных приборах, принципы согласования источников тока с нагрузкой;

— ознакомиться с принципами проведения измерений тока и напряжения в

электронных схемах с помощью современных измерительных приборов

(мультиметр, двухканальный осциллограф), наблюдать вид переменного тока на

отдельных деталях, сдвиг фаз между током и напряжением в цепях

переменного тока;

— изучать проявление емкостного и индуктивного сопротивлений в цепях

переменного тока, их зависимость от частоты генератора переменного тока и

номиналов деталей;

— изучать выделение мощности в цепях переменного тока;

— исследовать явление резонанса в цепях с последовательным и

параллельным колебательным контуром;

— определять параметры неизвестной детали;

— исследовать принципы построения электронных фильтров для цепей переменного тока.

Multisim 11.0.2Программа _700Mb_DEPOSITFILES c таблеткой, русификатором и подробными инструкциями по установке

5 видеоуроков по Multisim_120Mb__DEPOSITFILES

6 книг самоучителей по Multisim__108Mb__DEPOSITFILES

App Store: Симулятор цифровых схем Lite

The most enjoyable and realistic Digital logic gates circuits simulator.

DigicalSim (ранее: iLogicDesigner) — полнофункциональное приложение, которое помогает студентам в логическом дизайне, цифровой инженерии, информатике и математике.

Приложение основано на базовых цифровых строительных блоках, логических воротах. Никакое знание логических ворот или цифровых схем не требуется.

Он предлагает базовые строительные блоки, инструменты для проводки и гибкую плоскость для создания живых цифровых схем реального времени, идеально подходящую для тех, кто хочет изучить основные принципы работы компьютеров — особенно студенты цифровой техники, научиться создавать простые логические ворота , защелки, триггеры, сумматоры, сдвиговые регистры и счетчики. он может помочь им выполнить полные лабораторные эксперименты.

он может помочь им выполнить полные лабораторные эксперименты.

► Особенности:

— AND, NAND, OR, NOR, XOR, XNOR, Buffer, NOT, jk Flip-Flop, D Flip-Flop, T Flip-Flop, Switch, Clock, Vcc, GND, VLink-Out, VLink-In, LED, 7-сегментный дисплей, светодиодный стековый бар и метка.

— Входные ворота (3 и 4) входа для ворот (AND, NAND, OR, NOR, XOR, XNOR).

— Многоцветные гладкие изогнутые провода.

— Возможность добавления виртуальных ссылок для аккуратных схем.

— Неограниченное прокручиваемое пространство самолета, для сверхбольших проектов.

— Режим запуска для просмотра чистой схемы при работе в режиме реального времени.

— Блокировка цепи, для безопасного запуска.

— Два режима работы переключателя (Toggle или Pulse).

— Синхронизированные генераторы синхронизируемых цифровых сигналов. с регулируемой частотой.

— Коммутаторы могут быть связаны с работой исключительно вместе.

— Оба эффекта положительного края и отрицательного края поддерживаются для триггеров с индикатором.

— Настраиваемый светодиодный цвет.

— Индикаторы живой стоимости на каждой ноге, для легкого анализа.

— Настраиваемый тег для элементов.

— Настраиваемые ярлыки можно добавлять в любом месте.

— Защелка сетки Design-Time для более удобного выравнивания и более чистого внешнего вида.

— Масштабирование и выключение. Также можно автоматически увеличить масштаб до Show Circuit extents.

— Persistent Circuit, он автоматически сохраняет текущую схему, которая будет завершена позже.

— Сохранение и загрузка цепей с помощью диспетчера файлов.

— Библиотека готовых примеров схем для быстрого запуска.

— Схемы Можно использовать и печатать.

— Переустанавливаемое начало схемы.

— Добавить еще одну цепь к текущей цепи.

— Выделите проводники ворот во время перетаскивания.

— Выбрать, снять выделение, дублировать, перемещать и удалять ворота в группах.

— Группы элементов могут иметь отличительный цвет и ярлык с настраиваемым шрифтом и цветом шрифта.

— Автоматическая прокрутка плоскости при достижении края при прокладке, перетаскивании или выборе.

— Упругий прямоугольник выбора для простого выбора элементов.

— Отменить функциональность, с 10 шагами назад.

— Прямая проводка для использования с Apple Pen.

— Поддержка Pick’n Drop.

Новости | Breaks — Nintendo Entertainment System / Famicom / Dendy emulator

2020-02-10 — GraphFlow

После всех пертрубаций с выбором движка (императивный движок на Си, реактивное программирование, симулятор Verilog и пр.) решил остановиться на движке графов.

Со временем программист «эволюционирует» от обычных массивов к спискам (List), а потом и к деревьям (Trees). Вершиной эволюции структур данных являются судя по всему графы (их можно наблюдать как в структурах молекул, так и в нейросетях и даже галактики формируют сетеподобную структуру, то есть это естественная структура данных во Вселенной)

Более подробная информация по устройству движка находится в его ридми: https://github. com/ogamespec/breaks/tree/master/GraphFlow

com/ogamespec/breaks/tree/master/GraphFlow

Также вместе с движком идут несколько примеров (SampleGraphs), с которыми можно побаловаться в программе.

В настоящее время ведется работа по переводу в граф схемы Famicom, которая затем будет сэмулируована вначале с применением HLE-графов, а потом по мере добавления логических схем и обычными логическими графами.

2018-12-02 — Новый движок сайта и вики

Сайт переведен на легковесный движок Pico CMS.

Все страницы сайта теперь представляют собой обычные Markdown текстовые файлы.

Заодно где можно исправил битые ссылки и сделал текст крупнее, чтобы на мобильных устройствах сайт выглядел современно.

На вики добавлен сертификат SSL, который бесплатно предоставляется хостером, а движок вики (DokuWiki) обновлен до последней версии и стиль изменен на более легкочитаемый.

EDIT 2020: Сертификат убрал по причине просрочки бесплатного периода использования.

2016-04-10 — Переезд на Github

В связи с закрытием Google Code репозиторий переезжает на Github:

https://github.com/ogamespec/breaks/

Разработка проекта продолжается, но не так агрессивно, как раньше. В качестве целевой платформы окончательно выбран DotNet / C#

Из целей проекта были убраны тестирование ядра 6502 на фриварных эмуляторах (так как архитектура ядра не подходит ни для одного Open source эмулятора), а также собственный NSF player.

2014-11-09 — Random logic

Завершена схема самой сложной части 6502 — рандомной логики и исполнительной логики (dispatch).

Схема работает в симуляторе и выполняет инструкции)

Следующий этап — проанализировать как 6502 производит управление нижней частью. Для этого нужно собрать данные какие он отправляет команды на каждом из циклов исполнения.

После чего можно объединить верхнюю часть с нижней и сделать полную симуляцию 6502.

2014-10-26 — Полная логическая схема обработки прерываний

Завершил разбор схемы обработки прерываний. Схема включает в себя все механизмы.

Вкратце принцип работы: входные сигналы /NMI, /IRQ, /RES поступают на входные триггеры.

Для обработки прерываний дополнительно требуется схема генерации 6 и 7 циклов (так как они не поступают с декодера) (контрольные сигналы BRK6E и BRK7). Причём контрольный сигнал BRK6E начинается во время PHI2 6-го цикла и заканчивается во время PHI1 7-го цикла. Сделано это для того, чтобы определить фронт (edge) сигнала /NMI.

Определением фронта /NMI занимается классическая схема edge detect на базе двух RS-триггеров.

Сигнал /RES дополнительно сохраняется на RESET FLIP/FLOP, так как он требуется для других схем рандомной логики (в частности для особого управления контактом R/W).

Факт прихода любого прерывания отражается на флаге B, выход которого (B_OUT) принудительно заставляет процессор выполнить инструкцию BRK (код операции 0x00). Таким образом разрабочтики унифицировали обработку всех прерываний.

Таким образом разрабочтики унифицировали обработку всех прерываний.

Последняя небольшая схема формирует адрес (или вектор) прерывания (контрольные линии 0/ADL0, 0/ADL1 и 0/ADL2), которые управляют младшими 3 разрядами шины адреса.

2014-01-30 — Симуляция PPU

Начаты работы по симуляции PPU, уже сделана самая большая и сложная часть (управляющая логика и генератор видеосигнала).

Новый подход в симуляции заключается в использовании программы Logisim. Программа имеет некоторые ограничения: нет двунаправленных контактов и использование бистабильных защёлок вызывает «возбуждение» схемы, но их можно обойти. Вместо двунаправленных контактов можно использовать спаренные I/O линии, а бистабильные ячейки памяти легко заменяются стандартными триггерами.

Удобной фичей программы является «инкапсуляция» отдельных схем в графические блоки, в виде черных ящиков 🙂

Схема полностью логическая, за исключением декодеров H/V, которые удобнее делать решеткой транзисторов (при необходимости их также можно заменить элементами NOR).

Основная задача — проверить логическую схему на правильность работы, чтобы потом её можно было симулировать более быстрыми способами.

Работа как обычно ведется в прямом эфире, за процессом составления схемы можно следить онлайн 🙂

2013-12-03 — Верилог

После некоторых раздумий было решено добавить Verilog-транслятор.

Это позволит симулировать схемы на естественном языке.

Разработка транслятора находится где-то по середине: уже готов лексический анализатор и парсер, но никак не могу определиться каким образом обрабатывать reg/wire в сочетании с input/output, а также как собственно транслировать полученное после парсера дерево.

http://wiki.breaknes.com/sim

2013-10-17 — Ошибка в адресной линии 6502

Найдены не замеченные ранее транзисторы в выходных схемах адресной линии 6502.

Особо этот косяк на логику не влиял.

(незамеченные транзисторы обведены кружочками)

В вики добавлено описание работы этих схем : http://wiki.breaknes.com/6502:address_bus

2013-09-28 — Что нового

Давненько не было новостей, но это не значит что ничего не происходит 🙂

- Я начал переводить все транзисторные схемы в «красивый» формат sPlan. Сделано это для того, чтобы создать подобие схемы Балазца с полным 6502 на ней.

- Очень много обновлений в вики. Что-то конкретного сказать точно не могу, почитайте, там много чего появилось ) Кстати вики переведена на новый дизайн.

- И я по прежнему нахожу ошибки в транзисторных схемах. На этот раз был обнаружен не замеченный ранее транзистор для вспомогательной схемы 6502 — JB (Jump/Branch).

- Была разрешена очередная «дилемма» в симуляции 6502, которую я называю «транзисторные гонки» (race conditions) или «Что было первее — курица или яйцо).

Про это (и конфликтные состояние шины) можно почитать в вики : http://wiki.breaknes.com/6502:control

Про это (и конфликтные состояние шины) можно почитать в вики : http://wiki.breaknes.com/6502:control

2013-09-13 — В стране кризис

Теперь можно помочь проекту, для приобретения профессиональной аппаратуры:

2013-08-23 — Первые минуты жизни 6502

Почти через год исследований стало наконец понятно, как начинает свою работу 6502.

Подробнее в вики : http://wiki.breaknes.com/6502:phi1

2013-08-19 — Улучшения отладчика

В отладчик добавлены новые элементы управления : «локаторы» и «коллекторы». Локаторы позволяют быстро перемещаться между блоками микросхемы, а коллекторы позволяют выводить и изменять сразу пачку битов (регистры, шины) посредством окошка ввода. Дублируемые галочки теперь изменяются одновременно.

Также добавлена поддержка закладок, при этом в каждой закладке отображается своя микросхема. Подчищен код проекта и полностью переведён на Qt.

Подчищен код проекта и полностью переведён на Qt.

Делаются попытки собрать статичную линковку Qt SDK, но пока безуспешные =)

2013-08-16 — Освоение Qt

Определился с внешним видом и функционалом отладчика и среды, в которой будет работать эмулятор.

Приложение работает на базе Qt, создание проекта происходит в QtCreator. Qt стал действительно мощным и удобным тулкитом.

Отладчик будет представлять собой окно, с загруженной туда картинкой транзисторной (или какой-либо ещё) схемой процессора и расположенными поверх неё виджетами.

Минимальный набор — это кнопка «Next Step», которая вызывает функцию Step() этой микросхемы, для симуляции одного полутакта.

Все контрольные линии, защелки и триггеры будут выглядеть в виде чекбоксов, которые можно щелкать, тем самым меняя значение с 0 на 1 и наоборот.

Задний фон совместно с чекбоксами может масштабироваться и скроллиться мышкой для быстрого перемещения по схеме.

Таким образом управляющие элементы топологически становятся привязанными к схеме, чтобы не запутаться.

Вначале я хотел сделать это через HTML5 + Webkit, при этом задник рендерился бы как GIS-карта, но мне не удалось победить чекбоксы — они прыгали по всей схеме, при изменении размеров окна. Поэтому сделал по другому — в виде QGraphScene (загрузив туда jpg) + обычные QWidgets.

2013-07-30 — Переход на sPlan

В связи с тем, что Circuitlab стала платной я стал искать новую среду, для рисования логических схем. Выбор пал на sPlan — универсальную программу для рисования любых схем.

Схемы всех процессоров будут постепенно переведены в формат sPlan и будут находится по постоянным адресам:

Пока производится перевод схем 6502 из Circuitlab в sPlan, параллельно на «другом компе» начаты предварительные работы по восстановлению логической схемы PPU.

2013-06-26 — Логические схемы нижней части 6502

Потихоньку идет к завершению процесс получения логических схем нижней части 6502.

В первую очередь была восстановлена схема «сердца» процессора — ALU

На очереди его «счетный орган» — Program Counter :

Также в целях проекта пригодились картографические программы. Вот что получилось: http://breaknes.com/files/6502/tilemap/

Edit 02.12.2018: Данный инструментарии был удален с сайта (не пригодился).

2013-06-25 — Проекту 1 год!

Незаметно так летит жизнь и суета вместе с ней. Примерно год назад стартовал этот проект.

Изначально планировалось завершить его к зиме 2013-го, но прошло уже пол года, а 3 старенькие микросхемы всё ещё хранят в себе множество тайн и загадок )

2013-06-19 — Обновления сайта и логическая схема 6502

На сайте произошло много внутренних изменений в плане движка, чтобы им было удобнее управлять. В частности появился новый раздел Новости (загрузка всех превьюшек с YouTube/Twitch стала занимать много времени)

В разделе Скачать кроме даты последнего обновления теперь можно посмотреть подробную историю изменений выложенных файлов, отдельно для 6502, APU и PPU.

Ну и главная новость — практически полностью восстановлена логическая схема верхней части 6502! (осталось исправить мелкую схему DL/DB). Сейчас я веду серию стримов, посвященную боданию с последовательностью выполнения процессора. Стало понятно, что хотя функционально процессор разбит на 2 части (верхняя и нижняя) — выполнять по очереди их нельзя, вся эта гребанная лапша работает совместно и дополняет друг друга 🙂

Транзисторные схемы 6502 были серьезно подчищены и для удобства разделены на верхнюю и нижнюю часть. Их теперь всегда можно получить по фиксированным URL.

Параллельно были подчищены схемы PPU, который следующий на очереди получения логической схемы

2013-05-31 — Обновил схемку спрайтовой FIFO

Обновил схемку спрайтовой FIFO (схема, в которой хранится текущие 8 спрайтов для вывода на строку) и добавил туда схему приоритета спрайтов. Схема оказалась хитрым каскадом из NOR, планирую сделать её логическую схему, ибо над логикой приоритета спрайтов уже достаточно долго бьются лучшие умы NESDEV-а. Попутно выяснил назначение одной неизвестной линии. Это оказалась важная «Sprite 0 Hit».

Попутно выяснил назначение одной неизвестной линии. Это оказалась важная «Sprite 0 Hit».

Все схемки PPU (включая трассировку) обновлены в соотв. разделе.

2013-05-22 — Исходники PSD для всех схем APU

После непродолжительного творческого хиатуса продолжаем!

В разделе Скачать появились исходники PSD для всех схем APU :

Попутно обновил топологию APU небольшими фиксами.

2013-05-05 — Схема адресного контроллера PPU

История началась с того, что мне на почту написал китайский студент и указал на ошибку в маленькой транзисторной схеме, которая располагается в самом низу чипа PPU.

На момент подробного изучения я знал только то, что она как-то связана с адресной шиной PPU. Оказалось что она более сложная и выполняет функции контроллера этой шины. Конкретно, она устанавливает контакты RD, WR и /ALE, а также выдает внутрь PPU ряд управляющих команд.

Закончилась вся история стримом, где мы общаемся с HardWareMan-ом и чешем репу в догадках о работе схемы.

В результате была получена логическая схема этого адресного контроллера, а также я обновил PSD файлы в разделе «Скачать» (DATAREAD и ADDRCTRL).

Более подробно про схему адресного контроллера >>> тут

Watch live video from ogamespec on TwitchTV

2013-04-30 — Завершение транзисторных схем

За время с последнего обновления произошло много новостей, перечислю вкратце:

- Схема DPCM APU стала последней крупной схемой семейства чипов NES, поэтому можно сказать что этап восстановления транзисторных схем 6502, APU и PPU завершён!

- В разделе Скачать выложена обновленная схема 6502, а также пережата топология PPU, в результате чего файл уменьшился с 220 Мб до 40 🙂 Связано это с тем, что хостинг не резиновый и мы вплотную приблизились к лимиту в 2000 Мб.

- В разделе Чтиво появилось несколько подробных описаний схем 6502.

После получения транзисторной схемы было решено восстановить логические схемы на уровне NAND/NOR, чтобы досконально изучить особенности работы и облегчить симуляцию чипа. В отношении APU/PPU планируется провести соответствующие работы.

После получения транзисторной схемы было решено восстановить логические схемы на уровне NAND/NOR, чтобы досконально изучить особенности работы и облегчить симуляцию чипа. В отношении APU/PPU планируется провести соответствующие работы. - Немного поработал над дизайном и внутренним содержимым сайта, надеюсь вам понравилось моё творчество 🙂

- Мы окончательно перебрались на новую платформу Twitch, которая позволяет стримить в HD-качестве, также решили проблему с импортированием видео на Youtube, а проблему со звуком решим в ближайшее время, путём приобретения гарнитуры.

2013-04-03 — Прогресс в APU: NOISE и TRIANGLE

Очередной прогресс в изучении APU : получены схемы шумового и треугольного каналов.

Также испытал новую платформу для стримов высокого качества Twicth TV + Open Broadcaster Software:

Watch live video from ogamespec on TwitchTV

Ну и сами схемы:

Осталась схема генерации DMC и парочка мелких вспомогательных схем.

2013-03-05 — APU квадратный канал

Квадратный канал. Записан уже целый ряд стримов, где мы пытаемся понять как устроена эта схема. В прямом эфире общаемся с Quietust-ом:

2013-02-20 — APU Length counters

Потихоньку начинаем разбор схем APU. В первую очередь были разобраны length counters, которым было посвящено 2 стрима:

В первую очередь были разобраны length counters, которым было посвящено 2 стрима:

Схема:

А также готова схема спрайтовой DMA, подробнее можно почитать в разделе «Чтиво».

2013-02-16 — Отличия встроенного в APU 6502

После детального изучения схемы 2A03 были получены следующие результаты.

— Отличий в декодере не обнаружено

— Флаг D работает как обычно, его можно установить или сбросить, он используется нормальным образом при обработке прерываний (сохраняется в стеке) и после выполнения инструкций PHP/PLP, RTI.

— Рандомная логика отвечающая за генерацию двух контрольных линий DAA (decimal addition adjust) и DSA (decimal subtraction adjust) работает обычным образом.

Отличие заключается в том, что контрольные линии DAA и DSA, отвечающие за включение схем коррекции, отсоединены от схемы, путём вырезания 5 кусочков полисиликона (см. картинку). полисиликон обозначен фиолетовым цветом, вырезанные кусочки обозначены голубым, а места обведены красным.

Это приводит к тому, что схема вычилсения десятичного переноса при сложении и схема добавления/отнимания 6 к результату — не работают. Поэтому встроенный процессор 2A03 всегда считает двоичными числами, даже если флаг D установлен.

After detailed study of 2A03 circuit following results were obtained:

— No differences were found in the instruction decoder

— Flag D works as expected, it can be set or reset by CLD/SED instructions; it is used in the normal way during interrupt processing (saved on stack) and after execution of PHP/PLP, RTI instructions.

— Random logic, responsible for generating the two control lines DAA (decimal addition adjust) and DSA (decimal subtraction adjust) works normally.

The difference lies in the fact that the control lines DAA and DSA, which enable decimal correction, are disconnected from the circuit, by cutting 5 pieces of polysilicon (see picture). Polysilicon marked as purple, missing pieces marked as cyan.

As result decimal carry circuit and decimal-correction adders do not work.

Therefore, the embedded processor of 2A03 always considers add/sub operands as binary numbers, even if the D flag is set.

2013-02-13 — Как происходит исполнение инструкций 6502

Как происходит исполнение инструкций 6502.

1. Из входного тактового импульса PHI0 получаются два полутактовых импульса: PHI1 и PHI2

2. На защелки /NMI, /IRQ, /RES подаются входные значения

3. Обработка RDY и сдвигового регистра RDY для Branch T0

4. На декодер подаются текущие значения T и IR

На декодер подаются текущие значения T и IR

5. На основе выходных линий с декодера, управляющих линий с Predecode-логики, сигнала RDY, флагов(+контакта SO) и логики прерываний генерируются управляющие сигналы для нижней части процессора

6. Работает нижняя часть процессора (X,Y,S,АЛУ,PC,шины)

7. Изменяются флаги, на основе результатов работы нижней части

8. При необходимости IR загружается новым значением или обновляется T, для обработки следующего цикла инструкции.

2013-02-04 — Разобрана схема ALU 6502

Полностью разобрана и симулирована схема ALU. Отчет размещал на 6502.org, поэтому на английском. Копирую сюда для истории 🙂

Hello, today I finally completed ALU.

I wrote some documentation on it, and made some tests for decimal mode. You can find it below.

ALU internals

ALU Inputs:

I/ADDC : input carry (inverted)

/DAA, /DSA : used for decimal correction:

for ADC /DAA=0,/DSA=1; for SBC /DAA=1,/DSA=0. B

B

SUMS: A + B + carry

SRS : shift right to 1

Output controls:

— from adder hold register:

ADD/SB06 : adder hold[0-6] -> SB[0-6]

ADD/SB7 : adder hold[7] -> SB[7]

ADD/ADL : adder hold -> ADL

— from accumulator:

AC/SB : accumulator -> special bus

AC/DB : accumulator -> data bus

SB/DB : special bus = data bus

Internal registers:

ADD : adder hold register for intermediate result (before decimal correction).

Also can be used for address calculation.

AC : accumulator. Hold final add/subtract result, after optional decimal correction.

Random notes and facts:

— ALU has inverted carry chain between odd/even bits, to reduce propagation delay.

— ALU write intermediate result to adder hold register (ADD) during PHI2, and updating accumulator (AC) at same time.

Final result placed on acumulator only on following PHI1 half-cycle.

This is need to make sure no conflicts happen, during refreshing of AC register. carry.

carry.

— Decimal correction is actually +6

To add A + B, do the following:

— put A on special bus (SB)

— put B on data bus (DB)

— optionally set input carry

— wait dummy PHI1 half-cycle

— if you need to add in decimal mode, set /DAA = 0, /DSA = 1.

— perform commands on next PHI2 : SB/ADD, DB/ADD, SUMS

— perform commands on next PHI1 : ADD/SB06, ADD/SB7, SB/AC

— get result from accumulator (AC)

To subtract A — B, do the following:

— put A on special bus (SB)

— put B on data bus (DB)

— force to set input carry

— wait dummy PHI1 half-cycle

— if you need to subtract in decimal mode, set /DAA = 1, /DSA = 0.

— perform commands on next PHI2 : SB/ADD, NDB/ADD (- perform commands on next PHI1 : ADD/SB06, ADD/SB7, SB/AC

— get result from accumulator (AC)

So basically A — B = A + NOT(B) + 1

ALU pipeline :

— load input registers (AI and BI)

— ORS, ANDS, SRS: perform logic operations, based on NAND and NOR

— EORS: perform exclusive-OR, based on NAND/NOR

— SUMS: calculate sum of two operands based on XOR and additional XOR it with carry

— DAA: calculate decimal carry and half-carry on-the-fly

— hold intermediate result in ADD register

— set output carry and overflow flags

— output carry is set whenever binary carry or decimal carry happens

— DSA: perform decimal adjustment (+6) to intermediate result and put it on accumulator

ALU circuit

Nicely cleaned and correct.

ALU Simulation

You can find it on Google code : http://code.google.com/p/breaks/source/ … 6502/ALU.c

Decimal mode tests

ALU tests in decimal mode, based on :

http://visual6502.org/wiki/index.php?ti … ecimalMode

ADC: AI + BI + Carry = AC, V out, C out

79 + 00 + 1 = 80, V:1, C:0

24 + 56 + 0 = 80, V:1, C:0

93 + 82 + 0 = 75, V:1, C:1

89 + 76 + 0 = 65, V:0, C:1 !!! result!

89 + 76 + 1 = 66, V:0, C:1 !!! result!

80 + F0 + 0 = D0, V:1, C:1

80 + FA + 0 = E0, V:1, C:1 !!! V-flag

2F + 4F + 0 = 74, V:0, C:0

6F + 00 + 1 = 76, V:0, C:0

SBC: AI + !BI + Carry = AC, V out, C out

00 — 00 + 0 = 99, V:0, C:0

00 — 00 + 1 = 00, V:0, C:1

00 — 01 + 1 = 99, V:0, C:0

0A — 00 + 1 = 0A, V:0, C:1

0B — 00 + 0 = 0A, V:0, C:1

9A — 00 + 1 = 9A, V:1, C:1 !!! V-flag

9B — 00 + 0 = 9A, V:1, C:1 !!! V-flag

By !!! I marked some differencies. Looks like Visual6502 has some problems in decimal mode. Because if you look, for example on 89 + 76, it should be 0x165 (0x65 + carry), but Visual6502 somehow has 0x55 as a result, which is incorrect of couse.

Because if you look, for example on 89 + 76, it should be 0x165 (0x65 + carry), but Visual6502 somehow has 0x55 as a result, which is incorrect of couse.

Additional reading

US Patent 3991307 : http://www.google.com/patents/US3991307

Its really nothing to say anything else, its done

2013-01-25 — Серия стримов по изучению 6502

Начинаю серию стримов по изучению процессора 6502:

Пока получается не очень интересно, потому что мне трудно «уцепиться» за схему из-за её непомерной сложности. Но разум не отступает перед машинами и человечество обязательно победит! На канале Youtube уже находится почти 40 часов стримов.

В итоге немного улучшил схему 6502:

PS. Обновленный PSD 6502 можно скачать в соответствующем разделе.

2013-01-17 — Первый опыт выхода в эфир

Продолжаем разработки после новогдних праздников 🙂

Первая новость: я решил попробовать демонстрировать процесс разработки в прямом эфире, в стриме на Youtube. Вот что получилось:

Пока что выхожу в эфир каждый вечер примерно в 21:00 по мск.

Вторая новость : выложил все исходные PSD на PPU:

Скачать все файлы можно в соответствующем разделе. Enjoy!

2012-11-26 — Эмуляция 6502 практически завершена (ухаха.. а уже почти 2019)

Эмуляция 6502 практически завершена. Осталось доделать всего несколько блоков рандомной логики и можно начинать тестирование на ошибки.

Осталось доделать всего несколько блоков рандомной логики и можно начинать тестирование на ошибки.

Немного статистики:

| Объем исходных данных (микрофотографии, топологическая схема) | 215 MB |

| Объем полученной документации (текст и схемы) | 45 MB |

| Объем исходного кода | ~60 KB (включая комментарии) |

| Скорость работы (без оптимизаций) | ~0.2 / 4 MIPS (5%) |

После завершения работ и тестирования ядра будет произведена массивная табличная оптимизация промежуточных состояний, для увеличения производительности.

В разделе «Скачать» появились исходные схемы 6502. Архив будет периодически обновляться.

2012-11-22 — Карта связей

Сделал карту связей (propagation map) для рандомной логики 6502:

Такого до меня ещё никто не делал для исследования чипов, поэтому я очень доволен своим изобретением 🙂 С помощью этой карты можно легко узнать в какой очередности работает тот или иной кусок.

Сегодня отличная пятничная ночка, чтобы заколотить косячок и разобраться как ведет себя 6502 в первые минуты жизни.

2012-11-22 — Оптимизация схемы 6502

Успехи в эмуляции H/V логики PPU подтолкнули меня к дальнейшему улучшению схемы 6502:

Из схемы были убраны все лишние провода, которых было просто невразумительно много, что очень усложняло понимание схемы. Также я расставил метки на динамические защелки (желтые гексагоны), aka SR-триггеры. В основном это биты регистра флагов, но есть ещё парочка вспомогательных.

Плюс как оказалось — выходные линии «драйверов» логики это тоже динамические защелки. Правда они очищаются когда PHI2=1.

Ну и параллельно обозначил большинство блоков рандомной логики. Теперь схема выглядит гораздо понятней 🙂

2012-11-16 — Симуляция логики H/V PPU

Вообщем победил логику работы H/V, результаты ниже.

Что интересного обнаружил:

— H тикает от 0 до 340 (всего 341 пиксель), V тикает от 0 до 261 (всего 262 строки).

— Счёт пикселей самой первой строки начинается с 1, потому что 0й пиксель на самом деле рендерится, начиная с H=329.

— Количество видимых пикселей 256, но размер «картинки» NTSC немного больше. Связано это с тем, что после видимых пикселей выводится так называемый «front porch» (черный край).

— PPU начинает работу непосредственно с рендеринга пикселей. После отображения видимых пикселей выводится вначале front porch, а потом back porch, которая включает в себя hblank и colorburst. Значения когда что начинается в H следующие:

0: не понятно, типа заглушки чтоли

1-256: видимые пиксели

257-279: front porch

271-328: back porch (как видно у них происходит пересечение)

280-304: hblank

309-323: color burst

329-340: начало выборки и рендеринга 0го пиксела следующей строки

Напоминаю структуру композитного NTSC-сигнала:

Чуть позже выложу табличку с командами H/V логики остальному чипу, для каждого значения H.

— 16 ноя 2012, 14:22 —

Немного пояснений:

H/V — текущие значения счетчиков

далее идут названия команд H/V — это те самые контрольные линии, которые расползаются по всему чипу и управ. Расшифровка команд после таблицы.

Самая первая строка:

H:1 V:0 I/OAM2 F/NT VIS PICTURE

H:2 V:0 I/OAM2 F/NT VIS PICTURE

H:3 V:0 I/OAM2 F/AT VIS PICTURE

H:4 V:0 I/OAM2 F/AT VIS PICTURE

H:5 V:0 I/OAM2 F/TA VIS PICTURE

H:6 V:0 I/OAM2 F/TA VIS PICTURE

H:7 V:0 I/OAM2 F/TB VIS PICTURE

H:8 V:0 I/OAM2 F/TB VIS PICTURE

H:9 V:0 I/OAM2 F/NT VIS PICTURE

H:10 V:0 I/OAM2 F/NT VIS PICTURE

H:11 V:0 I/OAM2 F/AT VIS PICTURE

H:12 V:0 I/OAM2 F/AT VIS PICTURE

H:13 V:0 I/OAM2 F/TA VIS PICTURE

H:14 V:0 I/OAM2 F/TA VIS PICTURE

H:15 V:0 I/OAM2 F/TB VIS PICTURE

H:16 V:0 I/OAM2 F/TB VIS PICTURE

H:17 V:0 I/OAM2 F/NT VIS PICTURE

H:18 V:0 I/OAM2 F/NT VIS PICTURE

H:19 V:0 I/OAM2 F/AT VIS PICTURE

H:20 V:0 I/OAM2 F/AT VIS PICTURE

H:21 V:0 I/OAM2 F/TA VIS PICTURE

H:22 V:0 I/OAM2 F/TA VIS PICTURE

H:23 V:0 I/OAM2 F/TB VIS PICTURE

H:24 V:0 I/OAM2 F/TB VIS PICTURE

H:25 V:0 I/OAM2 F/NT VIS PICTURE

H:26 V:0 I/OAM2 F/NT VIS PICTURE

H:27 V:0 I/OAM2 F/AT VIS PICTURE

H:28 V:0 I/OAM2 F/AT VIS PICTURE

H:29 V:0 I/OAM2 F/TA VIS PICTURE

H:30 V:0 I/OAM2 F/TA VIS PICTURE

H:31 V:0 I/OAM2 F/TB VIS PICTURE

H:32 V:0 I/OAM2 F/TB VIS PICTURE

H:33 V:0 I/OAM2 F/NT VIS PICTURE

H:34 V:0 I/OAM2 F/NT VIS PICTURE

H:35 V:0 I/OAM2 F/AT VIS PICTURE

H:36 V:0 I/OAM2 F/AT VIS PICTURE

H:37 V:0 I/OAM2 F/TA VIS PICTURE

H:38 V:0 I/OAM2 F/TA VIS PICTURE

H:39 V:0 I/OAM2 F/TB VIS PICTURE

H:40 V:0 I/OAM2 F/TB VIS PICTURE

H:41 V:0 I/OAM2 F/NT VIS PICTURE

H:42 V:0 I/OAM2 F/NT VIS PICTURE

H:43 V:0 I/OAM2 F/AT VIS PICTURE

H:44 V:0 I/OAM2 F/AT VIS PICTURE

H:45 V:0 I/OAM2 F/TA VIS PICTURE

H:46 V:0 I/OAM2 F/TA VIS PICTURE

H:47 V:0 I/OAM2 F/TB VIS PICTURE

H:48 V:0 I/OAM2 F/TB VIS PICTURE

H:49 V:0 I/OAM2 F/NT VIS PICTURE

H:50 V:0 I/OAM2 F/NT VIS PICTURE

H:51 V:0 I/OAM2 F/AT VIS PICTURE

H:52 V:0 I/OAM2 F/AT VIS PICTURE

H:53 V:0 I/OAM2 F/TA VIS PICTURE

H:54 V:0 I/OAM2 F/TA VIS PICTURE

H:55 V:0 I/OAM2 F/TB VIS PICTURE

H:56 V:0 I/OAM2 F/TB VIS PICTURE

H:57 V:0 I/OAM2 F/NT VIS PICTURE

H:58 V:0 I/OAM2 F/NT VIS PICTURE

H:59 V:0 I/OAM2 F/AT VIS PICTURE

H:60 V:0 I/OAM2 F/AT VIS PICTURE

H:61 V:0 I/OAM2 F/TA VIS PICTURE

H:62 V:0 I/OAM2 F/TA VIS PICTURE

H:63 V:0 I/OAM2 F/TB VIS PICTURE

H:64 V:0 EVAL I/OAM2 F/TB VIS PICTURE

H:65 V:0 F/NT VIS PICTURE

H:66 V:0 S/EV F/NT VIS PICTURE

H:67 V:0 F/AT VIS PICTURE

H:68 V:0 F/AT VIS PICTURE

H:69 V:0 F/TA VIS PICTURE

H:70 V:0 F/TA VIS PICTURE

H:71 V:0 F/TB VIS PICTURE

H:72 V:0 F/TB VIS PICTURE

H:73 V:0 F/NT VIS PICTURE

H:74 V:0 F/NT VIS PICTURE

H:75 V:0 F/AT VIS PICTURE

H:76 V:0 F/AT VIS PICTURE

H:77 V:0 F/TA VIS PICTURE

H:78 V:0 F/TA VIS PICTURE

H:79 V:0 F/TB VIS PICTURE

H:80 V:0 F/TB VIS PICTURE

H:81 V:0 F/NT VIS PICTURE

H:82 V:0 F/NT VIS PICTURE

H:83 V:0 F/AT VIS PICTURE

H:84 V:0 F/AT VIS PICTURE

H:85 V:0 F/TA VIS PICTURE

H:86 V:0 F/TA VIS PICTURE

H:87 V:0 F/TB VIS PICTURE

H:88 V:0 F/TB VIS PICTURE

H:89 V:0 F/NT VIS PICTURE

H:90 V:0 F/NT VIS PICTURE

H:91 V:0 F/AT VIS PICTURE

H:92 V:0 F/AT VIS PICTURE

H:93 V:0 F/TA VIS PICTURE

H:94 V:0 F/TA VIS PICTURE

H:95 V:0 F/TB VIS PICTURE

H:96 V:0 F/TB VIS PICTURE

H:97 V:0 F/NT VIS PICTURE

H:98 V:0 F/NT VIS PICTURE

H:99 V:0 F/AT VIS PICTURE

H:100 V:0 F/AT VIS PICTURE

H:101 V:0 F/TA VIS PICTURE

H:102 V:0 F/TA VIS PICTURE

H:103 V:0 F/TB VIS PICTURE

H:104 V:0 F/TB VIS PICTURE

H:105 V:0 F/NT VIS PICTURE

H:106 V:0 F/NT VIS PICTURE

H:107 V:0 F/AT VIS PICTURE

H:108 V:0 F/AT VIS PICTURE

H:109 V:0 F/TA VIS PICTURE

H:110 V:0 F/TA VIS PICTURE

H:111 V:0 F/TB VIS PICTURE

H:112 V:0 F/TB VIS PICTURE

H:113 V:0 F/NT VIS PICTURE

H:114 V:0 F/NT VIS PICTURE

H:115 V:0 F/AT VIS PICTURE

H:116 V:0 F/AT VIS PICTURE

H:117 V:0 F/TA VIS PICTURE

H:118 V:0 F/TA VIS PICTURE

H:119 V:0 F/TB VIS PICTURE

H:120 V:0 F/TB VIS PICTURE

H:121 V:0 F/NT VIS PICTURE

H:122 V:0 F/NT VIS PICTURE

H:123 V:0 F/AT VIS PICTURE

H:124 V:0 F/AT VIS PICTURE

H:125 V:0 F/TA VIS PICTURE

H:126 V:0 F/TA VIS PICTURE

H:127 V:0 F/TB VIS PICTURE

H:128 V:0 F/TB VIS PICTURE

H:129 V:0 F/NT VIS PICTURE

H:130 V:0 F/NT VIS PICTURE

H:131 V:0 F/AT VIS PICTURE

H:132 V:0 F/AT VIS PICTURE

H:133 V:0 F/TA VIS PICTURE

H:134 V:0 F/TA VIS PICTURE

H:135 V:0 F/TB VIS PICTURE

H:136 V:0 F/TB VIS PICTURE

H:137 V:0 F/NT VIS PICTURE

H:138 V:0 F/NT VIS PICTURE

H:139 V:0 F/AT VIS PICTURE

H:140 V:0 F/AT VIS PICTURE

H:141 V:0 F/TA VIS PICTURE

H:142 V:0 F/TA VIS PICTURE

H:143 V:0 F/TB VIS PICTURE

H:144 V:0 F/TB VIS PICTURE

H:145 V:0 F/NT VIS PICTURE

H:146 V:0 F/NT VIS PICTURE

H:147 V:0 F/AT VIS PICTURE

H:148 V:0 F/AT VIS PICTURE

H:149 V:0 F/TA VIS PICTURE

H:150 V:0 F/TA VIS PICTURE

H:151 V:0 F/TB VIS PICTURE

H:152 V:0 F/TB VIS PICTURE

H:153 V:0 F/NT VIS PICTURE

H:154 V:0 F/NT VIS PICTURE

H:155 V:0 F/AT VIS PICTURE

H:156 V:0 F/AT VIS PICTURE

H:157 V:0 F/TA VIS PICTURE

H:158 V:0 F/TA VIS PICTURE

H:159 V:0 F/TB VIS PICTURE

H:160 V:0 F/TB VIS PICTURE

H:161 V:0 F/NT VIS PICTURE

H:162 V:0 F/NT VIS PICTURE

H:163 V:0 F/AT VIS PICTURE

H:164 V:0 F/AT VIS PICTURE

H:165 V:0 F/TA VIS PICTURE

H:166 V:0 F/TA VIS PICTURE

H:167 V:0 F/TB VIS PICTURE

H:168 V:0 F/TB VIS PICTURE

H:169 V:0 F/NT VIS PICTURE

H:170 V:0 F/NT VIS PICTURE

H:171 V:0 F/AT VIS PICTURE

H:172 V:0 F/AT VIS PICTURE

H:173 V:0 F/TA VIS PICTURE

H:174 V:0 F/TA VIS PICTURE

H:175 V:0 F/TB VIS PICTURE

H:176 V:0 F/TB VIS PICTURE

H:177 V:0 F/NT VIS PICTURE

H:178 V:0 F/NT VIS PICTURE

H:179 V:0 F/AT VIS PICTURE

H:180 V:0 F/AT VIS PICTURE

H:181 V:0 F/TA VIS PICTURE

H:182 V:0 F/TA VIS PICTURE

H:183 V:0 F/TB VIS PICTURE

H:184 V:0 F/TB VIS PICTURE

H:185 V:0 F/NT VIS PICTURE

H:186 V:0 F/NT VIS PICTURE

H:187 V:0 F/AT VIS PICTURE

H:188 V:0 F/AT VIS PICTURE

H:189 V:0 F/TA VIS PICTURE

H:190 V:0 F/TA VIS PICTURE

H:191 V:0 F/TB VIS PICTURE

H:192 V:0 F/TB VIS PICTURE

H:193 V:0 F/NT VIS PICTURE

H:194 V:0 F/NT VIS PICTURE

H:195 V:0 F/AT VIS PICTURE

H:196 V:0 F/AT VIS PICTURE

H:197 V:0 F/TA VIS PICTURE

H:198 V:0 F/TA VIS PICTURE

H:199 V:0 F/TB VIS PICTURE

H:200 V:0 F/TB VIS PICTURE

H:201 V:0 F/NT VIS PICTURE

H:202 V:0 F/NT VIS PICTURE

H:203 V:0 F/AT VIS PICTURE

H:204 V:0 F/AT VIS PICTURE

H:205 V:0 F/TA VIS PICTURE

H:206 V:0 F/TA VIS PICTURE

H:207 V:0 F/TB VIS PICTURE

H:208 V:0 F/TB VIS PICTURE

H:209 V:0 F/NT VIS PICTURE

H:210 V:0 F/NT VIS PICTURE

H:211 V:0 F/AT VIS PICTURE

H:212 V:0 F/AT VIS PICTURE

H:213 V:0 F/TA VIS PICTURE

H:214 V:0 F/TA VIS PICTURE

H:215 V:0 F/TB VIS PICTURE

H:216 V:0 F/TB VIS PICTURE

H:217 V:0 F/NT VIS PICTURE

H:218 V:0 F/NT VIS PICTURE

H:219 V:0 F/AT VIS PICTURE

H:220 V:0 F/AT VIS PICTURE

H:221 V:0 F/TA VIS PICTURE

H:222 V:0 F/TA VIS PICTURE

H:223 V:0 F/TB VIS PICTURE

H:224 V:0 F/TB VIS PICTURE

H:225 V:0 F/NT VIS PICTURE

H:226 V:0 F/NT VIS PICTURE

H:227 V:0 F/AT VIS PICTURE

H:228 V:0 F/AT VIS PICTURE

H:229 V:0 F/TA VIS PICTURE

H:230 V:0 F/TA VIS PICTURE

H:231 V:0 F/TB VIS PICTURE

H:232 V:0 F/TB VIS PICTURE

H:233 V:0 F/NT VIS PICTURE

H:234 V:0 F/NT VIS PICTURE

H:235 V:0 F/AT VIS PICTURE

H:236 V:0 F/AT VIS PICTURE

H:237 V:0 F/TA VIS PICTURE

H:238 V:0 F/TA VIS PICTURE

H:239 V:0 F/TB VIS PICTURE

H:240 V:0 F/TB VIS PICTURE

H:241 V:0 F/NT VIS PICTURE

H:242 V:0 F/NT VIS PICTURE

H:243 V:0 F/AT VIS PICTURE

H:244 V:0 F/AT VIS PICTURE

H:245 V:0 F/TA VIS PICTURE

H:246 V:0 F/TA VIS PICTURE

H:247 V:0 F/TB VIS PICTURE

H:248 V:0 F/TB VIS PICTURE

H:249 V:0 F/NT VIS PICTURE

H:250 V:0 F/NT VIS PICTURE

H:251 V:0 F/AT VIS PICTURE

H:252 V:0 F/AT VIS PICTURE

H:253 V:0 F/TA VIS PICTURE

H:254 V:0 F/TA VIS PICTURE

H:255 V:0 F/TB VIS PICTURE

H:256 V:0 E/EV EVAL F/TB VIS PICTURE

H:257 V:0 F/NT PAR/O /FO PICTURE SYNC FRPORCH

H:258 V:0 F/NT PAR/O /FO PICTURE SYNC FRPORCH

H:259 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:260 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:261 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:262 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:263 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:264 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:265 V:0 F/NT PAR/O /FO PICTURE SYNC FRPORCH

H:266 V:0 F/NT PAR/O /FO PICTURE SYNC FRPORCH

H:267 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:268 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:269 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:270 V:0 PAR/O /FO PICTURE SYNC FRPORCH

H:271 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:272 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:273 V:0 F/NT PAR/O /FO SYNC FRPORCH BKPORCH

H:274 V:0 F/NT PAR/O /FO SYNC FRPORCH BKPORCH

H:275 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:276 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:277 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:278 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:279 V:0 PAR/O /FO SYNC FRPORCH BKPORCH

H:280 V:0 SC/CNT PAR/O /FO BKPORCH

H:281 V:0 SC/CNT F/NT PAR/O /FO BKPORCH

H:282 V:0 SC/CNT F/NT PAR/O /FO BKPORCH

H:283 V:0 SC/CNT PAR/O /FO BKPORCH

H:284 V:0 SC/CNT PAR/O /FO BKPORCH

H:285 V:0 SC/CNT PAR/O /FO BKPORCH

H:286 V:0 SC/CNT PAR/O /FO BKPORCH

H:287 V:0 SC/CNT PAR/O /FO BKPORCH

H:288 V:0 SC/CNT PAR/O /FO BKPORCH

H:289 V:0 SC/CNT F/NT PAR/O /FO BKPORCH

H:290 V:0 SC/CNT F/NT PAR/O /FO BKPORCH

H:291 V:0 SC/CNT PAR/O /FO BKPORCH

H:292 V:0 SC/CNT PAR/O /FO BKPORCH

H:293 V:0 SC/CNT PAR/O /FO BKPORCH

H:294 V:0 SC/CNT PAR/O /FO BKPORCH

H:295 V:0 SC/CNT PAR/O /FO BKPORCH

H:296 V:0 SC/CNT PAR/O /FO BKPORCH

H:297 V:0 SC/CNT F/NT PAR/O /FO BKPORCH

H:298 V:0 SC/CNT F/NT PAR/O /FO BKPORCH

H:299 V:0 SC/CNT PAR/O /FO BKPORCH

H:300 V:0 SC/CNT PAR/O /FO BKPORCH

H:301 V:0 SC/CNT PAR/O /FO BKPORCH

H:302 V:0 SC/CNT PAR/O /FO BKPORCH

H:303 V:0 SC/CNT PAR/O /FO BKPORCH

H:304 V:0 SC/CNT PAR/O /FO BKPORCH

H:305 V:0 F/NT PAR/O /FO BKPORCH

H:306 V:0 F/NT PAR/O /FO BKPORCH

H:307 V:0 PAR/O /FO BKPORCH

H:308 V:0 PAR/O /FO BKPORCH

H:309 V:0 PAR/O /FO BKPORCH BURST

H:310 V:0 PAR/O /FO BKPORCH BURST

H:311 V:0 PAR/O /FO BKPORCH BURST

H:312 V:0 PAR/O /FO BKPORCH BURST

H:313 V:0 F/NT PAR/O /FO BKPORCH BURST

H:314 V:0 F/NT PAR/O /FO BKPORCH BURST

H:315 V:0 PAR/O /FO BKPORCH BURST

H:316 V:0 PAR/O /FO BKPORCH BURST

H:317 V:0 PAR/O /FO BKPORCH BURST

H:318 V:0 PAR/O /FO BKPORCH BURST

H:319 V:0 PAR/O /FO BKPORCH BURST

H:320 V:0 PAR/O /FO BKPORCH BURST

H:321 V:0 F/NT BKPORCH BURST

H:322 V:0 F/NT BKPORCH BURST

H:323 V:0 F/AT BKPORCH BURST

H:324 V:0 F/AT BKPORCH

H:325 V:0 F/TA BKPORCH

H:326 V:0 F/TA BKPORCH

H:327 V:0 F/TB BKPORCH

H:328 V:0 F/TB BKPORCH

H:329 V:0 F/NT PICTURE

H:330 V:0 F/NT PICTURE

H:331 V:0 F/AT PICTURE

H:332 V:0 F/AT PICTURE

H:333 V:0 F/TA PICTURE

H:334 V:0 F/TA PICTURE

H:335 V:0 F/TB PICTURE

H:336 V:0 F/TB PICTURE

H:337 V:0 0/HPOS EVAL F/NT /FO PICTURE

H:338 V:0 0/HPOS EVAL F/NT /FO PICTURE

H:339 V:0 0/HPOS EVAL /FO PICTURE

H:340 V:0 0/HPOS EVAL /FO PICTURE

Остальные строки начинаются так:

H:0 V:1 /FO PICTURE

H:1 V:1 I/OAM2 F/NT VIS PICTURE

H:2 V:1 I/OAM2 F/NT VIS PICTURE

. … и дальше понеслась душа по кочкам

… и дальше понеслась душа по кочкам

Полный список команд H/V логики:

CLIP_O, CLIP_B: команды обрезания левых 8 пикселей бекгрануда / спрайтов (clipping)

0/HPOS: очистить счетчики H в спрайтовой FIFO (спрайтовая FIFO — это специальная схема, которая выдает наружу смешанный цвет 8 текущих спрайтов)

EVAL: сравнение спрайтов в процессе

PAR/O: выборка паттернов для спрайтов

VIS: PPU ренедерит видимые пиксели (НЕ относится к front porch)

BLNK: картинка не видна (vblank) или выключена контрольными регистрами

RESCL: сбросить reset flip/flop

S/EV, E/EV: точное значение пока не известно, но первая испольняется перед началом сравнения спрайтов, а вторая — вконце

I/OAM2: инициализировать дополнительную OAM (32 байта, которые используются для временного хранения 8 текущих спрайтов)

SC/CNT: обновить регистры скроллинга.

F/NT, F/AT, F/TA, F/TB, /FO: команды выборки данных из памяти. NT — name table, AT — attribute table, TA — tile #0, TB — tile #1, /FO — активна когда PPU выбирает паттерны для спрайтов

PICTURE, BURST, SYNC : команды управления видеотрактом

/BPORCH :back porch (внутренняя команда, наружу не идет)

/FPORCH :front porch (внутренняя команда, наружу не идет)

/INT: выход /INT (прерывание VBlank)

Таким образом H/V — это черный ящик, который в зависимости от текущего значения H и V выдает различные команды.

На вход к нему поступает минимальное количество управляющих линий:

— PPU control register bits: OBCLIP, BGCLIP (для упраления командами clippinga), BLACK (выключить отрисовку видимых пикселей), VBL (отключить генерацию /INT)

— /R2 and /DBE bus enablers (for DB7), для получения текущего состояния vblank (бит 7 регистра $2002)

Несколько слов о контрольной линии «BLACK».

— Эта линия активна только в том случае, когда выключены бекграунд И спрайты. То есть на экране вообще ничего нет.

— Команда BLNK (blank) — это на самом деле комбинация BLACK и VBLANK. То есть команда BLNK активна во время VBLANK (когда естественно на экране ничего нет), а также если картинка отключена полностью (BLACK=1)

BLNK влияет на работу PPU следующим образом:

— часть контрольных линий с H/V счетчиков просто отсекаются, в результате чего наружу не идут команды управления другими блоками, ответственными за отрисовку

— эта линия дополнительно разводится по остальным блокам и просто отключает их, для экономии электричества и энергии Вселенной.

Больше тут сказать особо нечего, можно двигаться дальше ) На очереди «безспрайтовый» PPU. То есть я ставлю задачу вывести задний фон, игнорируя все блоки, которые занимаются сравнением и наложением спрайтов.

Исходный код тут:

http://code.google.com/p/breaks/source/ … sPPU/PPU.c

2012-11-15 — Первые шаги в симуляции PPU

Сделал первые шаги в эмуляции PPU:

http://code.google.com/p/breaks/source/browse/trunk/BreaksPPU/PPU.c

Ну и ради интереса измерил производительность на том, что уже готово (это ориентировочно 15-20% чипа в виде Си кода). Производительность PPU условно можно считать 44 MIPS (CLK примерно 22 МГц), используются оба полутакта. Результаты: 0.8 — 1 MIPS %) Измерил также пустой цикл у своего процессора, получилось что-то около 60-70 MIPS. PPU при всей своей простоте оказался невероятно производительным.

Будем искать компромисс между идеальной точностью и конечным результатом. Например с точки зрения пользователя PPU дискретен на уровне рендеринга точек. То есть все более быстрые процессы (те которые 44 MIPS) протекают исключительно внутри самого PPU, а внешне скорость его взаимодействия гораздо меньше, точки рендерятся с частотой что-то около 5.5 Мгц, то есть в районе 5 MIPS.

Например с точки зрения пользователя PPU дискретен на уровне рендеринга точек. То есть все более быстрые процессы (те которые 44 MIPS) протекают исключительно внутри самого PPU, а внешне скорость его взаимодействия гораздо меньше, точки рендерятся с частотой что-то около 5.5 Мгц, то есть в районе 5 MIPS.

Поэтому не исключено что для хардварных гиков я оставлю максимально точную симуляцию, а для рядового пользователя (кем я себя тоже считаю), сделаю попиксельный или может быть даже построчный рендеринг. В конце концов — человеческий глаз не в состоянии заметить прорисовку не только отдельной строки PPU, но даже целого кадра. Не говоря уж о попиксельной растеризации 🙂

2012-11-14 — Улучшения схемы рендеринга PPU

Подчистил схемку PPU-рендерера (находится в верхнем левом углу):

В этой схеме находится самая интересная часть, «мозг» PPU : H/V random logic. По сложности он конечно уступает рандомной логике 6502, который сложнее примерно раз в 5. Но тем не менее, логика достаточно сложная, без транзисторной схемы я вообще не представляю как можно разобраться в хитросплетении этих кишочков )) А со схемой все гораздо понятнее.

Но тем не менее, логика достаточно сложная, без транзисторной схемы я вообще не представляю как можно разобраться в хитросплетении этих кишочков )) А со схемой все гораздо понятнее.

Все блоки идентифицированы, можно приступать к эмуляции чипа. Хотя нет, ещё остается та самая милипизерная схема, в самом низу чипа

Бонус: контакт /RES

В нем находится динамическая защелка (выделена желтым гексагоном), которая устанавливается при возникновении импулься сброса (/RES).

Контрольная линия — RC очищает все регистры PPU, пока защелка активна.

А специальная линия — REGCL очищает саму защелку. Это происходит в конце каждого кадра, после vblank. Скорее всего это что-то вроде отклика от PPU на сигнал сброса.

А также на днях закончил среднюю часть схемы, где происходит сравнение и выборка 8 текущих спрайтов:

2012-11-07 — Сшивание фоток стравленного PPU

Закончил сшивание полученных фоток стравленного PPU:

Полноразмерное фото и набор слайдов можно скачать в соответствующем разделе 🙂

2012-11-07 — OLD SCHOOL vs NEW SCHOOL

Пересилил свое отвращение к установке продуктов Microsoft и скачал Express 2012. Заманили тем что регистрация и ключик на среду бесплатный.

Заманили тем что регистрация и ключик на среду бесплатный.

Устанавливал где-то час + потребовалась перезагрузка, всё в лучших традициях. Однако размер установленной студии порадовал — 900 мб. Видимо остальные 4 Гб находятся в .NET framework 4.

А цель была не просто установить. Недавно у нас с Евгеном зашел разговор — насколько быстрым будет Breaks. Ведь например эмулятор DICE (симулирует работу рассыпухи аркадных понгов итп) тупит даже на 3 ггц машинах.

Несложные калькуляции : ядро 6502 работает в среднем на частоте 2 мгц. При этом работая полутактами (используя как положительные, так и отрицательные фронты CLK), оно производит примерно 4 миллиона операций в секунду, то бишь условно 4 MIPS.

Мне стало интересно — сможет мое ядро 6502 выдавать заветные 4 MIPS (а ведь нужно ещё оставить процессорного времени на эмуляцию APU/PPU, ТВ-вывод и пр.)

Поэтому я взял и замерил сколько тактов эмуляции в секунду делает ядро Breaks 6502. Результаты конечно весьма печальные: на моем средненьком Intel Dual Core T4500 2 ггц компиляция с помощью lcc выдает примерно 80.000 операций/сек (0.08 MIPS), то есть в 50 раз медленнее чем необходимо 🙁

Поэтому стало интересно какие цифры получатся в новой Express 2012. В 4 часа утра я наконец умудрился скомпилировать проект и результаты следующие: примерно 220.000 оп/сек (0.2 MIPS). Уже лучше, но все равно в 20 раз медленнее.

Однако я не унываю, потому что сейчас ядро не использует упаковку бит. Что это значит? А то, что если регистр имеет 8 бит, то ядро честно производит операцию над каждым битом в цикле от 1 до 8. Такие циклы используются повсеместно, что и замедляет работу ядра. Основные затраты по времени конечно-же отнимает эмуляция PLA- декодера, при которой каждый полутакт прогоняется огромный цикл на 120 операций. Всё это можно существенно оптимизировать, но вначале нужно добиться точной эмуляции.

Как говорили авторы UNIX и создатели языка си: «Вначале сделай чтобы это работало, а потом сделай чтобы это работало быстро» 🙂

2012-11-07 — Закончена трассировка PPU

Закончил трассировку PPU:

(картинки кликабельны, полноразмерные фотки примерно по 20 MB каждая)

Исходники фотошопа тут: http://breaknes.com/files/PPU/2C02G.zip (260 MB)

2012-11-07 — Запуск сайта

Сайт запущен. Дизайн взял из какого-то хранилища, на первое время сойдет.

Программа для моделирования схем электроники на русском. Qucs – простой и бесплатный симулятор электронных схем

Программа для электрических схем — это инструмент, используемый инженерами, для создания электронных схем с целью расчета и тестирования изделий на этапах проектирования, производства, а также эксплуатации. Точное отображение параметров производится при помощи масштаба. Каждый элемент имеет свое обозначение в виде символов, соответствующих ГОСТу.

Программа для электрических схем: зачем мне это нужно?

При помощи программы для электрических схем можно строить точные чертежи, а затем сохранять их в электронном виде или распечатывать.

ВАЖНО! Почти во всех программах для рисования схем есть готовые элементы в библиотеке, потому вручную их можно не чертить.

Такие программы бывают платными и бесплатными. Первые характеризуются большой функциональностью, их возможности значительно шире. Существуют даже целые автоматизированные системы проектирования САПР, которые успешно используются инженерами во всем мире. С применением программ для черчения схем работа не только полностью автоматизированная, а и предельно точная.

Бесплатные программы уступают по функциональным возможностям платному софту, однако с их помощью можно реализовать проекты начальной и средней сложности.

Программное обеспечение позволяет упростить работу и сделать ее более эффективной. Мы подготовили перечень популярных программ для создания схем, используемых специалистами во всем мире. Но для начала давайте разберемся, что собой представляют схемы и каких видов они бывают.

Программы: для каких схем предназначены?

Схема представляет собой конструкторский документ графического типа. На нем размещены в виде условных обозначений составляющие компоненты устройства и связи между ними.

Схемы являются частью комплекта конструкторской документации. В них содержатся данные, необходимые для проектирования, производства, сборки, регулирования, использования прибора.

Когда нужны схемы?

- Процесс проектирования. Они позволяют определить структуру разрабатываемого изделия.

- Процесс производства. Дают возможность продемонстрировать конструкцию. На их базе разрабатывается технологический процесс, способ монтажа и контроля.

- Процесс эксплуатации. При помощи схем можно определить причину поломки, правильный ремонт и техническое обслуживание.

Виды схем по ГОСТу:

- кинематические;

- газовые;

- энергетические;

- пневматические;

- гидравлические;

- электрические;

- комбинированные;

- оптические;

- деления;

- вакуумные.

В какой программе лучше работать?

Существует огромное количество платных и бесплатных программ для разработки электрических чертежей. Функционал у всех одинаковый, за исключением расширенных возможностей у платных.

Visio

QElectro Tech

sPlan

Visio

Плюсы QElectro Tech

- экспорт в формате png, jpg, bmp или svg;

- проверка работоспособности электрических цепей;

- легко создавать схемы электропроводки, благодаря наличию обширной библиотеки;полностью на русском языке.

Минусы QElectro Tech

- функционал ограниченный;

- создание схемы сети начальной и средней сложности.

Простой интерфейс. Коллекция фигур для сборки электрических схем располагается слева в главном окне. В правой стороне находится рабочая область.

- Создать новый документ.

- Перетащить при помощи мышки в рабочую область необходимое количество элементов для создания и симуляции желаемого результата.

- Соединить детали между собой. Соединения автоматически преобразуются в горизонтальные и вертикальные линии.

- Сохранить файл с расширением qet.

Есть функция постройки собственных элементов и сохранения в библиотеке. Фигуры можно использовать в других проектах. Софт на русском языке. Программа подходит для Linux и Windows.

sPlan

Программа для построения электронных и электрических схем, рисования плат. При переносе элементов из библиотеки их можно привязывать к сетке координат. Софт простой, но позволяет создавать чертежи и рисунки разной сложности.

Фото 3 — Процесс составления схемы в sPlan

Задача sPlan заключается в проектировании и разработке электронных принципиальных схем. Для упрощения работы разработчик предусмотрел обширную библиотеку с геометрическими заготовками обозначений электронных элементов. Есть функция создания элементов и сохранения их в библиотеке.

Этапы работы:

- Создать новый документ.

- Из библиотеки элементов перетащить необходимые. Фигуры можно группировать, поворачивать, копировать, вырезать, вставлять и удалять.

- Сохранить.

В данной статье будет представлено 20 лучших программ для проектирования электронных схем и печатных плат, включая бесплатные, коммерческие и условно бесплатные программы.

Изучение дизайна макетов или электронных диаграмм не сложно, если вы выберете правильный инструмент дизайна. Для создания списка был использован ряд критериев, таких как:

- качество программного обеспечения;

- удобство для пользователя;

- сложность среды проектирования.

Бесплатное программное обеспечение для рисования электронных схем:

Ниже будет представлен список и краткое описание бесплатных программ для проектирования электронных схем.

LTspice

Это программное обеспечение для моделирования от линейных технологий до разработки электронных схем, моделирования SPICE, диаграмм сигналов и многих других функций:

- многоязычный графический интерфейс MDI для открытия и редактирования нескольких файлов в сеансе;

- встроенный редактор схем с базой данных 2 тыс. электронных компонентов;

- симулятор аналоговых и смешанных схем с режимом импорта файлов SPICE;

- постпроцессор для генерации графических кривых результатов анализа и отчетов;

- возможность персонализировать настройки режима отображения и сочетания клавиш;

- удобные функции масштабирования окна просмотра, печати и копирования в буфер обмена;

- интегрированная база данных схем выборки LTSpice .ASC.

Узнать больше и скачать LTspice вы можете на нашем .

«Компас-электрик»

Замечательная графическая российская программа, которая является разновидностью программы «Компас». Используется в области электрики для создания схем электрооборудования различных механизмов. Программа имеет обширные возможности. Посредством программы «Компас-электрик» возможно начертить любую электрическую схему.

Программа «Компас-электрик» имеет три версии, различные по своему функционалу: экспресс версия, стандартная версия, профессиональная версия. Основными компонентами данной программы являются:

- База данных, которая является фундаментом для проектирования документации;

- Редактор схем и отчетов, в котором происходит сам процесс создания и выпуска готовой документации проектов.

DipTrace

Это программа для проектирования профессиональных печатных плат. Вполне интуитивно понятный интерфейс, огромная функциональность. Dip Trace поддерживает несколько режимов работы. В каждый пакет DipTrace входят следующие программы:

- редактор схем;

- программа проектирования контуров — компоновка печатной платы;

- редактор компонентов;

- редактор корпуса;

- автотрассировщик;

- 3D-визуализация;

- функция импорта библиотек и проектов из других программ EDA.

Скачать и получить более подробную информацию с обучающей книгой вы можете на нашем .

EasyEDA

Бесплатный и доступный в облачном инструменте EDA, позволяющий создавать схемы, моделировать SPICE и дизайн печатной платы. В его базе данных уже более 70 000 готовых диаграмм и более 15 тысяч библиотек PSpice, которые позволяют быстро рисовать диаграммы в веб браузере. Проекты, подготовленные в EasyEDA, могут быть опубликованы или сохранены в облаке. Файлы также можно экспортировать во многие форматы, включая JSON.

Программное обеспечение EasyEDA совместимо с инструментами Altium, Eagle KiCad и LTspice, откуда вы можете импортировать дополнительные библиотеки. По желанию производитель предлагает относительно недорогую конструкцию печатной платы в соответствии с созданной конструкцией. Благодаря доступу к приложениям в облаке мы получаем удобство, мобильность и совместимость между устройствами.

TinyCAD

Это программа для рисования схем в Windows, доступная для бесплатной загрузки с SourceForge. Поддерживает стандартные и пользовательские библиотеки символов. TinyCAD чаще всего используется для создания:

- однолинейных диаграмм;

- создания блок-схем;

- разработки технических чертежей для целей презентации.

Xcircuit

Бесплатная программа для рисования схем из Open Circuit Designs, разработанная для среды Unix / Linux, но вы можете использовать ее в Windows, если у вас есть работающий сервер или Windows API. Существует множество бесплатных версий.

Dia

Это базовый инструмент проектирования с возможностью рисования блок-диаграмм. Dia — программа для начинающих, только для людей, входящих в область рисования электронных схем. Программа имеет лицензию GPL и доступна в версиях Mac и Linux (без версии для Windows). Чаще всего используется для построения блок-схем.

Pspice — Student Version

Бесплатная версия программного обеспечения Pspice была создана для студентов. Он содержит ограниченные версии таких продуктов, как: PSpice A / D 9.1, PSpice Schematics 9.1, Capture 9.1. Позволяет разрабатывать и моделировать аналоговые и цифровые схемы.

SmartDraw

Программные шаблоны проектирования электро схем из SmartDraw LCC, считается одним из лучших САПРОВ для рисования электронных схем, блок-схем, HVAC, и т.д.

Бесплатная версия SmartDraw представляет собой усеченный вариант платного программного обеспечения, в котором отсутствует расширенные функции.

1-2-3 схема

Это простая программа редактор для создания электро схем, которая позволит вам быстро и просто создать, и начертить любую схему любого уровня сложности. В приложении вы имеете возможность создавать электро схемы щитков для жилищных комплексов, стоит заметить, что программа на русском языке, поэтому удобна в применении.

1-2-3 схема является одним из бесплатных приложений, которое позволяет укомплектовывать электрощиты Хагер (Hager) оборудованием того же производителя. Основной особенностью программы относится такая функция, как сам по себе выбор корпуса для электрощита, который отвечает всем требованиям и нормам безопасности. Выбор производится непосредственно из ряда моделей Hager.

Более подробную информацию о программе вы можете найти на нашем .

Microsoft Visio

Основной задачей программы является разработка и создание с помощью шаблонов рисование разного рода электронных схем. Программа имеет возможность создавать:

- разнообразные инженерные и технические рисунки;

- электронные схемы;

- составлять эффектные презентации;

- разрабатывать организационные схемы, маркетинговые и многие другие.

Кроме широких возможностей, программа имеет богатый набор готовых элементов, шаблоны visio для электро схем, а также библиотеку красивых объемных рисунков. Создание различных электронных схем не является единственной задачей для MS Visio.

KiCad

Это пакет с открытым исходным кодом, который был создан французом Жан-Пьером Шаррас. Данное программное обеспечение включает в себя ряд интегрированных независимых программ, таких как:

- kicad — приложение для управления проектами;

- EESchema — расширенный редактор схем, с помощью которого можно создавать иерархические структуры;

- Pcbnew — редактор для создания печатных плат на основе схемного дизайна;

- gerbview — средство для просмотра файлов gerber и многие другие.

KiCad совместим со многими ОС, так как основан на библиотеке wxWidgets.

Более подробную информацию вы можете найти на нашем .

CadSoft Eagle

Высококачественная программа для проектирования печатных плат от немецкой компании CadSoft, входящей в состав Premier Farnell plc. EAGLE является аббревиатурой для легко применимого графического редактора макетов, что означает простой в использовании графический редактор.

CadSoft Eagle завоевала большую популярность из-за простоты и возможности использовать одну из версий — Eagle Light бесплатно. Бесплатная версия программы не позволяет создавать электронные схемы в коммерческих целях.

Программа доступна для операционных систем Windows, Linux, OS X.

Платное программное обеспечение для рисования электронных схем:

Ниже представлен список и краткое описание платных программ для проектирования электронных схем.

OrCAD

Самая популярная программа компании Cadence, содержащая полную среду для коммерческих проектов PCB, содержит все компоненты, необходимые для проектирования печатных плат, такие как:

- модуль для введения схем;

- редактор печатных плат с интегрированным управлением проектирования.

Чтобы повысить эффективность дизайна, программа предлагает интерактивную технологию проводки Push & Shove.

TINA-TI

Недорогое решение от DesignSoft, созданное для предприятий и фрилансеров. Он позволяет создавать:

- схемы;

- компоновку компонентов;

- моделирование;

- множество дополнительных функций.

Примечательной особенностью является также тестирование систем в режиме реального времени.

Altera

Предоставляет полный набор инструментов программирования для каждого этапа проекта, включая программные обеспечения:

- NIOS II для проектирования встроенных систем;

- DSP Builder для проектирования цифровых систем обработки сигналов;

- Quartus II и ModelSim для построения логических систем.

Система Altera Max + Plus II (многоадресная матричная программируемая логическая пользовательская система) представляет собой интегрированную среду для проектирования цифровых схем в программируемых структурах. Система Max + Plus II включает 11 интегрированных прикладных программ.

Altium Designe

Комплект Altium Designer включает в себя четыре основных модуля:

- редактор схем;

- 3D- дизайн печатной платы;

- разработка программируемой вентильной матрицы (FPGA) и управление данными.

Как правило, Altium Designer является дорогим ПО, но отличается способностью добиваться быстрых результатов для сложных схем.

P-Cad

Это программа для создания печатных плат и электронных схем. В пакет P-CAD входят два основных компонента:

- P-CAD Schematic — редактор схем;

- P-CAD pcb — редактор печатных плат.

На протяжении долгого времени данной программой пользовалось огромное количество российских разработчиков электронных схем, главной причиной этой популярности стал достаточно интуитивно понятный и удобный интерфейс. На данный момент производитель прекратил поддержку данного ПО, заместив ее программой Altium Designer.

Proteus Design Suite

Это полное программное решение для моделирования схем и проектирования печатных плат. Он содержит несколько модулей для схемного захвата, прошивки IDE и компоновки печатных плат, которые отображаются в виде вкладок внутри единого интегрированного приложения. Это обеспечивает плавный рабочий процесс AGILE для инженера проектировщика и помогает продуктам быстрее выйти на рынок.

Пробная версия приложения имеет полный функционал, но не имеет возможности сохранения файлов.

sPlan

Простой в использовании инструмент, который зарекомендовал себя в области инженерии, ремесел, образования, исследований и обучения. Он также стал полезным инструментом для многих частных пользователей.

Создавайте профессиональные планы за очень короткое время, от простой схемы до сложных планов. Особенностями данной программы являются:

- расширяемая библиотека символов;

- индивидуальные страницы с листами форм;

- список компонентов;

- автоматическая нумерация компонентов;

- удобные инструменты рисования.

В бесплатной версии нельзя сохранять, экспортировать и печатать файлы.

Напишите в комментариях, какие программы для создания схем и дизайна электронных схем вы используете?

Этой статьей начинаю освещать одну из интереснейших тем это тема компьютерного, еще говорят, схемотехнического моделирования схем различных электронных устройств .

Вообще термин моделирование электронных схем имеет много синонимов, это и эмуляция электронных схем, симуляция электронных схем и т. д. Я буду придерживаться термина «компьютерное моделирование» или моделирование схем на компьютере, не суть важно.

Итак, поехали.

На сегодняшний день существуем множество компьютерных программ, которые предназначены в первую очередь для разработки различных электронных устройств и в таких программах существует одна из важных функций – эмуляция электрических схем.

Перечислю только самые известные из них: