RS-триггер от ZETLAB, компонент SCADA системы

Триггер — это электрическая схема, имеющая два устойчивых состояния, которые устанавливаются при подаче соответствующей комбинации сигналов на управляющие входы триггера и сохраняющиеся в течение заданного времени после окончания действия этих сигналов. Триггер — логическое устройство способное хранить 1 бит данных.

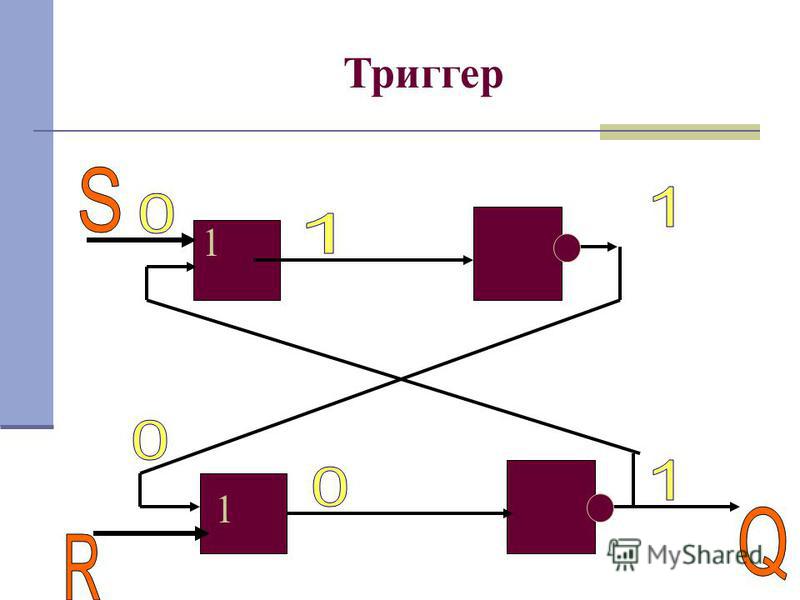

Рис.1

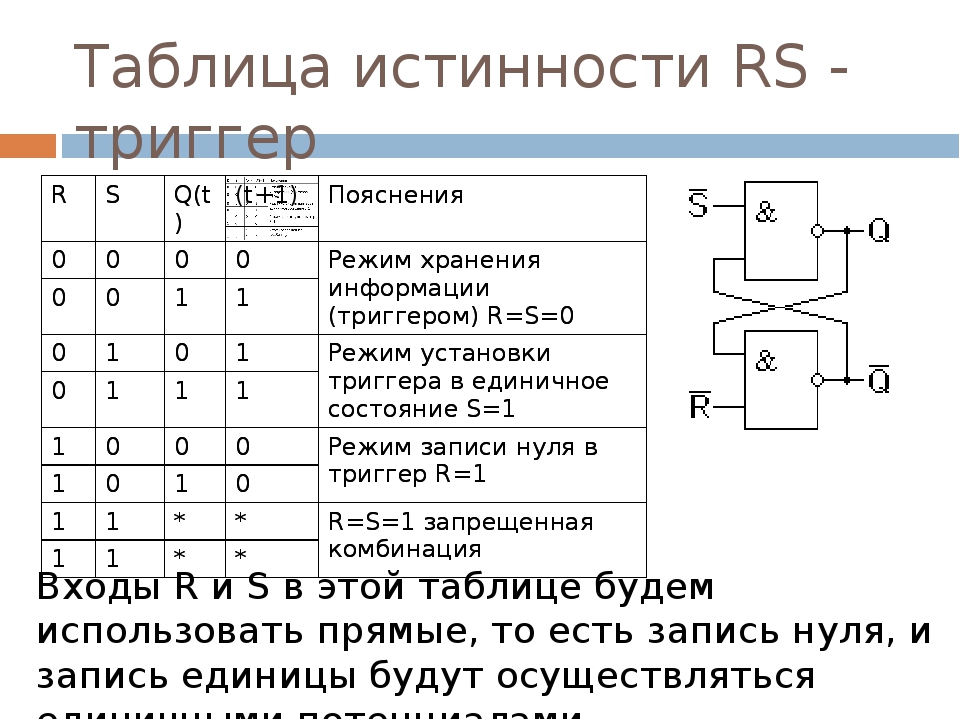

RS-триггер реализуется на основе двух инверторов с перекрестными обратными связями. RS-триггер, показаны на рис.1, состоит из двух элементов ИЛИ-НЕ. Входы триггера обозначаются S (Set — установка) и R (Reset — сброс). Его работа описывается следующей таблицей истинности:

| S | R | Q | ¬Q |

| 0 | 0 | Q-1 | ¬Q-1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

Q-1

При S=0, R=0 состояние триггера не меняется, этот режим называется режимом хранения информации. При S=R=1 оба выхода триггера должны равняться нулю, что логически невозможно, поэтому, поэтому такое состояние называется неопределенным или запрещенным, и таких ситуаций надо избегать. Режим S=1, R=0, является режимом записи логической единицы (режимом установки), а режим S=0, R=1 –режимом логического нуля (режимом сброса).

При S=R=1 оба выхода триггера должны равняться нулю, что логически невозможно, поэтому, поэтому такое состояние называется неопределенным или запрещенным, и таких ситуаций надо избегать. Режим S=1, R=0, является режимом записи логической единицы (режимом установки), а режим S=0, R=1 –режимом логического нуля (режимом сброса).

| ¬S | ¬R | Q | ¬Q |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | Q-1 | ¬Q-1 |

Q-1 – предыдущее состояние

Рис.2

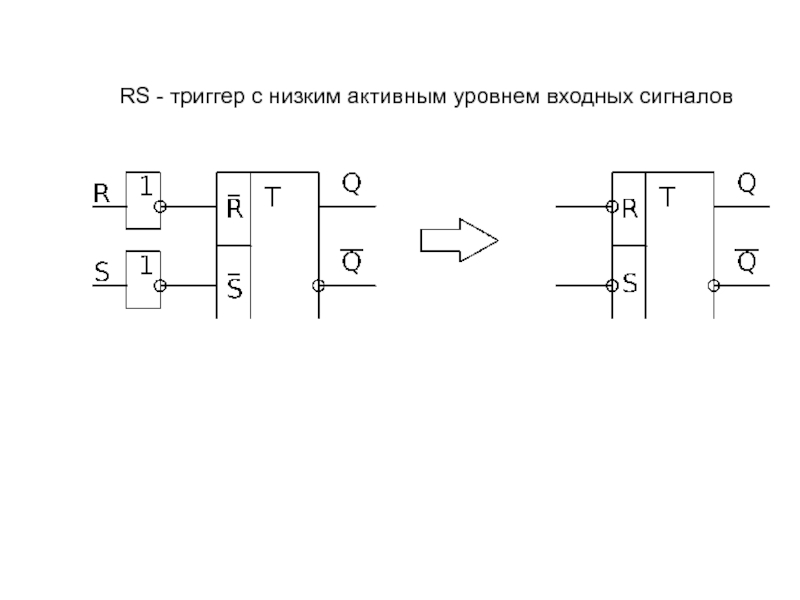

На рис.2 показан RS-триггер с инверсными входами, переключение состояний которого осуществляется сигналами низкого уровня. Для такого триггера таблица истинности имеет вид:

Рис.3

На Рис.3 показана модификация RS-триггера, называемая управляемым или синхронным RS-триггером. Такой триггер меняет свое состояние, только когда на вход синхронизации CLK подан сигнал высокого уровня. При сигнале на этом входе низкого уровня триггер сохраняет свое предыдущее состояние. Для управляемого RS-триггера характерна следующая таблица истинности.

Такой триггер меняет свое состояние, только когда на вход синхронизации CLK подан сигнал высокого уровня. При сигнале на этом входе низкого уровня триггер сохраняет свое предыдущее состояние. Для управляемого RS-триггера характерна следующая таблица истинности.

| CLK | S | R | Q | ¬Q | |

| 1 | 0 | 0 | Q-1 | ¬Q-1 | Как RS-триггер |

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | ? | ? | |

| 0 | X | X | Q-1 | ¬Q-1 | Режим хранения информации |

Очередной подход к RS-триггеру, теперь с TLA+ / Хабр

Я уже моделировал RS-триггер как полностью

синхронную схему. Но в некоторых приложениях таких моделей не достаточно, требуется рассмотреть переходные процессы, которые могут возникнуть. TLA+ разработан для анализа параллельных асинхронных систем. Поупражнявшись в

TLA+ разработан для анализа параллельных асинхронных систем. Поупражнявшись в

с его помощью, можно начать применять этот инструмент и для более серьезных задач.

RS-триггер состоит из двух рекурсивно связанных NOR-элементов (NOT OR). Для начала опишем отдельный NOR.

NOR(a,b,c) == c' = ~ (a \/ b)

Этот элемент связывает три точке в схеме, его действие устанавливает сигнал в точке c в следующий момент времени в NOT(OR(a,b)). Когда именно это произойдет мы пока не указываем.

Теперь объединим два NOR в один RS-триггер.

RS == (\/ (NOR(r, q, p) /\ UNCHANGED q)

\/ (NOR(p, s, q) /\ UNCHANGED p)

\/ (NOR(r, q, p) /\ NOR(p, s, q)))

/\ UNCHANGED <<r,s>>

Здесь явно описана асинхронная природа электронных схем. Может сработать один из двух NOR или оба сразу. При этом предполагаем, что входные сигналы r и s не изменяются.

RS-триггер работает корректно, если не подавать ему на вход оба сигнала r и s равными TRUE.

Change == /\ p = ~ (r \/ q)

/\ q = ~ (p \/ s)

/\ IF r = FALSE /\ s = FALSE

THEN \/ (r' = TRUE /\ s' = FALSE)

\/ (r' = FALSE /\ s' = TRUE)

ELSE r' = FALSE /\ s' = FALSE

/\ UNCHANGED <<p,q>>

Что бы проверить, что установившееся состояние триггера соответствует выполняемой операции введем вспомогательные переменные, в которых будем хранить значения сигналов перед изменениями.

Check == /\ oldp' = p

/\ oldq' = q

/\ stable' = (r = FALSE /\ s = FALSE)

Теперь можно сформулировать предикат перехода.

Next == Check /\ (RS \/ Change)

Кроме корректности установившегося состояния триггера будем проверять так же непротиворечивость выходов в промежуточном состоянии — что оба выхода не могут одновременно принимать значение TRUE (в частности это означает, что мы имеем право передавать выходы одного триггера на другой).

OutputOk == p /= TRUE \/ q /= TRUE

И полный инвариант

Invariant == /\ (r = FALSE \/ s = FALSE)

/\ (stable => oldq = q /\ oldp = p)

/\ OutputOk

Еще одно хорошее свойство, которое, однако, не может быть записано в инварианте — что переходные процессы в триггере рано или поздно завершаться.

RSok == /\ [] (r = TRUE ~> q = TRUE)

/\ [] (s = TRUE ~> p = TRUE)

«

r ~> q» — синтаксический сахар для «

r => <> q«.

«

=>» — логический оператор «следует».

«

<>» — темпоральный оператор «когда-нибудь».

«

[]» — темпоральный оператор «всегда».

Темпоральные операторы запрещено использовать в инварианте, но можно в PROPERTY (свойство всей модели).

С нашим свойством RSok есть небольшая проблема — оно не выполняется! Дело в том, что действие RS выполнившись может ничего не изменить, то есть в графе состояний образуется петля, в которой система, согласно нашей спецификации, может крутиться вечно. Эту петлю не сложно было бы убрать, добавив предусловия на срабатывание:

Эту петлю не сложно было бы убрать, добавив предусловия на срабатывание:

RS == (\/ ((p /= ~ (r \/ q)) /\ NOR(r, q, p) /\ UNCHANGED q) \/ ((q /= ~ (p \/ s)) /\ NOR(p, s, q) /\ UNCHANGED p) \/ (((p /= ~ (r \/ q)) /\ (q /= ~ (p \/ s)) /\ NOR(r, q, p) /\ NOR(p, s, q))) /\ UNCHANGED <<r,s>>

Но дело обстоит хуже — если задана проверка темпоральных свойств модели, TLA+ автоматически добавляет петлю в каждый узел. Это делается для «композируемости» моделей — если мы составляем модель из нескольких, действие в одном компоненте оставляют без изменения состояния не связанных с ним компонентов. Таким образом свойства компонента должны быть инвариантны к наличию петель.

Что бы с этим как-то жить, TLA+ поддерживает «справедливость» (fairness) — ему можно указать, что если переход возможен, он когда-нибудь произойдет.

vars == <<r,s,p,q, stable, oldp, oldq>>

Spec == Init /\ [][Next]_vars /\ WF_vars(Next)

Fairness указывается заклинанием

WF_vars(Next)Полный файл rs. tla

tla

--------------------------------- MODULE rs --------------------------------- VARIABLES r,s,p,q, stable, oldp, oldq vars == <<r,s,p,q, stable, oldp, oldq>> NOR(a,b,c) == c' = ~ (a \/ b) Init == /\ r = FALSE /\ s = FALSE /\ p = TRUE /\ q = FALSE /\ stable = FALSE /\ oldp = p /\ oldq = q RS == (\/ (NOR(r, q, p) /\ UNCHANGED q) \/ (NOR(p, s, q) /\ UNCHANGED p) \/ (NOR(r, q, p) /\ NOR(p, s, q))) /\ UNCHANGED <<r,s>> Check == /\ oldp' = p /\ oldq' = q /\ stable' = (r = FALSE /\ s = FALSE) Change == /\ p = ~ (r \/ q) /\ q = ~ (p \/ s) /\ IF r = FALSE /\ s = FALSE THEN \/ (r' = TRUE /\ s' = FALSE) \/ (r' = FALSE /\ s' = TRUE) ELSE r' = FALSE /\ s' = FALSE /\ UNCHANGED <<p,q>> Next == Check /\ (RS \/ Change) OutputOk == p /= TRUE \/ q /= TRUE Invariant == /\ (r = FALSE \/ s = FALSE) /\ (stable => oldq = q /\ oldp = p) /\ OutputOk Spec == Init /\ [][Next]_vars /\ WF_vars(Next) RSok == /\ [] (r ~> q) /\ [] (s ~> p) =================================================================================

Теперь создадим конфигурацию для проверки модели rs. cfg

cfg

SPECIFICATION Spec

PROPERTY RSok

INVARIANT Invariant

Проверка модели запускается командой

tlc2 rs.tlaили указав значения из конфигурации в настройках модели в графической оболочке

tla-toolbox.

RS – Триггер

1.14.1. RS – Триггер.

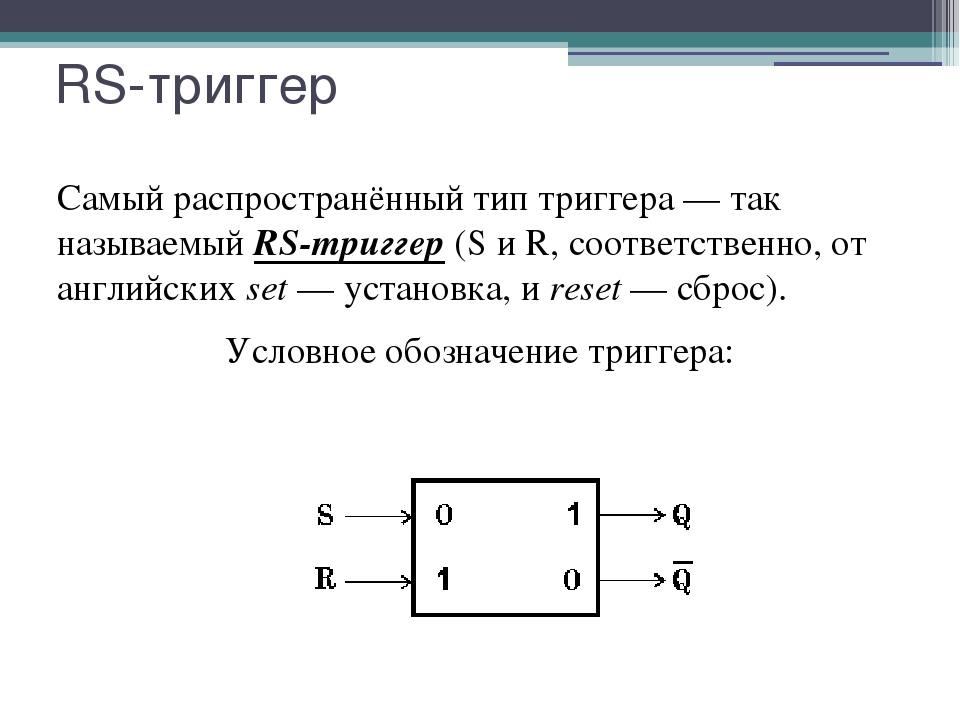

RS — Триггер имеет два входа S и R, основной и инверсный выходы. Состояние триггера определяется по сигналу на основном входе. Вход S называется входом установки, а вход R входом сброса. При подаче управляющего сигнала на вход S на основном входе устанавливается логическая единица или эта единица подтверждается, если она там была. При подаче управляющего сигнала на вход R на основном входе появляется логический ноль, как говорят, триггер сбрасывается. Если триггер был уже сброшен , то сброс подтверждается. Подача управляющих сигналов одновременно на входы S и R запрещена. В отсутствии управляющих сигналов состояние триггера измениться не может, триггер находится в режиме хранения информации. В зависимости от типа логических элементов, на которых собран триггер, управляющими сигналами могут быть, как нули, так и единицы. На рис.1.14.1 показана таблица функционирования RS – триггера.

В зависимости от типа логических элементов, на которых собран триггер, управляющими сигналами могут быть, как нули, так и единицы. На рис.1.14.1 показана таблица функционирования RS – триггера.

В таблица Qt это значение выходного сигнала к моменту подачи управляющих сигналов St и Rt , или его исходное состояние. Qt+1 – новое состояние триггера после подачи управляющих сигналов, которыми являются логические единицы.

|

|

St |

Rt |

Qt+1 |

|

|

||||||

|

0 |

0 |

0 |

0 |

Хранение информации |

|

||||||

|

0 |

0 |

1 |

0 |

Подтверждение 0 |

|

0 |

1 |

Х1 |

0 |

||

|

0 |

1 |

0 |

1 |

Установка в 1 |

|||||||

|

0 |

1 |

1 |

Х |

Запрет |

1 |

1 |

Х1 |

0 |

|||

|

1 |

0 |

0 |

1 |

Хранение информации |

|||||||

|

1 |

0 |

1 |

0 |

Сброс в 0 |

|

||||||

|

1 |

1 |

0 |

1 |

Подтверждение 1 |

|

||||||

|

1 |

1 |

1 |

Х |

Запрет |

|

||||||

Рис 1. 14.1

14.1

На рис 1.14.1 показана процедура минимизации функции Qt+1 с использованием карты Карно, полученная формула описывает работу RS триггера, но схемы триггеров строят после преобразования этой формулы, заменяя операцию умножения на сложение или сложение заменяют умножением. После замены умножения на сложение по 16-й теореме Булевой алгебры можно получить следующую формулу .

Если заменить сложение на умножение, то получим . Схемы триггеров, построенные по этим формулам показаны на рис 1.14.2. Первая из схем построена на элементах ИЛИ-НЕ, этот триггер управляется логическими единицами. Таблица его функционирования приведена на рис. 1.14.1. Схема триггера построена по второй формуле на элемента И-НЕ самая распространенная , этот триггер управляется логическими нулями, т.е. имеет инверсные входы. Таблица его функционирования показана на рис 1.14.2.

|

Qt |

St |

Rt |

Qt+1 |

|

|

0 |

0 |

0 |

Х |

Запрет |

|

0 |

0 |

1 |

1 |

Установка в 1 |

|

0 |

1 |

0 |

0 |

Подтверждение 0 |

|

0 |

1 |

1 |

0 |

Хранение информации |

|

1 |

0 |

0 |

Х |

Запрет |

|

1 |

0 |

1 |

1 |

Подтверждение 1 |

|

1 |

1 |

0 |

0 |

Сброс |

|

1 |

1 |

1 |

1 |

Хранение информации |

Рис. 1.14.2

1.14.2

На рис 1.14.3 показаны временные диаграммы переключения RS – триггера с инверсными входами с учетом задержки переключения каждого элемента на tзад.ср. Из временных диаграмм видно, что задержка полного переключения триггера равна 2tзад.ср .

Рис.1.43.3

RS – триггер может быть синхронным. В этом случае кроме двух информационных входов S и R триггер имеет еще вход синхронизации. Сигналы на входах S и R лишь подготавливают триггер к нужному переключению, а само переключение происходит только в момент подачи синхронизирующего импульса. Схема такого триггера показана на рис 1.14.4. Синхронизация организуется с помощью двух дополнительных элементов И-НЕ D1 и D2. Элементы D3 и D4 образуют несинхронный (асинхронный) RS – триггер с инверсными входами.

При отсутствии сигнала синхронизации ( С = 0 ) на входах асинхронного RS – триггера устанавливаются две единицы, что обеспечивает в нем хранение информации. При подаче синхронизирующего сигнала ( С = 0 ) триггер переключается соответственно поданной информации на входы S и R.

Рис. 1.14.4

- D – триггер.

D – триггер, называемый еще триггером задержки может быть асинхронным и синхронным, но асинхронный D – триггер смысла не имеет, т.

к. имеет один информационный вход D и основной и инверсный выходы. Сигнал (информация ) на выходе всегда совпадает с информацией на входе, т.е. Qt+1 = Dt. Смысл имеет только синхронный D – триггер, у которого кроме информационного входа D есть вход синхронизации С. Информация со входа D передается на основной выход (записывается в триггер) в момент прихода синхронизирующего импульса. Структурная формула, описывающая работу синхронного D – триггера следующая: . Из формулы видно, что при С = 0 состояние триггера не меняется , а при С = 1 состояние триггера совпадает со значением информации на входе D . Таким образом при отсутствии синхронизирующего импульса состояние триггера не меняется, информация записанная в триггер сохраняется (задерживается) на период следования синхронизирующих импульсов. На рис 1.14.5 показан один из вариантов схемы D – триггера и его условное обозначение. При С = 0, на входах асинхронного RS – триггера, входящего в состав D – триггера, устанавливаются две единицы, что означает хранение информации.

к. имеет один информационный вход D и основной и инверсный выходы. Сигнал (информация ) на выходе всегда совпадает с информацией на входе, т.е. Qt+1 = Dt. Смысл имеет только синхронный D – триггер, у которого кроме информационного входа D есть вход синхронизации С. Информация со входа D передается на основной выход (записывается в триггер) в момент прихода синхронизирующего импульса. Структурная формула, описывающая работу синхронного D – триггера следующая: . Из формулы видно, что при С = 0 состояние триггера не меняется , а при С = 1 состояние триггера совпадает со значением информации на входе D . Таким образом при отсутствии синхронизирующего импульса состояние триггера не меняется, информация записанная в триггер сохраняется (задерживается) на период следования синхронизирующих импульсов. На рис 1.14.5 показан один из вариантов схемы D – триггера и его условное обозначение. При С = 0, на входах асинхронного RS – триггера, входящего в состав D – триггера, устанавливаются две единицы, что означает хранение информации. Можно проследить по схеме, что при С = 1 триггер установится в 1 если на его входе D была 1 и сбросится в 0, если на входе D был логический 0.

Можно проследить по схеме, что при С = 1 триггер установится в 1 если на его входе D была 1 и сбросится в 0, если на входе D был логический 0.

Рис 1.14.5

- Т – триггер

Несинхронный Т – триггер имеет один вход Т, основной и инверсный выходы. Входной импульс переключает триггер в противоположное состояние. Структурная формула, описывающая работу Т- триггера имеет следующий вид:. У синхронного Т – триггер а есть еще вход синхронизации. Этот триггер переключается сигналом на входе Т в противоположное состояние только при наличии логической единицы на входе синхронизации С. Т –триггер называют «счетным» триггером, т.к. делит частоту следования управляющих импульсов в два раза, или, как говорят, «пересчитывает» их вдвое.

На рис 1.14.6 показана схема Т – триггера с элементами задержки. Основным признаком Т – триггера является подача на информационные входы синхронного RS триггера входящего в состав Т – триггера, информации с выходов этого же триггера.

Рис 1.14.6

Если триггер перед подачей очередного входного импульса был сброшен, то логическая единица с его инверсного входа поступает на информационный вход S синхронного RS – триггера (верхний вход элемента D1) и поэтому триггер переключается в состояние «единица». При единичном исходном состоянии единица с основного выхода поступает на вход сброса синхронного RS – триггера и триггер сбрасывается в «0», т.е. опять переключается в противоположное состояние.

Устройства задержки в схеме триггера необходимы для того, чтобы легче было выполнить условие tUвхпер.

тр. Длительность входного импульса обязательно должна быть меньше времени переключения триггера, т.к. в противном случае триггер может переключиться не один раз под действием одного входного импульса. Создать управляющий импульс короче времени переключения триггера довольно сложно. Введение задержки, увеличивающей время переключения уменьшает требования к длительности входного импульса, но создает усложнение схемы, особенно при её миниатюризации, т.к. конденсаторы, входящие в состав элементов задержки плохо миниатюризируются. На рис 1.14.7 показана схема двухступенчатого триггера, свободного от этого недостатка.

тр. Длительность входного импульса обязательно должна быть меньше времени переключения триггера, т.к. в противном случае триггер может переключиться не один раз под действием одного входного импульса. Создать управляющий импульс короче времени переключения триггера довольно сложно. Введение задержки, увеличивающей время переключения уменьшает требования к длительности входного импульса, но создает усложнение схемы, особенно при её миниатюризации, т.к. конденсаторы, входящие в состав элементов задержки плохо миниатюризируются. На рис 1.14.7 показана схема двухступенчатого триггера, свободного от этого недостатка.

Рис 1.14.7

Двухступенчатый Т – триггер состоит из двух синхронных RS – триггеров и инвертора. При подаче первого перепада из 0 в1 входного импульса переключается в противоположное состояние только первая ступень всего триггера ( первый RS – триггер на элементах D1,D2,D3). Вторая ступень не меняет своего состояния, т.к. логическая единица со входа триггера через инвертор D7 поступает на элементы D4 и D5 и обеспечивает на инверсных входах RS –триггера D6 две единицы и, следовательно, хранение информации на выходе Т – триггера. При окончании входного импульса логический ноль на входе сохраняет состояние первой ступени триггера, но меняется на противоположное второй ступени, т.е. всего Т – триггера. Такое управление триггером, когда переключение происходит только под действием импульса, т.е. под действием двух перепадов напряжения называется динамическим управлением. На рис 1.14.7 показаны условные обозначения двух типов Т – триггеров с динамическим входом. Верхний триггер имеет динамический инверсный вход. Это означает, что триггер переключается перепадом из 1 в 0. Рассмотренный триггер имеет такой вход. Другой триггер имеет прямой динамический вход, это означает, что он переключается перепадом из 0 в 1, а перепадом из 1 в 0 переключается только первая ступень триггера.

Вторая ступень не меняет своего состояния, т.к. логическая единица со входа триггера через инвертор D7 поступает на элементы D4 и D5 и обеспечивает на инверсных входах RS –триггера D6 две единицы и, следовательно, хранение информации на выходе Т – триггера. При окончании входного импульса логический ноль на входе сохраняет состояние первой ступени триггера, но меняется на противоположное второй ступени, т.е. всего Т – триггера. Такое управление триггером, когда переключение происходит только под действием импульса, т.е. под действием двух перепадов напряжения называется динамическим управлением. На рис 1.14.7 показаны условные обозначения двух типов Т – триггеров с динамическим входом. Верхний триггер имеет динамический инверсный вход. Это означает, что триггер переключается перепадом из 1 в 0. Рассмотренный триггер имеет такой вход. Другой триггер имеет прямой динамический вход, это означает, что он переключается перепадом из 0 в 1, а перепадом из 1 в 0 переключается только первая ступень триггера.

Т – триггер может быть построен на D – триггере. Если в структурной формуле D – триггера приравнять D к то получим . Полученная формула совпадает с формой Т – триггера. Вход С D – триггера играет роль входа Т Т – триггера. Следовательно для получения Т – триггера на основе D – триггера достаточно соединить вход D с инверсным выходом, а вход синхронизации С использовать как вход Т – триггера.

1.14.4 Универсальный JK –триггер.

Несинхронный JK – триггер имеет два входа J и K, основной и инверсные входы. Вход J аналогичен входу S RS – триггера. По этому входу триггер устанавливается в состояние «1». По входу K триггер сбрасывается в «0», как и RS – триггер по входу R. Отличие от RS – триггера состоит в том, что этот триггер не имеет запрещенных комбинаций сигналов на входах, а при подаче управляющих сигналов одновременно на оба входа триггер переключается в противоположное состояние. Синхронный JK – триггер имеет еще один вход С – вход синхронизации и переключается только при подаче импульса на этот вход.

Структурная формула, описывающая работу несинхронного JK – триггера имеет следующий вид: . JK – триггер называют универсальным, т.к. из него можно сделать любой тип триггера. RS – триггер получается из JK – триггера, когда входы JK используются, как входы S и R соответственно, а запрещенная комбинация не подается.

Если в формуле несинхронного JK – триггера J назвать входом D, а на вход K подать , то получим: , что соответствует несинхронному D – триггеру, но т.к. несинхронный D – триггер смысла не имеет, то для получения синхронного D – триггера нужно использовать синхронный JK – триггер. Для получения T – триггера достаточно объединить входы J и K и назвать этот вход входом Т по которому триггер будет переключаться в противоположное состояние, как это должен делать Т – триггер. На рис 1.14.8 показано условные обозначения JK – триггеров и выполнение на основе JK – триггеров другие типы триггеров.

|

несинхр.

RS – триггер Т – триггер

RS – триггер Т – триггер

синхр. D – триггер

Рис 1.14.8

- Регистры.

Регистром называют последовательное устройство предназначенное для хранения небольшого объёма цифровой информации (числа). Один из типов регистров, последовательный регистр, позволяет производить над этим числом арифметические операции умножения и деления.

Процедура ввода числа в регистр называется записью. Процедура вывода числа называется считыванием. По способу записи и считывания различают следующие типы регистр: 1. Параллельный регистр, в котором и запись и считывание производят в параллельном коде, т.е. во все разряды одновременно записывается число и одновременно со всех разрядов считывается. 2. Последовательный регистр, в котором и запись и считывание производятся в последовательном коде, т.е. последовательно разряд за разрядом. 3. Параллельно – последовательный регистр, в котором запись производится в параллельном коде, а считывание в последовательном. 4. Последовательно – параллельный, в котором запись производится в последовательном коде, а считывание в параллельном.

2. Последовательный регистр, в котором и запись и считывание производятся в последовательном коде, т.е. последовательно разряд за разрядом. 3. Параллельно – последовательный регистр, в котором запись производится в параллельном коде, а считывание в последовательном. 4. Последовательно – параллельный, в котором запись производится в последовательном коде, а считывание в параллельном.

Рассмотрим примеры построения схем перечисленных типов регистров.

1.

Параллельный регистр на D – триггерах.

Рис 1.14.9

Информация (число) записывается во все разряды регистра, во все D – триггеры одновременно, т.е. параллельным кодом. В приведенной на рисунке схеме считывание выполняется с использованием элементов И – НЕ, часть из которых превращается в инверторы путем объединения двух входов. При отсутствии сигнала считывания, которым является логическая единица, т.е. при нуле на входе считывания, на всех выходах установятся логические нули. При единице на входе «счит.» число на выходах будет равно числу, записанному в триггерах.

При отсутствии сигнала считывания, которым является логическая единица, т.е. при нуле на входе считывания, на всех выходах установятся логические нули. При единице на входе «счит.» число на выходах будет равно числу, записанному в триггерах.

2. Последовательный регистр.

последовательный регистр строится на D – триггерах путем соединения выхода каждого триггера со входом «D» следующего. Для записи и считывания одновременно на входы синхронизации всех триггеров подаются тактовые импульсы «ТИ» рис 1.14.10

Рис 1.14.10

Первым тактовым импульсом первая единица старшего разряда числа 101 записывается в первый триггер. Вторым тактовым импульсом в первый триггер записывается значение следующего разряда (в нашем примере 0), а во второй триггер записывается единица, которая была перед приходом второго тактового импульса на выходе первого триггера.

Таким образом каждый тактовым импульсом в регистре происходит сдвиг числа на один разряд. Трехразрядное число будет полностью записано в регистр после третьего тактового импульса. При этом на выходе регистра можно просчитать значения разряда, который был записан первым. Для считывания значений следующих двух разрядов нужно подать ещё два тактового импульса. В двоичной системе счисления при сдвиге числа на один разряд в сторону старших разрядов происходит увеличения числа в два раза. При сдвиге числа в сторону младших разрядов число записывается в регистр уменьшается в два раза. Таким образом сдвигающий регистр можно использовать для умножения или деления числа на 2n , где n – количество сдвигов равное количеству под тактовых импульсов.

3. Параллельно – последовательный регистр.

В параллельно – последовательном регистре запись информации происходит в параллельном коде, а считывание в последовательном.

На рис 1.14.11 показан пример построения такого регистра на JK – триггерах.

На рис 1.14.11 показан пример построения такого регистра на JK – триггерах.

Рис 1.14.11

В приведенной схеме JK – триггеры дважды превращены в D – триггеры. Одно превращение осуществлено для организации записи с использованием вспомогательных инверсных входов S и R и, добавлением двух элементов И –НЕ. Этот способ построения триггера показан на рис 1.14.5. Запись числа в регистр в параллельном коде происходит при подаче числа на входы х1, х2, х3 и сигнала «1» на вход «зап». Для считывания информации из регистр в последовательном коде JK – триггеры второй раз превращены в D – триггеры у которых выходы каждого триггера соединены со входом D следующего, как это делается в последовательном регистре. Во втором случае JK – триггеры превращены в D – триггеры способом показанном на рис 1.14.8, но вместо дополнительного инвертора используется инверсный выход предыдущего триггера. Исключение составляет первый триггер, у которого входы J и K объединены и соединены с основным входом этого же триггера. Благодаря такой схеме после подачи импульсов считывания первый триггер оказывается в состоянии «0».

Исключение составляет первый триггер, у которого входы J и K объединены и соединены с основным входом этого же триггера. Благодаря такой схеме после подачи импульсов считывания первый триггер оказывается в состоянии «0».

- Последовательно – параллельный регистр.

Для построения последовательно – параллельного регистра достаточно в последовательном регистре организовать параллельное считывание используя дополнительные элементы И – НЕ, как это показано на рис 1.14.12.

Рис. 1.14.12

При подаче сигнала «1» на вход «счит» значение разрядов числа с инверсных выходов триггеров поступают на выходы У1, У2, У3 через элементы И – НЕ.

- Счетчики импульсов.

Счетчиком называется устройство, предназначенное для подсчета числа импульсов, поступающих на его вход, и фиксации этого числа в виде кода, хранящегося в триггерах. Счетчик относится к последовательным логическим устройствам. Число разрядов счетчика определяется наибольшим числом подсчитываемых импульсов. В счетчиках имеется один вход и n выходов по числу разрядов. Для установки начального состояния счетчика (сброс в ноль) обычно предусматривается вход сброса.

По назначению счетчики могут быть суммирующими, вычитающими и реверсивными.

Суммирующие счетчики производят сложение чисел поступающих на вход импульсов с тем числом, которое хранилось в нем.

Вычитающие счетчики производят вычитание числа поступающего импульса из начального числа, записанного в нем заранее.

Реверсивные счетчики могут производить как сложение, так и вычитание поступающих на вход импульсов в зависимости от управляющих сигналов, меняющих режим работы счетчика.

По способу переноса сигнала в старший разряд счетчики могут быть с последовательным, параллельным и сквозным переносом.

Счетчики отличаются друг от друга кодом, в котором они работают. Код всегда бывает двоичным, но может иметь различные веса разрядов, например вес 8421 или 5211 и т.п., двоично-десятичным, когда значение каждого разряда десятичного числа кодируется двоичным кодом.

Счетчики бывают синхронными, когда счетные импульсы подаются счетные входы всех триггеров, и асинхронными, когда сигнал на счетный вход какого-либо триггера подается с выхода одного из триггеров младших разрядов.

Счетчики строятся на Т – триггерах или на универсальных JK – триггерах.

Максимальное число, которое может быть записано в счетчике, равно числу его состояний и называется модулем счета Ксч . Счетчик , не имеющий дополнительных связей , имеет модуль счета Ксч = 2n . Счетчики, имеющие модуль счета 2n , называются двоичными. Если Ксч ¹ 2n, то счетчик называется не двоичным. Одним из недвоичных является двоично-десятичный счетчик.

Если Ксч ¹ 2n, то счетчик называется не двоичным. Одним из недвоичных является двоично-десятичный счетчик.

1. Суммирующий двоичный асинхронный счетчик с последовательным переносом.

Схема двоичного счетчика с последовательным переносом на JK – триггерах, работающего в коде 8421, показана на рис 1.14.13. Здесь JK – триггеры превращены в Т – триггеры путем подачи «1» на вход J и K .

Рис. 1.14.13

Поскольку триггеры имеют инверсный динамический вход, то каждый последующий триггер будет переключаться при сбросе в «0» предыдущего триггера. Важным параметром счетчика является его максимальное время установления кода, т.е. время, необходимое для установления кода после подачи счетного импульса. В схемах счетчиков с последовательным переносом максимальное время установления Туст определяется суммой времени задержки переключения всех триггеров. Время установления Туст определяет быстродействие счетчика. Счетчики с последовательным переносом обладают сравнительно плохим быстродействием.

В схемах счетчиков с последовательным переносом максимальное время установления Туст определяется суммой времени задержки переключения всех триггеров. Время установления Туст определяет быстродействие счетчика. Счетчики с последовательным переносом обладают сравнительно плохим быстродействием.

2. Суммирующий двоичный счетчик с последовательным переносом.

Наличие сигнала переноса в старший разряд определяется выражениями:

P12 = Q1×C1; P23 = Q1×Q2×C; P34 = Q1×Q2×Q3×C,

, где Р12 – сигнал переноса из первого разряда во второй; Р23 – сигнал переноса из второго разряда в третий и т.п.

Для любого разряда Pn(n+1) = Q1×Q2×Q3, …, Qn×C . В схеме счетчика с параллельным переносом сигналы переноса в каждый разряд формируются согласно приведенным формулам.

Схема счетчика с параллельным переносом показана на рис 1.1.4.14.

Рис. 1.14.14

Время установления кода при параллельной организации переноса определяется задержкой переключения одного триггера и временем задержки срабатывания схем И и существенно меньше, чем при последовательном переносе.

Недостатком параллельного переноса является то, что при большом числе разрядов требуются схемы И с большим числом входов.

2. Суммирующий счетчик со сквозным переносом.

При сквозном переносе триггеры счётчика объединяются в группы, внутри каждой группы осуществляется параллельный перенос, а между группами – последовательный. На рис 1.14.15 представлена схема счетчика со сквозным переносом, каждая группа которого содержит по два триггера.

При такой организации переноса все схемы умножения должны быть двухвходовыми. Время установления кода в счетчике со сквозным переносом определяется задержкой переключения триггера, задержка переключения схем И и инвертора в одной группе и количеством групп. Таким образом, быстродействие такого счетчика является промежуточным между быстродействиями счетчиков с последовательным и параллельным переносом.

При такой организации переноса все схемы умножения должны быть двухвходовыми. Время установления кода в счетчике со сквозным переносом определяется задержкой переключения триггера, задержка переключения схем И и инвертора в одной группе и количеством групп. Таким образом, быстродействие такого счетчика является промежуточным между быстродействиями счетчиков с последовательным и параллельным переносом.

4. Реверсивный счётчик.

Для построения вычитающего счетчика достаточно подать сигнал переноса на триггер старшего разряда не с прямого выхода предыдущего триггера, а с инверсного.

Связи между триггерами реверсивного счётчика соответствуют как суммирующему, так и вычитающему счётчику, но работает только одна из связей, которая определяется командой «Реверс» и подается на элемент И–НЕ, включенные в цепи передачи сигнала переноса. Схема реверсивного счётчика показана на Рис 1.14.16.

Схема реверсивного счётчика показана на Рис 1.14.16.

Пример синтеза двоично-десятичного счетчика.

Пусть требуется синтезировать асинхронный счетчик, работающий в коде 5-2-1-1. В соответствии с заданным кодом заполняем левую часть табл. 1 функционирования счётчика (столбцы Q4, Q3, Q2, Q1, n).

Таблица 1

|

.n |

Q4 |

Q3 |

Q2 |

Q1 |

|

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

J4 |

K4 |

|

0 |

0 |

0 |

0 |

0 |

1 |

— |

0 |

— |

— |

— |

— |

— |

|

|

1 |

0 |

0 |

0 |

1 |

— |

0 |

1 |

— |

— |

— |

— |

— |

|

|

2 |

0 |

0 |

1 |

1 |

— |

0 |

— |

1 |

1 |

— |

— |

— |

|

|

3 |

0 |

1 |

0 |

1 |

— |

0 |

1 |

— |

— |

— |

— |

— |

|

|

4 |

0 |

1 |

1 |

1 |

— |

1 |

— |

1 |

— |

1 |

1 |

— |

|

|

5 |

1 |

0 |

0 |

0 |

1 |

— |

0 |

— |

— |

— |

— |

— |

|

|

6 |

1 |

0 |

0 |

1 |

— |

0 |

1 |

— |

— |

— |

— |

— |

|

|

7 |

1 |

0 |

1 |

1 |

— |

0 |

— |

1 |

1 |

— |

— |

— |

|

|

8 |

1 |

1 |

0 |

1 |

— |

0 |

0 |

— |

— |

— |

— |

— |

|

|

9 |

1 |

1 |

1 |

1 |

— |

1 |

— |

1 |

— |

1 |

— |

1 |

В таблице n – номер состояния счетчика, меняющийся на единицу при подаче каждого счетного импульса; Q1, Q2, Q3 и Q4 – логические переменные на выходе четырех триггеров, первый триггер с выходом Q1 соответствует первому младшему разряду; J и K – значения соответствующих сигналов на соответствующих входах JK – триггеров.

Каждый из универсальных триггеров может переключаться при подаче на вход С положительного («одиночного») импульса либо при подаче сигнала на вход С с выхода другого триггера. При этом переключение последующего триггера происходит тогда, когда предыдущий переключается из «1» в «0». Учитывая это, находим необходимое место подключения входов С всех четырех триггеров. Первый триггер должен переключаться при подаче первого, пятого и нулевого (десятого) импульса. Ни один из последующих триггеров не может обеспечить всех трех переключений. Поэтому на вход С первого триггер нужно подавать счетные импульсы. Они обеспечивают максимальную частоту переключений, а выборка нужных моментов переключения обеспечивается подачей сигналов на вход J и K .

На вход с второго триггера также нужно подать счетные импульсы, так как выходные сигналы ни одного из триггеров не обеспечат его переключения в нужный момент.

Вход С третьего триггера нужно соединить с выходом второго, так как его переключение при подаче третьего, пятого, восьмого триггера в эти моменты времени из «1» в «0».

По тем же соображениям выход третьего триггера нужно соединить со входом четвертого. Для определения сигналов на входах J и K заполняют правую часть табл. 1, используя таблицу функционирования JK – триггера (табл. 2). Почерк в таблице показывает, что значение сигнала в данном виде не вызывает изменения или сохранения состояния триггера. Например, для переключения первого триггера из «0» в «1» при подаче первого счетного импульса требуется, чтобы J1 = 1 в позиции n = 0,а значения K1 может быть любым, что означает прочерк. Если при очередном такте работы на какой – либо триггер сигнал переноса не подается, т.е. триггер, с которого он может прийти, не сбрасывается в «0», то в соответствующих клетках J и K можно ставить прочерки, так как при любых значениях J и K триггер не переключается. Таким способом заполняется

вся таблица.

Таблица 2

|

Qn ® Qn+1 |

Jn |

Kn |

|

0 0 |

0 |

— |

|

0 1 |

1 |

— |

|

1 0 |

— |

1 |

|

1 1 |

— |

0 |

Перенесем теперь данные правой части табл. 1 на диаграммы Вейча. В табл. 3 приведена диаграмма Вейча для четырех логических переменных. Принимаем за логические переменные значения сигналов на выходах триггеров и заполним восемь диаграмм Вейча (табл. 4), по которым определим сигналы на входах J и K четырех триггеров. При заполнении диаграмм единицы, нули или прочерк ставятся в тех клетках, в которых находятся соответствующие комбинации выходных переменных Q.

1 на диаграммы Вейча. В табл. 3 приведена диаграмма Вейча для четырех логических переменных. Принимаем за логические переменные значения сигналов на выходах триггеров и заполним восемь диаграмм Вейча (табл. 4), по которым определим сигналы на входах J и K четырех триггеров. При заполнении диаграмм единицы, нули или прочерк ставятся в тех клетках, в которых находятся соответствующие комбинации выходных переменных Q.

Таблица 4

J1

|

— |

— |

— |

— |

|

— |

— |

— |

— |

|

— |

— |

— |

1 |

|

— |

— |

— |

1 |

В клетках, в которых функция не определена или её значение не играет роли (т. е. ставится прочерк), можно помещать любые значения переменных, чтобы объединить контуром наибольшее количество клеток. Так, в табл. 4 для J1 во всех клетках можно поставить единицы и объединить одним контуром. Это означает, что J1 = 1.из всех других диаграмм следует, что K1 = Q2Q3 , J2 =Q1 , K2 = 1, J3 = 1, K3 =1, J4 =1, K4 = 1. Следовательно, на входы J1, K2, J3, K3, J4, K4 надо подать единицы, на вход K1 – конъюнкцию сигналов с прямых выходов второго и третьего триггеров, а вход J2 соединить с прямым выходом первого триггера. Если какой либо вход не куда не подключен, это эквивалентно подаче на этот вход единицы. Таким образом, счетчик синтезирован. Его схема показана на рис. 1.14.17.

е. ставится прочерк), можно помещать любые значения переменных, чтобы объединить контуром наибольшее количество клеток. Так, в табл. 4 для J1 во всех клетках можно поставить единицы и объединить одним контуром. Это означает, что J1 = 1.из всех других диаграмм следует, что K1 = Q2Q3 , J2 =Q1 , K2 = 1, J3 = 1, K3 =1, J4 =1, K4 = 1. Следовательно, на входы J1, K2, J3, K3, J4, K4 надо подать единицы, на вход K1 – конъюнкцию сигналов с прямых выходов второго и третьего триггеров, а вход J2 соединить с прямым выходом первого триггера. Если какой либо вход не куда не подключен, это эквивалентно подаче на этот вход единицы. Таким образом, счетчик синтезирован. Его схема показана на рис. 1.14.17.

Рис 1.14.17

Синтез синхронных счетчиков производится аналогично, но счетные импульсы подаются на входы С всех триггеров, поэтому при подаче каждого счетного импульса в каждом триггере нужно обеспечивать нужные значения J и K.

Лекция 7. Триггеры.

Триггер – простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под воздействием входных сигналов.

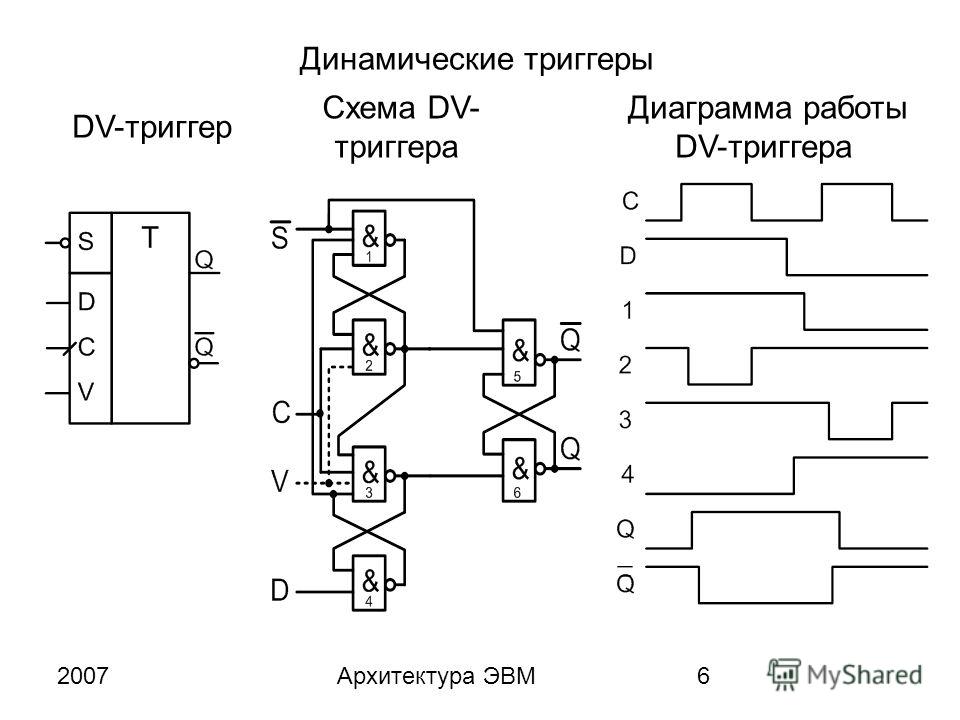

По способу работы с сигналами различают синхронные, асинхронные и смешанные триггерные схемы.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт». Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

RS-триггер или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах, и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S (от английского англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от английского англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Если RS-триггер синхронный, то состояние его входов учитывается только в момент тактирования, например по переднему фронту импульса. Состояние, при котором на оба входа R и S одновременно поданы логические единицы является запрещённым. Так, например, схема RS-триггера изображённая на рисунке, при подаче на оба инверсных входа логического нуля перейдёт в состояние, когда на обоих выходах будут единицы, что не соответствует логике выхода триггера, поскольку инверсный выход будет равен неинверсному Q , т.е..

S R Q(t) Q(t+1)

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 *

1 1 1 *

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени.

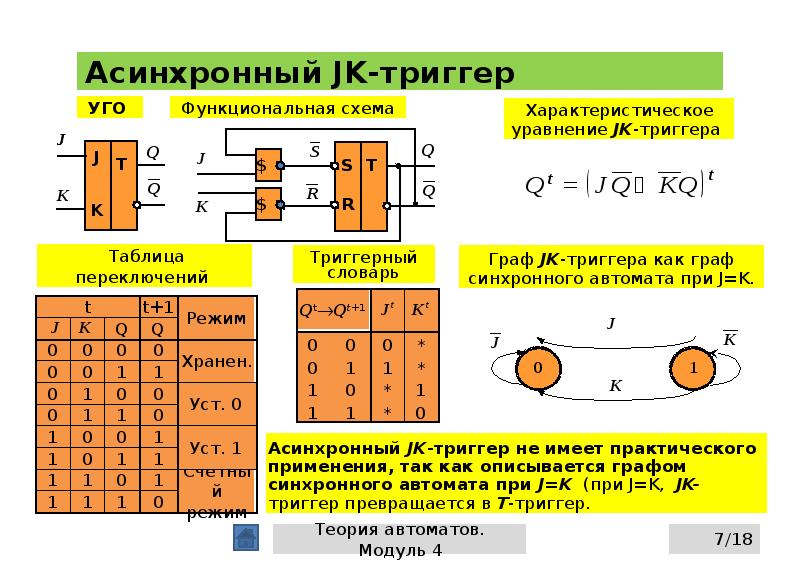

JK-триггер работает также как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становиться равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггер, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

J K Q(t) Q(t+1)

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 0

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[4].

D-триггер (D от англ. delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D Q(t) Q(t+1)

0 0 0

0 1 0

1 0 1

1 1 1

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в D-триггере динамического С входа позволяет получить на его основе T-триггер. При этом вход D соединяется с инверсным выходом, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение , то есть будет переключаться в противоположное состояние.

T Q(t) Q(t+1)

0 0 0

0 1 1

1 0 1

1 1 0

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

| < Предыдущая | Следующая > |

|---|

Pintech RS-5 Внешний барабанный триггер

Описание

ТРИГГЕР ПРОДАЖ №1 В МИРЕ!Внешние триггеры Pintech RS-5 могут устанавливаться на головке или на корпусе для обеспечения превосходной чувствительности и отклика. Система крепления «Kwik Klip» гарантирует, что входной разъем остается на месте и крепится к любому натяжному стержню без клея! Наша эксклюзивная в отрасли конструкция свободно плавающего спускового механизма позволяет спусковому крючку свободно плавать внутри корпуса, что обеспечивает наилучшее срабатывание и надежность.

Эти внешние триггеры, специально разработанные для всемирно известной триггерной системы Pintech, обеспечивают лучшую чувствительность и отклик на рынке. Легко снимается и может применяться снова и снова. Если вы ищете лучшие триггеры для денег, то вот они!

Система фиксации триггера Pintech TT3: Защищает и надежно удерживает спусковой крючок на месте. Больше не нужно беспокоиться о случайном нажатии на спусковой крючок. Изготовлен из углеродистой стали для гарантии защиты.Используйте их, чтобы лучше закрепить их на сетчатых головках.

У меня плотная ударная установка, и у меня не может быть больших громоздких триггеров на пути моих палочек. В Pintech есть важные пьезоэлементы, защищенные небольшим прочным кожухом, и ничто другое не мешает, поэтому я могу установить их внутри или снаружи корпуса или на головке большого барабана, и они будут выполнять свою работу, не мешая моей игре. Они легко и удобно прикрепляются к любому месту, где вы хотите. — Терри Боззио

Характеристики:

- Возможность установки на голову или на корпус

- Отличается эксклюзивным монтажным диском Pintech, который позволяет свободно плавающей камере свободно перемещаться вместе с головкой барабана и не повредить ее.

- Отличная чувствительность и отклик

- Монтажная система Kwik Klip

- Специально разработан для акустических или сетчатых головок

- American производства Pintech

Дополнительная информация

| Вес | НЕТ |

|---|---|

| Размеры | НЕТ |

| Опции: | Триггер RS-5, триггер RS-5 + триггер Trap, RS-5 триггер (5 шт.), RS-5 триггер + триггер Trap (5 шт.) |

RS-триггер.Принцип действия, функциональные схемы, таблица преобразования

Спусковой механизм— это простейшее устройство, представляющее собой цифровой автомат. У него два состояния стабильности. Одному из этих состояний присваивается значение «1», а другому — «0». Состояние триггера, а также значение хранящейся в нем двоичной информации определяется выходными сигналами: прямым и обратным. В случае, когда на прямом выходе устанавливается потенциал, соответствующий логической единице, состояние триггера называется одиночным (потенциал на обратном выходе равен нулю).Если на прямом выходе нет потенциала, то состояние триггера называется нулевым.

Классифицируйте триггеры следующими способами:1. По способу записываемой информации (асинхронный и синхронный).

2. По способу управления информацией (статистический, динамический, одноэтапный, многоступенчатый).

3. По способу реализации логических связей (JK-триггеры, RS-триггеры, T-триггеры, D-триггеры и другие типы).

Основными параметрами всех типов триггеров являются наибольшее значение длительности входного сигнала, время задержки, необходимое для переключения триггера, а также разрешенное время отклика.

В этой статье поговорим о таком типе устройств, как RS-триггер. Они бывают двух типов: синхронные и асинхронные.

Асинхронный RS-триггер конструктивно имеет два прямых (R и S) входа. Это устройство работает в соответствии с таблицей преобразования.

Запрещено для такого триггера комбинация сигналов на входах устройства, вызывающая состояние неопределенности. Эта комбинация может быть выражена требованием RtSt = 0. При минимизации карты Карно выводится закон триггерной функции, который называется характеристическим уравнением: Q (t + 1) = St V R’tQt.В этом случае RtSt будет нулевым.

Функциональная схема показывает триггер RS асинхронного типа для элементов И-НЕ и во втором исполнении для элементов ИЛИ-ИЛИ.

Второй тип — синхронный RS-триггер. Такое устройство конструктивно имеет три прямых входа S, R и C. Разница между синхронным триггером и асинхронным типом заключается в наличии входа синхронизации (C). Это необходимо по следующим причинам: ведь на входы устройства (логического элемента) не всегда поступают сигналы одновременно.Это связано с тем, что они проходят через разные типы и количество узлов, которые имеют разные задержки. Это явление называется «конкуренция». В результате таких «соревнований» полученные значения сигналов будут наложены на предыдущие значения других сигналов. Все это приводит к ложному срабатыванию устройства.

Это явление можно устранить, подавая сигнал на стробирующие сигнальные устройства. А именно: на вход логического элемента, помимо непосредственно информационных сигналов, подаются ключевые синхронизирующие импульсы, к этому времени сигналы ввода информации могут быть зафиксированы на входах.

Главное условие корректной работы триплогических каскадов в RS-триггерах и управляемых ими логических схемах — недопустимость одновременного срабатывания сигнала Rt или St переключения устройства, а также снятие информации с выход Q (t + 1) триггера. В связи с этим потенциальные серии элементов содержат только синхронные.

RS-триггер синхронного типа представлен характеристическим уравнением: Q (t + 1) = StCt V R’tQt V QtC «t.

На фото триггер RS синхронного типа на элементах NAND.

Входные логические элементы И-НЕ передает коммутирующую логическую единицу с информационного входа S или R на необходимые входы асинхронного триггера типа RS с инверсными входами только при наличии сигнала с логической единицей на синхронном входе (C).Pintech Percussion RS-5 Acoustic Head Trigger

От редакции ОбзорТРИГГЕР №1 ПО ПРОДАЖЕ В МИРЕ! Эти внешние триггеры RS-5 могут быть установлены на голове или на корпусе для обеспечения превосходной чувствительности и отклика.Система крепления «Kwik Klip» гарантирует, что аудиоразъем остается на месте и крепится к любому натяжному стержню без клея! Эти внешние триггеры, специально разработанные для всемирно известной триггерной системы Pintech, предлагают лучшую чувствительность и реакцию на рынке. Легко снимается и может применяться снова и снова. Если вы ищете лучшие триггеры для денег, то вот они! «Моя ударная установка плотная, и у меня не может быть больших громоздких триггеров на пути к моим пикам. У Pintech есть важная пьезоэлектрическая защита в небольшой прочной крышке, и ничто другое не мешает, поэтому я могу установить их внутри или снаружи на корпусе или на пластине большого барабана, и они делают свою работу, не мешая моей игре.Они легко и удобно закрепляются в любом месте, где вы хотите «. — Терри Боззио Особенности: Возможность установки на головку или корпус Особенности эксклюзивного монтажного диска Pintech, который позволяет свободно плавающей камере перемещаться вместе с головкой барабана и не повредить ее. Превосходная чувствительность и response Система крепления «Kwik Klip» Специально разработана для акустических или сетчатых головок American made by Pintech

Характеристики

1) Возможность установки на головку или корпус

2) Особенности Эксклюзивный монтажный диск Pintech, который позволяет свободно плавающей камере перемещаться вместе с головкой барабана и не повредить его.

3) Отличная чувствительность и отклик

4) Система крепления «Kwik Klip»

5) Сделано в США!

Спецификация

Переплет: Электроника

Марка: Pintech Percussion

EAN: 0734797100321

Этикетка: Pintech Percussion

Производитель: Pintech Percussion

Модель: RS-5

Размеры упаковки_Вес: 45,00 сотых фунтов

Размеры упаковки: L: 6,00 XW: 3,00

Группа продуктов: Музыкальные инструменты

Тип продукта: PERCUSSION_INSTRUMENTS

Издатель: Pintech Percussion

Размер: -дюймы

Студия: Pintech Percussion

Название: Pintech Percussion Триггер акустической головки RS-5

Что такое RS Flip Flop? Логический элемент NAND и NOR RS Flip Flop & Truth Table

Flip Flop — это бистабильное устройство.Существует три класса триггеров, они известны как защелки , триггеры с импульсным запуском, триггеры, триггеры по фронту, триггеры. В этом наборе слово означает, что выход схемы равен 1, а слово сброс означает, что выход равен 0.

Существует два типа триггеров: один — RS Flip Flop и JK Flip Flop . В этой статье подробно описывается RS Flip Flop.

Содержание :

RS-триггер считается одной из самых простых схем последовательной логики.Flip Flop — это бистабильное устройство с однобитной памятью.

Он имеет два входа, один называется «SET» , который устанавливает устройство (выход = 1) и помечен S, а другой известен как «RESET» , который сбрасывает устройство (выход = 0), помеченный как R. RS означает SET / RESET.

Триггер сбрасывается обратно в исходное состояние с помощью входа RESET, а выходом является Q, который будет либо на логическом уровне «1», либо на логическом «0». Это зависит от состояния установки / сброса триггера.Слово триггера означает, что оно может быть «ПЕРЕВОРОЧЕНО», перешло в одно логическое состояние или «ЗАБЛОКИРОВАНО» обратно в другое.

Базовая схема RS-триггера логического элемента И-НЕ используется для хранения данных и, таким образом, обеспечивает обратную связь с обоих выходов обратно на входы. RS-триггер фактически имеет три входа: SET, RESET и токовый выход Q, относящийся к его текущему состоянию.

Обозначение RS Flip-Flop показано ниже:

Триггер NAND Gate RS

Пара перекрестно связанных логических элементов NAND из 2 блоков — это самый простой способ сделать любой базовый однобитовый RS-триггер с установкой / сбросом.Он образует бистабильную установку / сброс или активную защелку логического элемента LOW RS NAND. Обратная связь подается с каждого выхода на один из других входов логического элемента И-НЕ.

Устройство состоит из двух входов; один известен как SET (S), а другой — как RESET (R).

Два выхода — это столбцы Q и Q, как показано на рисунке ниже:

Состояние набора

С учетом приведенной выше схемы. Если вход R находится на логическом уровне «0» (R = 0), а вход S — на логической «1» (S = 1), элемент И-НЕ Y имеет, по крайней мере, один из своих входов на логическом «0». ».Следовательно, его выход Q должен иметь логический уровень «1» (принципы логического элемента И-НЕ). Выход (Q) возвращается на вход «A». Оба входа вентилей И-НЕ X находятся на логической «1», и, следовательно, его выход Q должен быть на логическом уровне «0».

Вход сброса R изменяет свое состояние и переходит в ВЫСОКИЙ уровень до логической «1» с константой S на уровне логической «1». Вход Y логического элемента И-НЕ теперь (R = 1) и (B = 0). Выход на Q остается на ВЫСОКОМ уровне или на логическом уровне «1», поскольку один из его входов все еще находится на логическом уровне «0».

В результате нет изменений в состоянии.Следовательно, триггерная схема называется «ЗАБЛОКИРОВАНО» или «УСТАНОВЛЕНА» с Q = 1 и Ǭ = 0.

Состояние сброса

В этом втором стабильном состоянии Q находится на логическом уровне «0», а его обратный выход Q — на логическом уровне «1». И задается формулами (R = 1) и (S = 0). Поскольку вентиль X имеет один из своих входов на логическом «0», его выход Q должен быть равным логическому уровню «1». (По принципу NAND gate). Выход Q подается на вход B, поэтому оба входа логического элемента И-НЕ Y имеют логическую «1». Следовательно, Q = 0.

Если установленный вход S теперь меняет состояние на логическую «1», а вход R остается на логической «1», выход Q по-прежнему остается НИЗКИМ на логическом уровне «0». И нет никаких изменений в состоянии.

Следовательно, состояние «СБРОС» триггерных схем было зафиксировано.

Таблица истинности Set / Reset приведена ниже:

| Состояние | S | R | Q | Ǭ | Описание |

|---|---|---|---|---|---|

| НАБОР | 1 | 0 | 1 | 0 | Набор Q >> 1 |

| 1 | 1 | 1 | 0 | Без изменений | |

| СБРОС | 0 | 1 | 0 | 1 | Сброс Q >> 0 |

| 1 | 1 | 0 | 1 | Без изменений | |

| НЕДЕЙСТВИТЕЛЬНО | 0 | 0 | 0 | 1 | Память с Q = 0 |

| 0 | 0 | 1 | 0 | Память с Q = 1 |

Из таблицы истинности ясно, что когда оба входа S = 1 и R = 1, выходы Q и Ǭ могут быть на логическом уровне «1» или «0» в зависимости от состояния входов. .

Когда состояние входа R = 0 и S = 0 является недопустимым условием, и его следует избегать, потому что это даст оба выхода Q и Ǭ на логическом уровне «1» одновременно, и необходимое условие состоит в том, чтобы Q было инверсным. из Ǭ.

Триггер переходит в нестабильное состояние, так как оба выхода переходят в НИЗКИЙ. Это нестабильное состояние возникает, когда вход LOW переключается на HIGH. Триггер переключается в то или иное состояние, и любой из выходов триггера переключается быстрее, чем другой.Это нестабильное состояние известно как метастабильное состояние.

Бистабильный триггер RS активируется или устанавливается на логическую «1», приложенную к его входу S, и деактивируется или сбрасывается логической «1», примененной к R. Говорят, что RS-триггер находится в недопустимом состоянии, если оба входы установки и сброса активируются одновременно.

Триггер NOR Gate RS

Принципиальная схема триггера с вентилем ИЛИ-НЕ показана на рисунке ниже:

Простые однобитовые RS-триггеры изготавливаются с использованием двух перекрестно связанных вентилей ИЛИ-НЕ, соединенных в одной конфигурации.Схема будет работать аналогично схеме затвора NAND.

Таблица истинности для ИЛИ-вентиль RS Flip Flop показана ниже:

| S | R | Q | Ǭ |

|---|---|---|---|

| 0 | 0 | Без изменений | Без изменений |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

Входы активны ВЫСОКОЕ, и недопустимое состояние существует, когда оба его входа находятся на логическом уровне «1».

триггеров OnePlus запущены в Индии за 1 099 рупий

OnePlus запустила ряд продуктов во время мероприятия по запуску серии OnePlus 9. Помимо трех смартфонов серии OnePlus 9 и первых умных часов бренда, к концу мероприятия OnePlus также представила пару игровых триггеров. Однако OnePlus не упомянул график их доступности.

Однако триггеры OnePlus теперь доступны в Индии и могут быть приобретены в магазине OnePlus за 1099 рупий.Триггеры были официально опубликованы в Твиттере генерального директора Пита Лау. Посмотрите это ниже.

Триггеры OnePlus: что вам нужно знатьМы разработали игровые триггеры OnePlus так, чтобы они были надежными, отзывчивыми, приятно щелкающими и, да, красивыми. Мы также позаботились о том, чтобы они работали со многими другими телефонами, потому что лучший дизайн продукта — это тот, который дает вам свободу делать собственный выбор. pic.twitter.com/hJNa4Dsa5s

— Пит Лау (@PeteLau) 21 апреля 2021 г.

Триггеры OnePlus имеют матово-черный дизайн с большой изогнутой кнопкой в верхней части, которую пользователи могут нажать, чтобы активировать любую клавишу в играх.Клипсовый дизайн триггеров, как и у ряда аксессуаров сторонних производителей, работает, защелкиваясь на вертикальном крае смартфона.

Триггеры OnePlus могут быть прикреплены к любому смартфону OnePlus или других производителей, если толщина рассматриваемого телефона составляет менее 11,5 мм. Сенсорное управление поможет пользователям получить более захватывающую обратную связь в играх по сравнению с сенсорным управлением на экране.

Триггеры OnePlus подходят для любого смартфона толщиной менее 11,5 мм (Источник изображения: Twitter / Pete Lau).Триггеры, которые имитируют функциональность «плечевых кнопок» на таких телефонах, как телефоны серии Asus ROG, также позволяют геймерам видеть большую часть экрана во время игры, поскольку они не закрывают дисплей пальцами.

Обратите внимание, что для использования триггеров OnePlus ваша игра должна поддерживать переназначаемые клавиши управления. Это часто встречается в играх жанра Battle Royale, таких как PUBG Mobile и Call of Duty Mobile. Триггеры OnePlus пока доступны только в Индии, и пока нет информации о международной доступности триггеров.

.