RS-триггер. Принцип работы RS-триггера. Схема :: SYL.ru

RS-триггер представляет собой простейший управляющий автомат, реализованный обычно в виде цифровой электронной схемы, относящийся к классу последовательностных схем. Как известно, в цифровой схемотехнике к функциональным устройствам последовательностного типа относятся регистры, счетчики, генераторы чисел и управляющие автоматы, включая триггеры разных видов.

Место триггеров в цифровой схемотехнике

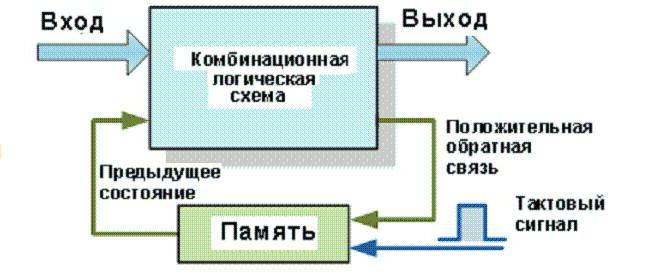

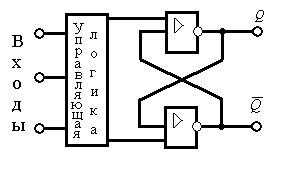

В отличие от комбинационных логических схем, которые изменяют состояние в зависимости от фактических сигналов, поданных на их входы в определенное время, последовательностные логические имеют некоторую форму присущей им встроенной «памяти», так что они могут учитывать как предыдущее, так и фактическое состояние их входов и выходов. Общая структурная схема последовательностного устройства показана ниже.

RS-триггер как цифровой управляющий автомат включает собственно память и комбинационную схему управления на типовых лигических элементах, реализующую его входной логический алгоритм. Если рассматривать эту схему применительно к простейшим схемам триггеров, то они не имеют структурно выделенной памяти в виде какой-то специализированной микросхемы или схемного узла. Память триггера существует на уровне функции, она словно встроена в алгоритм работы его комбинационной схемы управления. Проявлением этой «памяти» является так называемая бистабильность триггера, выходы которого могут находиться в одном из двух основных состояний: логической единицы (далее — 1) или логического нуля (далее — 0). Установившиеся значения своих выходов триггер запоминает («защелкивает» их) и сохраняет, пока не возникнет очередное изменение его входных сигналов.

Классификация

Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов:

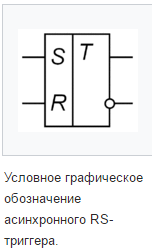

1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них.

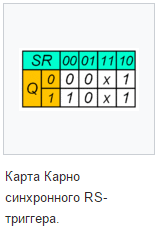

2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала.

3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала.

Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход.

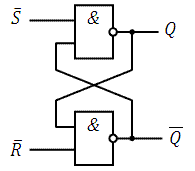

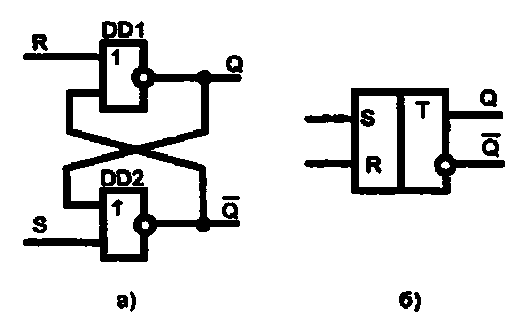

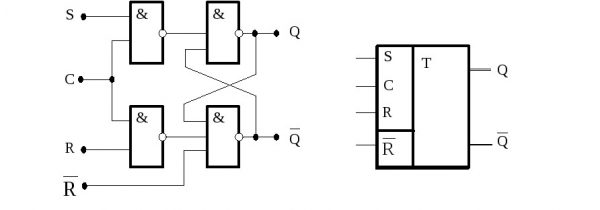

RS-триггер на логических элементах

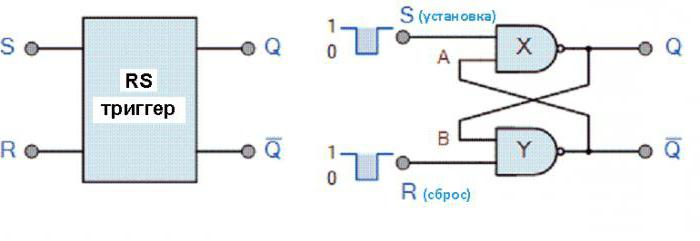

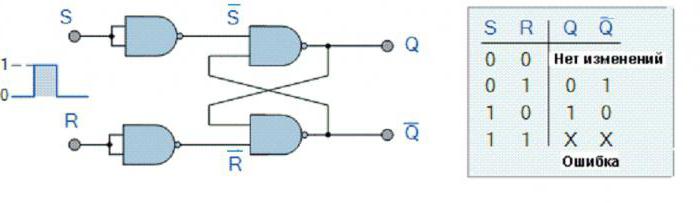

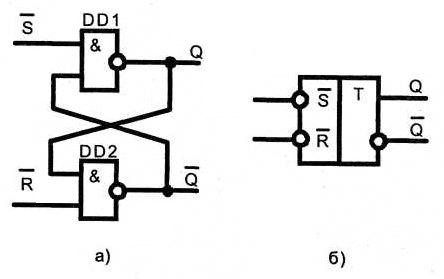

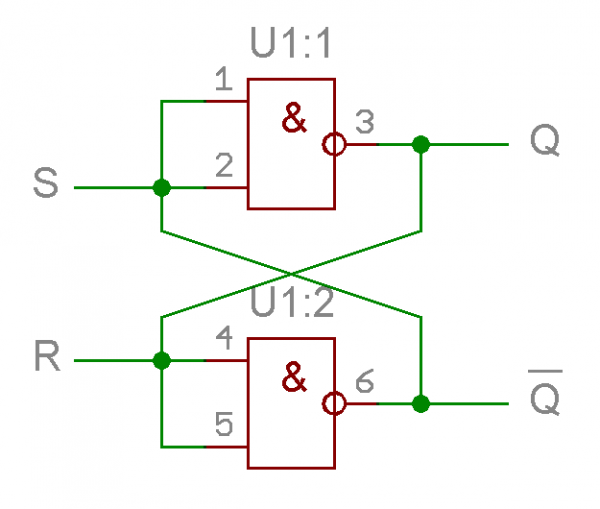

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

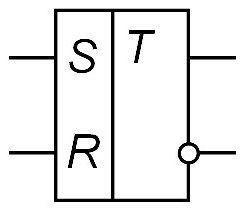

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

Состояние «Установлен»

Рассмотрим, как происходит работа RS-триггера в этом состоянии, задаваемом значениями R = 0 и S = 1. Поскольку на вход R элемента И-НЕ Y подан уровень 0, то Q̃ =1 (логика И-НЕ). С выхода Y сигнал Q̃ также подан обратно на элемент X (вход «A»). Поскольку S = A = 1, то Q = 0.

Если устанавливается R = 1, а вход S по-прежнему равен 1, то на входах Y имеем B = 0 и R = 1, а его выход Q̃ =1, т. е. он не изменился. Итак, если S = 1, то RS-схема триггера «защелкивается» в состоянии «Установлен» Q = 0 и Q̃ = 1, а смена сигнала R его не изменяет.

Состояние «Сброшен»

В этом втором устойчивом состоянии Q̃ = 0, а Q = 1, и задается оно входами R = 1 и S = 0. Поскольку у элемента Х вход S = 0, то его выход Q =1 (логика И-НЕ). Сигнал Q подается обратно на элемент Y (вход «В»), и так как R = B = 1, то Q̃ = 0.

Если S становится равен 1 при R = 1, то Q̃ остается равен лог 0, т. е. он не изменяется. Итак, при R =1 схема триггера снова «защелкивается» в состоянии «Сброшен» Q̃ = 0 и Q = 1, сохраняемом при любом сигнале S.

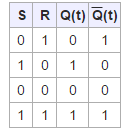

Сводим результаты в таблицу

Мы можем определить состояние сигналов Q и Q̃ по следующей таблице истинности:

| Состояние | S | R | Q | Q̃ | Описание |

| Установка | 1 | 0 | 0 | 1 | Выход Q̃ =1 |

| 1 | 1 | 0 | 1 | без изменений | |

| Сброс | 0 | 1 | 1 | 0 | Выход Q̃ =0 |

| 1 | 1 | 1 | 1 | без изменений | |

| Недопустимое | 0 | 0 | 1 | 1 | состояние ошибки |

Видно, что когда S = R = 1, то Q и Q̃ могут быть равны как 1, так и 0 (но не одновременно!) в зависимости от уровней входов S или R перед возникновением данного состояния выходов. Таким образом, при условии S = R = 1 нельзя изменить состояние выходов Q и Q̃. Оно может измениться только при смене уровня с 1 на 0 на одном из входов.

Значение S = R = 0 является нежелательным или недопустимым состоянием, и его следует избегать. Состояние S = R = 0 вызывает установку обоих выходов Q и Q̃ на уровне 1, в то время как состояние Q̃ всегда должно быть обратно Q. Результатом является то, что триггер теряет контроль над Q и Q̃, и если два входа теперь перейдут к состоянию 1, то схема становится неустойчивой и переключается в неопределенное состояние.

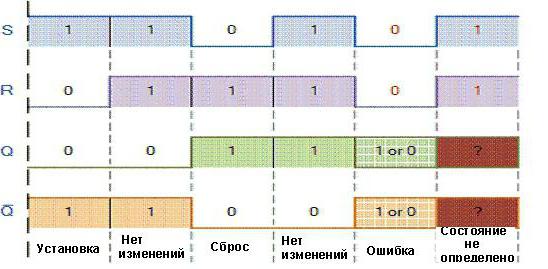

Диаграмма переключения RS-триггера

Сказанное в предыдущем разделе иллюстрирует следующая диаграмма переключения.

Как видно, при S = R = 0 возникает дисбаланс (неопределенность) состояния выходов. Он может привести к переключению одного из выходов быстрее, чем другого, в результате чего произойдет переключение триггера в то или иное состояние, которое может не совпадать с требуемым, и данные будут повреждены. Это неустойчивое состояние обычно называют мета-стабильным.

Таким образом, подобный триггер-защелка может быть переведен в состояние «Установлен» путем подачи 0 на его S-ввод (при наличии 1 на R-вводе) и переведен в состояние «Сброшен» подачей 0 на R-ввод (при наличии 1 на S-вводе). Триггер входит в неопределенное состояние (мета-стабильное), если на оба его входа одновременно подается уровень 0.

Переключение состояния выходов происходит с небольшой задержкой относительно изменения сигнала на одном из входов без использования тактового сигнала. Следовательно, рассмотренная выше схема представляет асинхронный RS-триггер.

Модифицируем схему триггера

Как мы видели выше, базовые элементы И-НЕ рассмотренного RS-триггера работают так, что при его установке Q̃ = 1 и Q = 0, а при его сбросе Q̃ = 0 и Q = 1, хотя логичнее было бы в первом состоянии иметь Q = 1, а во втором — Q = 0. При этом еще и получается, что смена состояний происходит при падении уровня сигнала с 1 до 0.

Таким образом, для правильной работы схемы триггера его входные сигналы нужно проинвертировать. Тогда переключения его состояний будут происходить при подаче положительных входных сигналов. Для этого в схему нужно добавить два дополнительных И-НЕ элемента, присоединенных как инверторы к S̃- и R̃-входам, как показано на рисунке ниже. Здесь на входах элементов И-НЕ уже представлены инверсные входные сигналы.

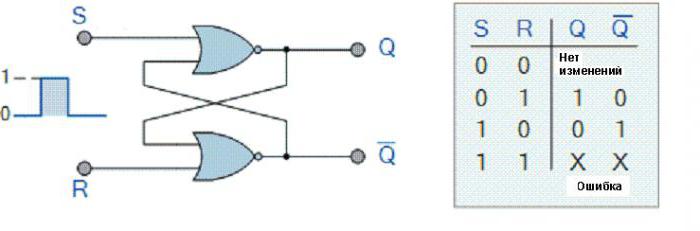

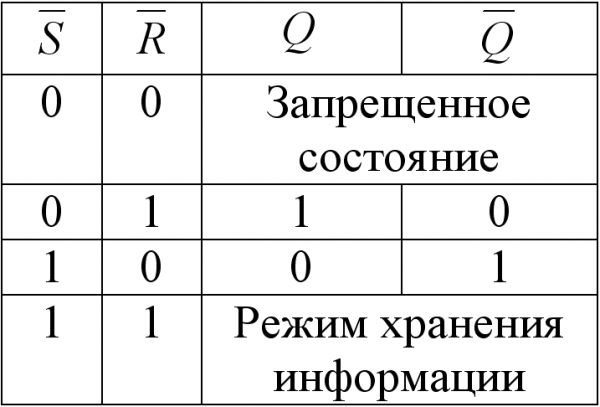

Так же, как и с использованием И-НЕ элементов, можно построить простой RS-триггер с использованием двух ИЛИ-НЕ элементов, соединенных по такой же схеме. Она будет работать аналогичным образом, как и рассмотренная выше схема И-НЕ. При этом активным является высокий уровень сигналов на входах, а недопустимое состояние возникает, когда на оба входа подан уровень логической «1», как это показано в таблице истинности на рисунке ниже.

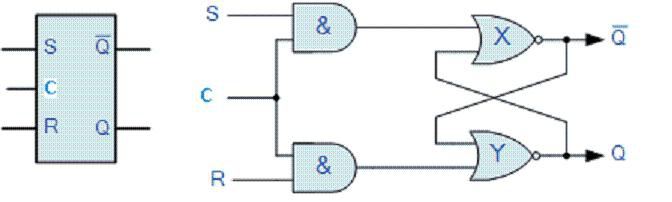

Как синхронизировать работу триггера

Иногда желательно в последовательностных логических схемах иметь бистабильный триггер, изменяющий свое состояние, когда соблюдены определенные условия, независимо от состояния S- или R-входов. Такая схема может быть создана подключением двухвходного элемента И последовательно с каждого входом триггера. Объединив два входа элементов И, получим новый вход триггера. Добавление его означает, что выходы Q и Q̃ изменяют состояние, когда сигнал на нем является высоким, и, следовательно, он может быть использован в качестве тактового C-ввода, как показано на рисунке ниже.

Когда сигнал на С-входе находится на уровне 0, то выходы двух элементов И — также на уровне 0 (логика элемента И), независимо от состояния двух входов S и R, а два выхода Q и Q̃ «защелкнуты» в последнем установившемся состоянии. Когда сигнал на С-входе изменяется на уровень 1, то схема отвечает как обычный бистабильный триггер, становясь прозрачной для установки и сброса состояний.

Этот дополнительный C-вход также может быть подключен к выходу генератора тактовой частоты синхронизации, образуя тогда синхронный RS-триггер. Таким образом, данная схема работает как стандартная бистабильная триггерная «защелка», но выходы активируются только тогда, когда уровень 1 подан на C-вход, и отключаются при появлении уровня логического нуля.

Регистры на триггерах

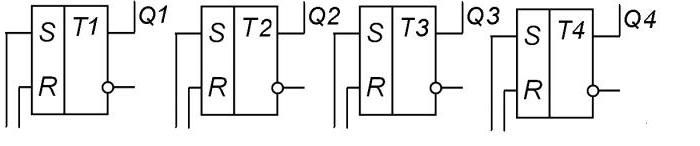

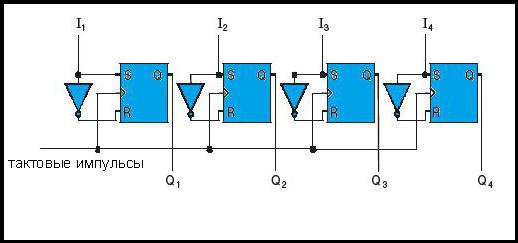

RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера.

Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2.

Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже.

Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи.

Эксперименты с RS-триггером.

Схемы RS-триггеров на микросхемах

После знакомства с принципом работы различных триггеров у начинающего радиолюбителя возникает естественное желание опробовать работу этих самых триггеров в «железе».

На практике изучение работы триггеров гораздо интересней и увлекательней, кроме того происходит знакомство с реальной элементной базой.

Далее будут рассмотрены несколько схем триггеров, выполненных на цифровых микросхемах так называемой жёсткой логики. Сами по себе схемы не являются завершёнными готовыми устройствами и служат лишь для наглядной демонстрации принципов работы RS-триггера.

Итак, начнём.

Для ускорения процесса сборки и тестирования схем применялась беспаечная макетная плата. С её помощью удаётся быстро сконфигурировать и изменить схему в соответствии с потребностями. Пайка, естественно, не применяется.

Схема RS-триггера на микросхеме К155ЛА3.

Данная схема уже приводилась на страницах сайта в статье про RS-триггер. Для её сборки потребуется сама микросхема К155ЛА3, два индикаторных светодиода разного цвета свечения (например, красный и синий), пара резисторов номиналом 330 Ом, а также стабилизированный блок питания с выходным напряжением 5 вольт. В принципе, подойдёт любой маломощный блок питания на 5 вольт.

Для дела сгодится даже 5-ти вольтовый зарядник от сотового телефона. Но стоит понимать, что не каждый зарядник держит стабильное напряжение. Оно может гулять в пределах 4,5 – 6 вольт. Поэтому всё-таки лучше использовать стабилизированный блок питания. При желании можно собрать блок питания своими руками. К выводу 14 микросхемы К155ЛА3 подключается «+» питания, а к 7 выводу «-» питания.

Как видим, схема очень простая и выполнена на логических элементах 2И-НЕ. Собранная схема имеет всего лишь два устойчивых состояния 0 или 1.

После того, как на схему будет подано напряжение питания, загорится один из светодиодов. В данном случае загорался синий светодиод, который подключен к инверсному выходу триггера (Q).

При однократном нажатии на кнопку Set (установка), RS-триггер устанавливается в единичное состояние. При этом должен засветиться тот светодиод, который подключен к так называемому прямому выходу Q

Это свидетельствует о том, что триггер «запомнил» 1 и выдал сигнал об этом на прямой выход Q.

Светодиод (синий), который же подключен к инверсному выходу Q, должен погаснуть. Инверсный – это значит обратный прямому. Если на прямом выходе 1, то на инверсном 0. При повторном нажатии на кнопку Set, состояние триггера не изменится – реагировать на нажатия кнопки он не будет. В этом и заключается основное свойство любого триггера – способность длительное время сохранять одно из двух состояний. По сути, это простейший

Чтобы сбросить RS-триггер в нуль (т.е. записать в триггер логический 0) нужно один раз нажать на кнопку Reset (сброс). При этом красный светодиод погаснет, а синий загорится. Повторные нажатия на кнопку Reset состояние триггера не изменят.

Показанную схему можно считать примитивной, так как собранный RS-триггер не имеет никакой защиты от помех, а сам триггер является одноступенчатым. Но зато в схеме применяется микросхема К155ЛА3, которая очень часто встречается в электронной аппаратуре и поэтому она легкодоступна.

Также стоит отметить, что на этой схеме выводы установки S, сброса R, прямого Q и инверсного выхода Q показаны условно – их можно поменять местами и суть работы схемы не изменится. Это всё потому, что схема выполнена на неспециализированной микросхеме. Далее же мы разберём пример реализации RS-триггера на специализированной микросхеме-триггере.

Схема RS-триггера на микросхеме КМ555ТМ2.

В данной схеме используется специализированная микросхема КМ555ТМ2, в составе которой 2 D-триггера. Эта микросхема выполнена в керамическом корпусе, поэтому в названии присутствует сокращение К

Как мы знаем, D-триггер несколько отличается от RS-триггера, но у него также присутствуют входы для установки (S) и сброса (R). Если не использовать вход данных (D) и тактирования (C), то на базе микросхемы КМ555ТМ2 легко собрать RS-триггер. Вот схема.

В схеме применён только один из двух D-триггеров микросхемы КМ555ТМ2. Второй D-триггер не используется. Его выводы никуда не подключаются.

Так как входы S и R микросхемы КМ555ТМ2 являются инверсными (отмечены кружком), то переключение триггера из одного устойчивого состояния в другое происходит при подаче на входы S и R логического 0.

Чтобы подать на входы 0, нужно просто соединить эти входы с минусовым проводом питания (с минусом «-»). Сделать это можно как с помощью специальных кнопок, например, тактовых, как на схеме, так и с помощью обычного проводника. Кнопками, конечно, это делать гораздо удобнее.

Жмём кнопку SB1 (Set) и устанавливаем RS-триггер в единицу. Засветится

А теперь жмём кнопку SB2 (Reset) и сбрасываем триггер в нуль. Засветится синий светодиод, который подключен к инверсному выходу триггера (Q).

Стоит отметить, что входы S и R у микросхемы КМ555ТМ2 являются приоритетными. Это значит, что сигналы на этих входах для триггера являются главными. Поэтому если на входе R нулевое состояние, то при любых сигналах на входах C и D состояние триггера не изменится. Это утверждение относится к работе D-триггера.

Если найти микросхемы К155ЛА3, КМ155ЛА3, КМ155ТМ2, К155ТМ2, К555ТМ2 и КМ555ТМ2 не удастся, то можно использовать зарубежные аналоги этих микросхем стандартной транзисторно-транзисторной логики (ТТЛ): 74LS74 (аналог К555ТМ2), SN7474N и SN7474J (аналоги К155ТМ2), SN7400N и SN7400J (аналоги К155ЛА3).

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

40.Одноступенчатый rs-триггер на элементах и–не.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

ВИДЫ ОДНОСТУПЕНЧАТЫХ ТРИГГЕРОВ:

RS-триггер асинхронный

.RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесенных во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

RS-триггеры иногда называют RS-фиксаторами

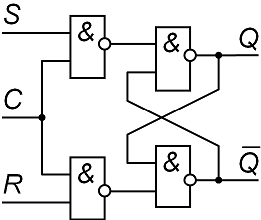

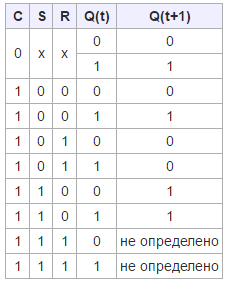

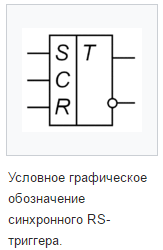

2. RS-триггер синхронный

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

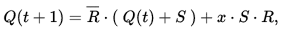

Алгоритм функционирования синхронного RS-триггера можно представить формулой

где x — неопределённое

состояние.

где x — неопределённое

состояние.

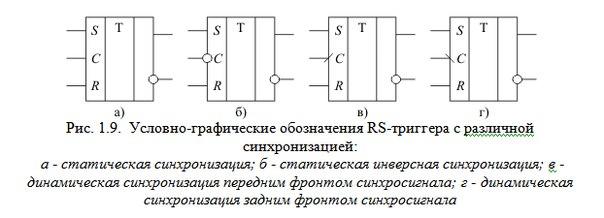

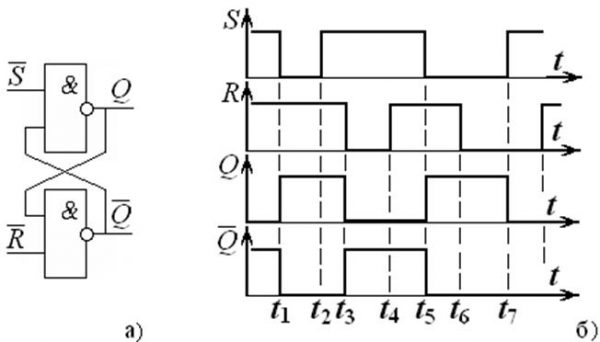

41. Синхронный одноступенчатый rs-триггер. Условно-графическое обозначение rs-триггера с различной синхронизацией. Временная диаграмма работы rs-триггера с различными типами синхронизации.

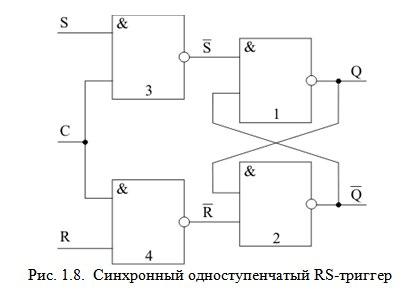

Синхронный одноступенчатый RS-триггер отличается от асинхронного наличием С-входа для синхронизирующих ( тактовых) импульсов. Синхронный триггер состоит из асинхронного — триггера и двух логических элементов на его входе.

Особенность одноступенчатых RS-триггеров — записываемая в них информация практически сразу ( лишь с небольшой задержкой, обусловленной временем срабатывания) появляется на выходах, что не всегда желательно.

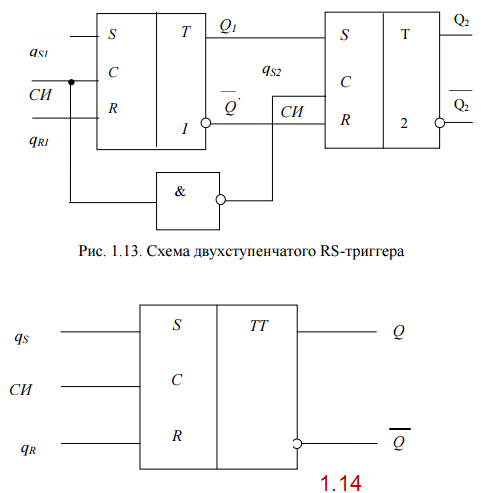

42. Двухступенчатый rs-триггер.

Двухступенчатый RS-триггер (рис. 1.13 и рис. 1.14) строится на основе двух одноступенчатых триггеров с прямой статической синхронизацией. Информация в первую ступень триггера (элемент 1) заносится во время действия высокого уровня синхросигнала. После того как синхросигнал на входе принимает низкое значение, элемент 1 переходит в режим хранения, а значение высокого сигнала на выходе инвертора 3 обеспечивает запись состояния триггера 1 в триггер 2. Идеализированная временная диаграмма работы двухступенчатого RS- триггера приведена на рис. 1.15

Следует отметить, что первая ступень представляет собой одноступенчатый триггер, реализующий заданную таблицу переходов, в то время как вторая ступень – это всегда одноступенчатый синхронный RS-триггер.

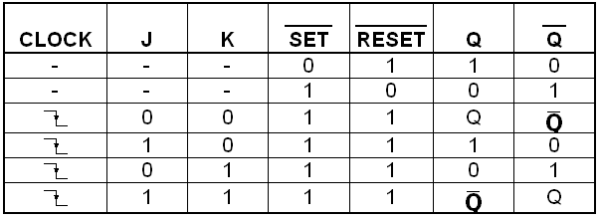

43.T-, JK-, D-триггеры.

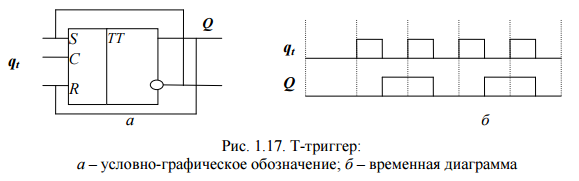

Т-триггер представляет собой триггер, имеющий один вход «Т», поступление единичного сигнала на который переводит Т- триггер в состояние, противоположное его исходному состоянию (фигурально говоря, по каждому входному сигналу триггер «кувыркается», меняя свое состояние на противоположное). На рис. 1.17 приведена реализация Т-триггера на базе двухтактного RS- триггера (а) и временная диаграмма его работы (б). Имеющиеся на схеме обратные связи создают ситуацию, при которой сигналы на входах R и S стремятся перевести триггер в состояние, противоположное текущему. Поэтому при приходе очередного сигнала qT триггер воспринимает сигналы, имеющиеся на его входах. Выходные сигналы триггера изменяются после снятия единичного сигнала на его входе qT, так как триггер двухтактный.

Т-триггер можно рассматривать как счетчик, считающий по модулю два количество импульсов, поступающих на его вход. Действительно, если в исходном состоянии триггер находится в «0», то при поступлении на его вход нечетного количества импульсов триггер будет находиться в «1», а при четном в– «0», что соответствует суммированию по модулю «2» количества поступающих импульсов.

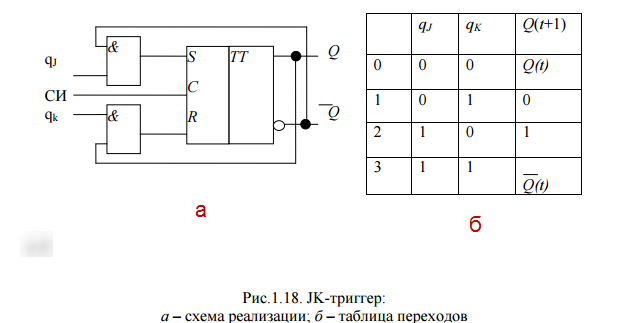

JK-триггер. Реализация JK-триггера и соответствующая таблица истинности приведена на рис. 1.18. Вход «J» – это вход установки «1», вход «K» – вход установки «0».

Из приведенной схемы видно, что сигналы qJили qK, стремящиеся установить триггер, соответственно, в «1» или «0», поступают на соответствующий вход «S» или «R» базового RS-триггера только тогда, когда его исходное состояние противоположно тому, в которое стремится перевести JK-триггер комбинация входных сигналов. В противном случае сигналы qJили qK на соответствующий вход S или R базового триггера не поступают. В связи с этим комбинация входных сигналов «1, 1» не является запретной, так как в этом случае на соответствующий вход базового RS-триггера поступит только тот сигнал, который стремится установить триггер в состояние, противоположное его исходному состоянию. Этот момент отражен в таблице истинности:при комбинации входных сигналов «1,1» триггер меняет исходное состояние, то есть работает как T-триггер

Таким образом, JK-триггер представляет собой универсальный триггер, объединяющий в себе свойства и RS-триггера и Т-триггера.

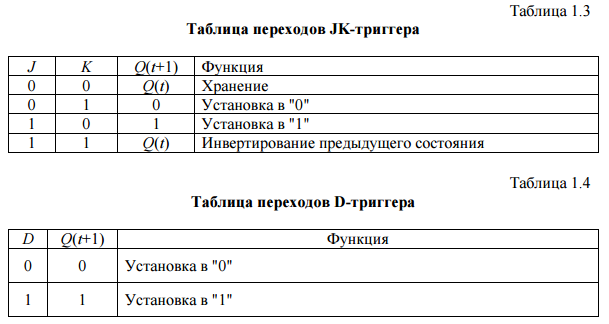

D-триггер. D-триггер по-другому называют элементом задержки.

Использование подачи сигнала установки «1» через логику НЕ на вход установки «0» приводит к тому, что на входы R и S базового RS-триггера подаются сигналы, имеющие противоположные значения.

Это означает, что, когда есть «1» на входе qD, на входах базового триггера будут сигналы: «1»–на входе S и «0»–на входе «R». Поэтому по переднему фронту сигнала СИ в триггере устанавливается «1», если есть «1» на входе qD, в противном случае в триггере будет установлен «0». Состояние, которое имеется у триггера в момент заднего фронта сигнала СИ, будет сохраняться («задерживаться») до поступления очередного сигнала синхронизации СИ. Таблицы переходов JK- и D- триггеров приведены в таблиц.1.3 и 1.4 соответственно.

_16Л_Триггеры

ТРИГГЕРЫ

ТРИГГЕРЫ

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер

имеет два выхода: прямой Q и

инверсный  . Состояние

триггера определяют по значению сигнала

на прямом выходе Q. Значения

сигналов на прямом и инверсном

выходах всегда противоположны.

. Состояние

триггера определяют по значению сигнала

на прямом выходе Q. Значения

сигналов на прямом и инверсном

выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

1. RS-триггеры ‘

Асинхронные RS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. Асинхронные RS-триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS-триггер

— это триггер с раздельной установкой

состояний

логического нуля и логической единицы.

Он имеет два информационных входа S и R.. По

входу S триггер

устанавливается в состояние Q=1 ( =0), по

входу R — в

состояние Q=0 (

=0), по

входу R — в

состояние Q=0 ( =1). В зависимости от логической структуры

асинхронные RS-триггеры

бывают с прямыми либо инверсными входами

и могут строиться

на двух логических элементах:

2ИЛИ-НЕ — триггер с прямыми входами; или

на элементах 2И-НЕ

— триггер с инверсными входами.

=1). В зависимости от логической структуры

асинхронные RS-триггеры

бывают с прямыми либо инверсными входами

и могут строиться

на двух логических элементах:

2ИЛИ-НЕ — триггер с прямыми входами; или

на элементах 2И-НЕ

— триггер с инверсными входами.

Асинхронный RS-триггер с прямыми входами на логических элементах 2ИЛИ-НЕ представлен на рисунке 2.

Рис.2.

Логические

элементы ИЛИ-НЕ с инвертированием

сигнала образуют петлю положительной

обратной связи.

При таком соединении логическая единица

на выходе

одного логического элемента (ЛЭ) поступает

на вход другого

ЛЭ и обеспечивает логический ноль

(инвертирование)

на его выходе. Логический ноль на выходе

ЛЭ, поступая

на вход другого, при инвертировании

дает логическую

1. Таким образом, выходы Q и  всегда

находятся в противоположных состояниях.

Соединение элементов

по данной схеме позволяет получить цепь

с двумя устойчивыми

состояниями.

всегда

находятся в противоположных состояниях.

Соединение элементов

по данной схеме позволяет получить цепь

с двумя устойчивыми

состояниями.

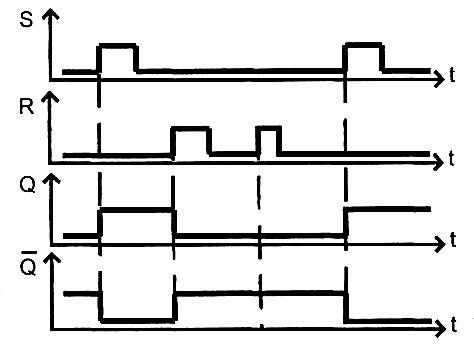

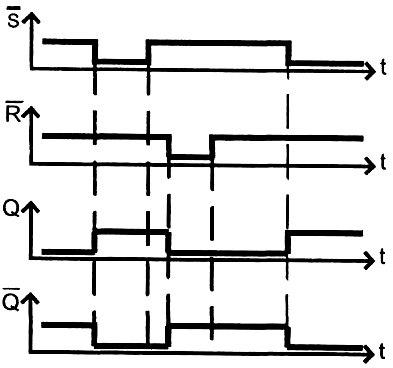

Временные диаграммы, характеризующие работу асинхронного RS-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для

элементов ИЛИ-НЕ активным является

высокий

уровень — логическая 1, поэтому в

режиме хранения данных на входы этого

триггера подаются нулевые значения R=S=0.

Установка триггера в нужное состояние

производится подачей на соответствующий

вход активного уровня единицы.

Одновременная подача единицы на оба

входа (R

и S)

приводит к неопределенности. На обоих

выходах Q и появляются

единицы, а после отключения входов

(S=R=0)

может установиться любое состояние.

Такая ситуация неопределенности не

допустима, поэтому комбинация S=R=1

считается запрещенной.

появляются

единицы, а после отключения входов

(S=R=0)

может установиться любое состояние.

Такая ситуация неопределенности не

допустима, поэтому комбинация S=R=1

считается запрещенной.

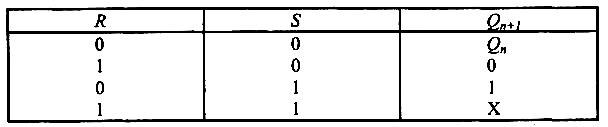

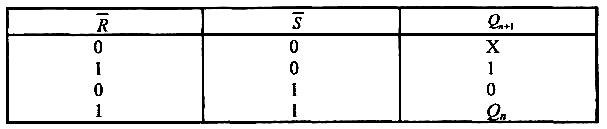

Функционирования триггера с прямыми входами на элементах 2ИЛИ-НЕ может быть отражено таблицей истинности

Асинхронный RS-триггер с инверсными входами на логических элементах 2И-НЕ представлен на рисунке 4.

Рис.4

Для этих ЛЭ логическая 1 является пассивным уровнем, поэтому сигнал R = S = 1 не влияет на состояние триггера и обеспечивает хранение предыдущего значения на выходах Qn+1= Qп. Для элементов И-НЕ активным является низкий уровень, т.е. логический 0.

Временные диаграммы работы асинхронного RS—триггера на элементах И-НЕ показаны на рис.5

Рис.5

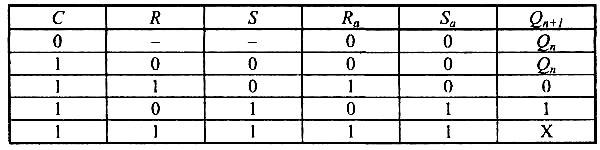

В таблице показано функционирование асинхронного RS-триггера в инверсными входами на элементах 2И-НЕ.

Таблица переходов RS-триггера на элементах 2И-НЕ

Знак

«X»

при  =

= =0 означает,

что такая комбинация

является запрещенной.

=0 означает,

что такая комбинация

является запрещенной.

Синхронный RS-триггер имеет дополнительный вход синхронизации, который также называют тактирующим входом. Синхронизирующий вход разрешает прием сигналов с информационных входов. При наличии синхросигнала происходит переключение триггера. При отсутствии сигнала на синхровходе информационные сигналы не влияют на состояние триггера.

Достоинство синхронных триггеров: они позволяют устранить влияние задержки распространения сигнала в различных частях схемы. Таким образом, достигается одновременный прием сигналов в заданные интервалы времени в разных точках схемы.

Синхронные триггеры бывают со статическим и динамическим управлением. При статическом управлении триггер реагирует на изменение информационных сигналов в течение всего времени действия синхросигналов. Поэтому изменение информационных сигналов в них возможно только при отсутствии сигнала на синхровходе.

В синхронных триггерах с динамическим управлением прием сигналов с информационных входов происходит в течение короткого фронта сигнала синхронизации. В остальное время информационные входы логически отключены и изменения сигналов на информационных входах не вызывают срабатываний синхронного триггера.

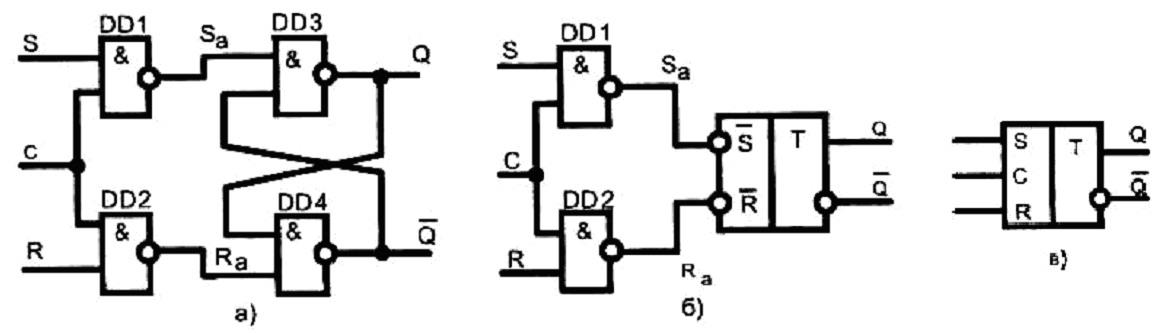

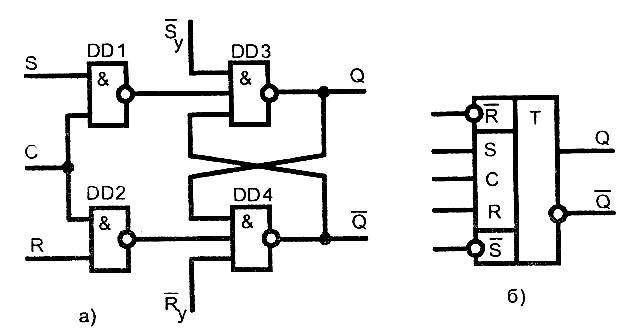

Логическая структура синхронного RS-триггера содержит асинхронный RS-триггер и дополнительную входную логическую схему, которая управляет его работой. На рис. 6 изображены схемы и обозначение синхронного RS-триггера с прямыми информационными и синхронизирующим входами. Такой триггер также называют RSТ-триггером, полагая вход С тактовым входом Т.

Рис.6

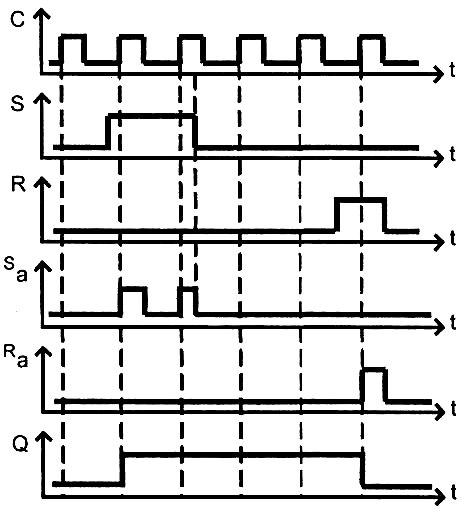

На входах кроме информационных сигналов R, S действует сигнал синхронизации С. Буквами Ra, Sa обозначены сигналы на входах асинхронного триггера. С помощью логических элементов DD1, DD2 обеспечивается передача входных сигналов на асинхронные триггеры. На рис. 7 изображены временные диаграммы работы синхронного RS-триггера с прямыми входами.

Рис.7

Таблица истинности синхронного RS-триггера

с прямыми входами (рис. 6, в)

При отсутствии синхронизирующего сигнала С=0 триггер не переключается независимо от входной информации R, S (прочерки в таблице). В этом режиме RST-триггер сохраняет ранее записанную в него информацию.

При С=1 триггер изменяет свое состояние в соответствии с поступившей на входы R и S информацией.

Триггеры могут дополнительно иметь установочные входы Ry, Sy,, сигналы которых непосредственно устанавливают триггер в заданное состояние независимо от синхросигналов (рис. 8).

Рис.8

При использовании для построения синхронного RS—триггера однотипных логических элементов (И-НЕ либо ИЛИ-НЕ) его синхронные либо асинхронные входы управляются различными активными логическими уровнями. В случае элементов И-НЕ для синхронных входов активным является сигнал логической единицы, а для асинхронных входов активным является сигнал логического 0. Условное графическое обозначение RS-триггера с прямыми информационными и инверсными установочными входами показано на рис. 8, б.

rs-триггер Википедия

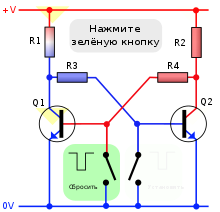

RS-триггер

RS-триггер

(R1, R2 = 1 kΩ, R3, R4 = 10 kΩ).

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном е.

При включении питания триггер непредсказуемо принимает (с равной или неравной вероятностью) одно из двух состояний. Это приводит к необходимости выполнять первоначальную установку триггера в требуемое исходное состояние, то есть подавать сигнал сброса на асинхронные входы триггеров, счётчиков, регистров, и т. д. (например, с помощью RC-цепочки), а также учитывать, что ячейки ОЗУ, построенного на триггерах (память статического типа), содержат после включения произвольную информацию.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно биполярные и полевые транзисторы), в прошлом — электромагнитные реле, электронные лампы. С появлением технологии производства микросхем малой и средней степени интеграции был освоен выпуск обширной номенклатуры триггеров в интегральном исполнении. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС). Используются, в основном, в вычислительной технике для организации компонентов вычислительных систем: регистров, счётчиков, процессоров, ОЗУ.

Логическая схема и принцип работы RS триггера в таблице истинности

Базовый строительный блок, который делает возможной компьютерную память, а также используется во многих последовательных логических устройствах является триггерной, или бистабильной, схемой. Только два взаимосвязанных логических входа составляют основную форму этой схемы, выход которой имеет два стабильных состояния. Когда схема запускается в какое-либо из них с помощью подходящего входного импульса, она будет «запоминать» это состояние до тех пор, пока оно не будет изменено дополнительным входным импульсом, или пока не отключится питание.

Логическая микросхема

Классификация последовательных схем

Последовательные схемы могут быть использованы для простых триггеров или для создания более сложных систем: устройств памяти, счетчиков, регистров сдвига. Они подразделяются на три основные категории:

- Асинхронные, меняющие статус при включении;

- Синхронные, согласованные с тактовым сигналом;

- Комбинированные, реагирующие на запуск импульсов.

Важно! Если схема зависит от внешнего входа, то она является асинхронной. Если состояния меняются в зависимости от тактового сигнала, то она синхронная. Для сохранения состояния присутствует обратная связь, когда частично сигнал с выхода идет опять на вход.

Что такое RS триггер

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

RS триггер

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние.

Таблица истинности

Работу триггера РС можно представить в таблице истинности:

- Q устанавливается на логическое значение 1, если применяется 0 на входе S;

- Изменение S-входа на единицу на выходную логику не влияет. 0-импульс был запомнен Q;

- Q сбрасывается на 0 с помощью логического 0, подаваемого на вход R;

- Когда R возвращается к 1, на Q запоминается 0.

Таблица истинности

Для условий 2-й и 3-ей строки таблицы Q̃ является величиной, обратной Q. Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

В последней строке на обоих входах присутствует логическая единица, выходы Q̃ и Q будут находиться в противоположных состояниях, но не ясно, какими конкретно значениями будут обладать. Они будут соответствовать запоминаемым с последнего входного импульса.

Помимо применения логики И-НЕ, можно построить простые триггеры, используя два перекрестно соединенных вентиля И-ИЛИ. Схема работает аналогично. Только запрещенное состояние будет при наличии обоих входных сигналов, равных единице.

Временные диаграммы

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

JK триггер

Другие широко распространенные виды логических схем – JK, D и Т, которые являются разработками RS триггера на логических элементах.

Недостатки схемы И-НЕ РС триггера:

- Необходимость избегать условия, когда оба входных сигнала равны 0;

- При изменениях состояния R и S, имеющих единичный входной сигнал, правильное блокирующее действие не всегда происходит.

Для преодоления этих недостатков была разработана схема JK триггера. Его входы являются теми же R и S, но им присвоены буквы J и K по имени изобретателя схемы, чтобы отличить от других триггеров. JK схема отличается от RS триггера тем, что она не имеет неопределенных или запрещенных входных статусов.

JK триггер

В JK добавлена входная схема синхронизации, предотвращающая неопределенное условие вывода, которое может случиться, если R и S равны единице. Поэтому в наличии четыре возможных комбинации ввода: 1, 0, «без изменений» и «переключение». Вход J соответствует S, а K – R. Кроме того, для каждого вентиля имеется третий вход. На выходе остаются Q̃ и Q.

Перекрестная связь RS триггера позволяет использовать ранее неопределенные условия работы триггера, когда оба входных сигнала равны 1, для создания «переключателя», так как два входа могут быть блокированы.

Схема JK – это триггер SR с обратной связью, который позволяет только одному из его терминалов (SET или RESET) быть активным в любой момент времени, тем самым устраняя недопустимое условие:

- Если активен терминал SET, вход J блокируется статусом 0 (Q̃) через нижний логический элемент И-НЕ;

- Если в действии терминал RESET, вход К заблокирован статусом 0 через верхний вентиль И-НЕ.

Так как Q̃ и Q всегда разные, они могут использоваться для манипулирования входом. Для JK триггера таблица истинности принимает следующий вид.

Таблица истинности JK триггера

Когда оба входа J и K имеют единицу на входе при высоком тактовом импульсе, схема может переключаться из состояния SET в RESET и наоборот.

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер. При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Видео

Оцените статью:Триггер — Национальная библиотека им. Н. Э. Баумана

Материал из Национальной библиотеки им. Н. Э. Баумана

Последнее изменение этой страницы: 17:36, 7 января 2015.

Триггер — это запоминающее устройство, хранящее одно из двух состояний — либо 0 либо 1.

RS — триггер

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

Рис. 1.1. RS-триггер с прямыми информационными входами.S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Рис. 1.2. RS-триггер с инверсными информационными входами.Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

Рис. 1.3. Классическая реализация RS-триггера.Таблица истинности:

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 0 | 0 | 0 | 0 | 1 | режим хранения нуля |

| 0 | 0 | 1 | 1 | 0 | режим хранения единицы |

| 1 | 0 | 0 | 1 | 0 | установка в состояние 1 |

| 1 | 0 | 1 | 1 | 0 | режим хранения 1 |

| 0 | 1 | 0 | 0 | 1 | режим хранения нуля |

| 0 | 1 | 1 | 0 | 1 | сброс в ноль |

| 1 | 1 | 0 | 0 | 0 | запрещено |

| 1 | 1 | 1 | 0 | 0 | запрещено |

Когда оба входа активны, то Q=Q¯=0{\displaystyle Q={\overline {Q}}=0}. Но, по определению, они противоположны ⇒R=S=1⇒{\displaystyle \Rightarrow R=S=1\Rightarrow } запрещенное состояние, но оно однозначно определено. Эта особенность используется для ускорения переключения схемы.

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Рис. 1.4. Временные диаграммы RS-триггера.Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

Рис. 1.5. Использование RS-триггера в качестве генератора случайных чисел. Рис. 1.6. Временные диаграммыДругая реализация RS-триггера

Также RS-триггер можно реализовать на базе элеметов «И-НЕ» (рис. 6). Входы у такой реализации — инверсные.

Рис. 1.7. Реализация RS-триггера на базе элементов «И-НЕ».Синхронный RS-триггер

Добавляется вход синхронизации С (основное отличие от асинхронных триггеров, описанных выше). Логика работы — активный вход синхронизации разрешает работу триггера. При неактивном входе синхронизации триггер не реагирует на входные значения. То есть:

- C=0; R,S — любые. Q(t+1)=Q(t)

- C=1

- R=S=0 — хранение

- S=0 R=1 — сброс (установка нуля)

- S=1 R=0 — установка единицы

- S=1 R=1 — запрещенное состояние

Схема синхронного RS-триггера

Рис. 2.1. Схема реализации синхронного RS-триггера.Синхронный JK-триггер

Основное преимущество данного триггера — у него нет запрещенного состояния.

Рис. 3.1. Условное обозначение синхронного JK-триггера.Логика работы:

- C=1

- J=0 K=1 Q(t+1)=0

- J=0 K=0 Q(t+1)=Q(t)

- J=1 K=0 Q(t+1)=1

- J=1 K=1 Q(t+1)=no Q(t)

- C=0 — режим хранения

Схема JK-триггера

Рис. 3.2. Схема JK-триггера и временные диаграммы его работы. Рис. 3.3. Временные диаграммы.Считается, что значения на выходе изменяются одновременно. Записать в триггер можно только изменяющееся значение, хранимое в триггере значение — нельзя.

Конкретная реализация синхронного JK-триггера

Рис. 3.4. Конкретная реализация JK-триггера и временные диаграммы его работы. Рис. 3.5. Временные диаграммы.Если длительность управляющих сигналов больше времени переключения триггера — получаем автоколебательный режим (при наличии двух единиц на входах).

При J=K=1{\displaystyle J=K=1\,\!} необходимо подать на вход сихронизирующий импульс, не превышая время переключения (время ПП) внутри JK-триггера.

tJK=2tNOR+tAND{\displaystyle t_{JK}=2t_{NOR}+t_{AND}\,\!}

Окончание автоколебательного процесса определяется длительностью сигнала синхронизации и времени установки триггера.

D-триггер

Является синхронным триггером

- если С=0, то Q(t+1)=Q(t) — режим хранения

- если С=1, то Q(t+1)=D

Таким образом триггер сохраняет значение поданное на вход D.

Рис. 4.1. Условное обозначение D-триггера, его реализация и временные диаграммы его работы. Рис. 4.2. Временные диаграммы.При C=0{\displaystyle C=0} и R=S=1{\displaystyle R=S=1} возникает запрещенное состояние.

Предназначен для хранения мнформации на входе D{\displaystyle D} при C=1{\displaystyle C=1}

Т-триггер

Рис. 5.1. Условное обозначение T-триггера.Триггер при подаче сигнала синхронизации меняет значение на выходе на противоположное. Может иметь вход стробирования Е (при Е=0 триггер не изменяет значение на выходе ни при какхи условиях).

Рис. 5.2. Схема T-триггера.Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим.

Может быть реализован и на синхронном RS-триггере (рис. 5.3).

Рис. 5.3. Реализация T-триггера на базе RS-триггера.Двухступенчатые триггеры

Короткие импульсы синхронизации (менее времени срабатывания триггера) не совсем удобны для управления триггерами. Как вариант модернизации существуют двухступенчатые триггеры. Они реагируют на смену значения на входе синхронизации (фронт:0-1, либо спад:1-0).

В основе — RS триггер.

Рис. 6.1. Общий вид двухступенчатых триггеров.Перезапись из первой во вторую ступень происходит при смене значения входа синхронизации.

- 1-я ступень — ведущая (master).

- 2-я ступень — ведомая (slave).

Двухступенчатый синхронный RS-триггер

Рис. 6.2. Схема двухступенчатого синхронного RS-триггера.Запись происходит по спаду (изменение с 1 до 0). Основа — два обычных RS-триггера. Запись в первый триггер происходит при С=1 (второй триггер в это время в режиме хранения). При смене значения С на С=0 происходит запись значений из первого триггера во второй. Таким образом запись происходит по спаду сигнала синхронизации С (это обозначается наклонной чертой на входе синхронизации в обозначении триггера на схеме — см. рис 6.3).

Рис. 6.3. Условное обозначение двухступенчатого синхронного RS-триггера.Двухступенчатый D-триггер

Рис. 6.4. Схема и условное обозначение двухступенчатого D-триггера.Логика работы та же что и у RS-триггера. С=1 — запись в первый триггер, С=0 — запись из первого во второй (запись по спаду).

Двухступенчатый JK-триггер

Рис. 6.5. Схема двухступенчатого JK-триггера.Поведение аналогично предыдущим триггерам кроме состояния J=1 K=1. Рассмотрим это состояние. При J=1K=1{\displaystyle J=1K=1} и C=1{\displaystyle C=1} вознмкает автоколебательный процесс: 0, 1, 0, 1 и т.д. JK-триггер должен переключаться в состояние, противоположное тому, в котором находится 2й триггер, т.е. используются только внутренние обратные связи (ОС).

Для устранения этого недостатка можно модифицировать схему (рис. 6.6)

Рис. 6.6. Схема двухступенчатого JK-триггера (без автоколебательного процесса).Особенность схемы — наличие глубокой обратной связи (а именно, связи выходов второй ступени со входами первой ступени). В результате в триггер первой ступени записывыаются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно).

Двухступенчатые триггеры изменяют свои значения по спаду/фронту синхроимпульса, поэтому длительность импульсов не важна.

Приведенные выше (рис. 6.5 и 6.6) схемы являются базовыми, теперь следует рассмотреть конкретные реализации.

Рис. 6.7. Реализация двухступенчатого JK-триггера на базе элементов «И-НЕ».- D1-D2 — схема управления первой ступенью;

- D3-D4 — элементы памяти первой ступени; (D1-D4 в сумме — синхронный RS-триггер)

- D5-D6 — схема управления второй ступенью;

- D7-D8 — элементы памяти второй ступени; (D5-D8 в сумме — синхронный RS-триггер)

На входы D1 и D2 идет обратная связь с выходов D7, D8. Запись происходит при условии, что на выходах D1 и D2 одновременно присутствуют «1» (запись во вторую ступень). Запись в первую ступень происходит при противоположных значениях на выходах D7, D8. Запись в первую ступень происходит либо при C=1{\displaystyle C=1}, либо при J=K=0{\displaystyle J=K=0}. Перезапись — при C=0{\displaystyle C=0} (на выходах D1 и D2 — единицы).

Еще эту схему можно получить на базе RS-триггеров (вывод схемы — на рис. 6.8)

Рис. 6.8. Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).Универсальные триггеры

Рис. 7.1. Пример универсального триггера.При необходимости в схему можно ввести асинхронные входы установки в 0 и 1 — они устанавливают схему независимо от схемы управления. Триггер сч такими входами называется универсальным (т.е. он имеет и синхронные. и асинхронные входы установки). Асинхронные входы нужны для инициализации. Пример — рис 7.1, вход Reset переустановка всех компонентов схемы в начальное состояние. В режиме хранения требуется реагирование на синхронные входы (на их значения). При режиме записи — приоритет у асинхронных входов.

Универсальный JK-триггер

Рис. 7.2. Обозначение универсального JK-триггера.Имеет как синхронные, так и асинхронные входы установки. Конъюнкции D1 и D2 могут быть и 3хвходовыми, и 6-тивходовыми, а могут иметь и большую размерность, следовательнео, вместо одного сигнала J приходят несколько сигналов, объединенных конъюнкциями. Другими словами, на входе появляется «1», если на всех J — «1». Для входа K ситуация аналогичная.

Ступенчатый D-триггер

Классическая схема ступенчатого D-триггера представлена на рисунке 8.1.

Рис. 8.1. Разработка ступенчатого D-триггера.Состоит из трех асинхронных RS-триггеров (состоят из D1-D2, D3-D4, D5-D6 соответственно). Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

T3{\displaystyle T_{3}\,} — с инверсными входами (рем хранение — оба значения равны «1»). Если C=0{\displaystyle C=0\,}, то T2=T3=1{\displaystyle T_{2}=T_{3}=1\,}, то есть при C=0T3=1{\displaystyle C=0T_{3}=1\,}, а при C=1{\displaystyle C=1\,} T3{\displaystyle T_{3}\,} определяется тем, что подается на вход D.

При C=0,D=0{\displaystyle C=0,D=0\,} в T1{\displaystyle T_{1}\,} записывается некоторое значение, а T2{\displaystyle T_{2}\,} находится в запрещенном состоянии (две «1»).

Если при C=1{\displaystyle C=1\,} T2=1{\displaystyle T_{2}=1\,} и T3=0{\displaystyle T_{3}=0\,}, то произойдет переход в режим записи и проихойдет запись «0» во вторую ступень.

Рассмотрим случай, когда C=0,D=1{\displaystyle C=0,D=1\,}. Пусть D4=0{\displaystyle D4=0\,}, вход D4=0{\displaystyle D4=0\,}, тогда D1=1{\displaystyle D1=1\,}, можно наблюдать противоположную картину: T2{\displaystyle T_{2}\,} находится в режиме записи значения, а T1{\displaystyle T_{1}\,} — в запрещенном состоянии.

Рис. 8.2. Условное обозначение ступенчатого D-триггера.При переключении C из «0» в «1» на D3 происходит то же изменение, что и на D2 — переход из 1 в 0. Тогда T3{\displaystyle T_{3}\,} находится в режиме записи логической единицы:

(0)Q→1{\displaystyle (0)Q\rightarrow 1} (1)Q¯→0{\displaystyle (1){\bar {Q}}\rightarrow 0}При C=1{\displaystyle C=1\,} значение на входе D поменяется: 1→0{\displaystyle 1\rightarrow 0\,}, выход D4 установится в значение логической «1», поэтому D1{\displaystyle D1\,} станет равным 1 (его значение на выходе не меняется, на D2 — то же самое (только там — логический 0), поэтому значение на выходе D3 не меняется за счет D1 и D2).

При C=1{\displaystyle C=1\,} значение на входе D изменяется в порядке 1→0→1{\displaystyle 1\rightarrow 0\rightarrow 1\,}, значение D3 меняться не будет. Следовательно, при C=0{\displaystyle C=0\,} на выходе значение не будет меняться, при C=1{\displaystyle C=1\,} значение навыходе тоже не меняется. Таким образом, запись производится при переключении с 0 на 1 (по фронту).

- Первый триггер — для фиксации того, что хотим записать «0»;

- Второй триггер — для фиксации того, что хотим записать «1».

В итоге, при C:0→1{\displaystyle C:0\rightarrow 1} происходит запись, то есть переключение в другое состояние (или в запрещенное состояние).

Рис. 8.3. Преобразование ступенчатого D-триггера в универсальный. Рис. 8.4. Условное графическое обозначение универсального D-триггера.Можно сделать из данного триггера универсальный (рис 8.3). Для этого необходимо добавить асинхронные входы во вторую и первую ступени (для того, чтобы не получать запрещенное состояние только при наличии (1)S¯{\displaystyle (1){\bar {S}}} и (1)R¯{\displaystyle (1){\bar {R}}} во второй ступени). Устанавливаем (1)S¯{\displaystyle (1){\bar {S}}} и (1)R¯{\displaystyle (1){\bar {R}}} на D1 и D4, чтобы не изменять выход в режиме хранения (при C=0{\displaystyle C=0\,} — на D2 и D3). Условное изображение полученного триггера приведено на рисунке 8.4.