JK-триггер. Принцип работы, фунцкциональные схемы, таблицы истинности

Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

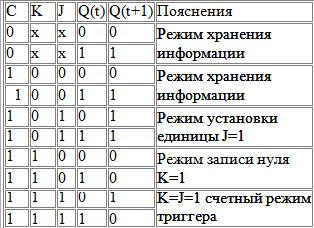

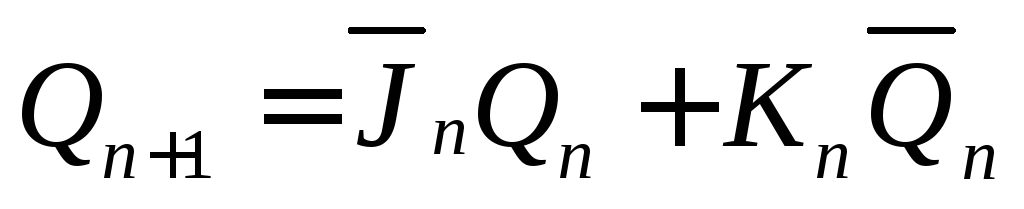

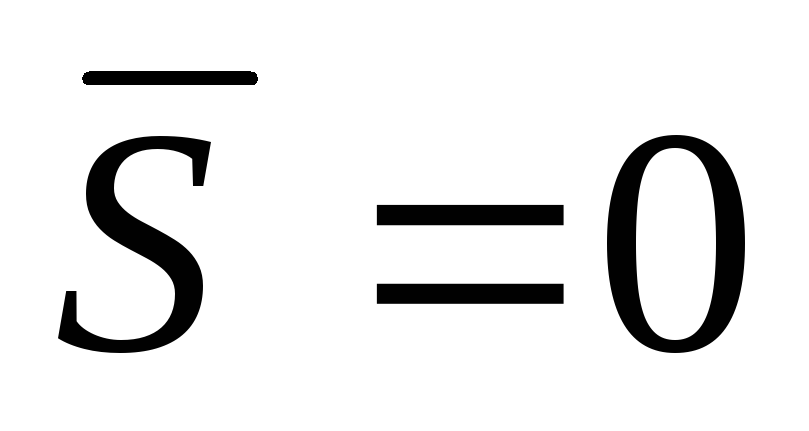

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

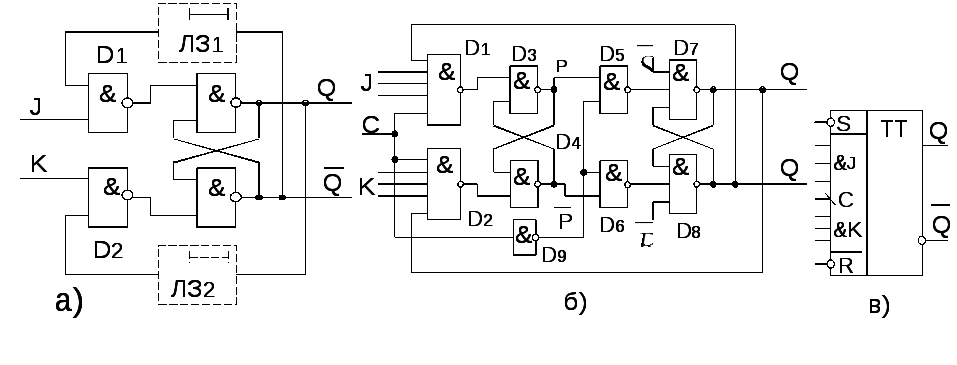

Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными.

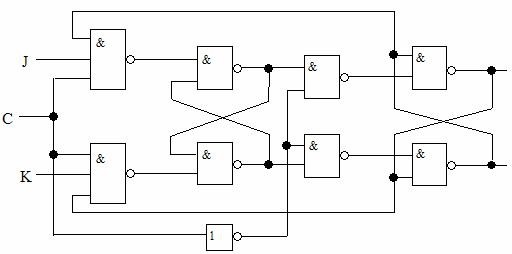

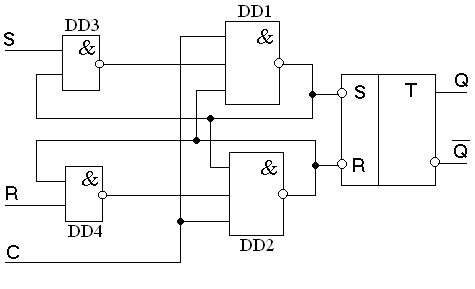

Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени.

Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q’ — логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q’ равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля.

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.

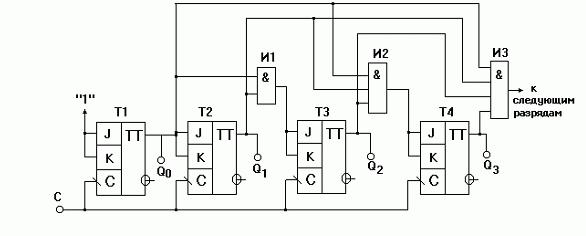

Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И.

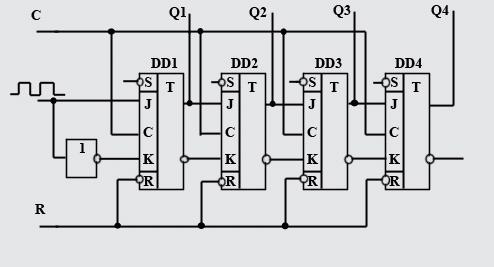

Также такие триггеры нашли применение при конструировании сдвигающих регистров.

Регистры сдвига – это узлы, выполняющие смещение двоичной информации вправо и влево по регистру в зависимости от управляющих сигналов.

Jk – триггеры

JK – триггер – это схема с двумя устойчивыми выходными состояниями и двумя входами J и К (Рисунок 51.а). Подобно RS – триггеру, в JK – триггере входы J и K это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от RS – триггера, в JK – триггере наличие J=K=1 приводит к переходу выхода Q триггера в противоположное состояние. Условие функционирования JK – триггера описывается функцией:

Рисунок 51 JK – триггеры: а) асинхронные; б) тактируемые фронтом.

Триггер JK –типа называют универсальным потому, что на его основе с помощью несложных коммутационных преобразований можно получить RS и Т – триггеры, а если между входами J и K включить инвертор, то получится схема D – триггера.

Недостатком этой схемы является зависимость работы схемы от длительности тактового импульса. Импульс должен быть коротким и должен закончиться до завершения процесса переключения триггера. Для ослабления требования к длительности тактового импульса в цепи обратных связей можно включить элементы задержки, как показано на рисунке 51,а пунктиром. Однако этот путь не всегда является целесообразным.

Разработаны и применяются в основном в интегральном исполнении JK – триггеры, тактируемые фронтом тактовых импульсов, которые не чувствительны к длительности тактовых импульсов.

JK – триггеры, тактируемые фронтом, строятся по схеме MS (master – slave то есть мастер – помощник). В схеме имеется два триггера: основной D1…D4, помощник D5….D8 и цепь, разделяющая их – D9 (Рисунок 51,б).

Триггер работает

следующим образом. Пусть в исходном

состоянии Q=0,

а  При отсутствии тактового импульса

(С=0), вентилиD1

и D2

закрыты вне зависимости от сигналов

на остальных входах.

При отсутствии тактового импульса

(С=0), вентилиD1

и D2

закрыты вне зависимости от сигналов

на остальных входах.

Пусть J=1,

тогда с приходом тактового импульса

С=1, D1

откроется, а D2

останется закрытым. Элементы D5

и D6

закроются сигналом

Несмотря на то, что на одном из входов D5 действует сигнал «1», а на одном из входов D6 – «0», они не изменят состояние вспомогательного триггера, так как на других входах элементов D5 и D6 действует сигнал лог «0» с инвертора D9.

По окончании

действия тактового импульса, появится

сигнал лог. «1» на вторых входах

вентилей D5,

D6,

а вентили D1

и D2

закроются. Так как основной триггер

находится в состоянии «1», то откроется

D5

и информация запишется во вспомогательный

триггер (Q=1,  ).

).

Cовершенно аналогично сигнал «1», поданный на вход К, установит триггер в состояние «0».

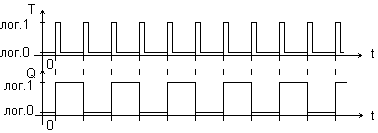

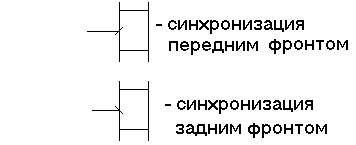

Таким образом, в триггере данного типа изменение выходного сигнала происходит только в моменты, когда потенциал «С» переходит из «1» в «0». Поэтому говорят, что эти триггеры тактируются срезом (или фронтом) в отличие от триггеров, тактируемых потенциалом.

Условное графическое обозначение триггера приведено на рисунке 51,в.

Если соединить

вместе входы J

и K,

то JK

– триггер превратится в Т – триггер.

Пусть триггер находится в исходном

состоянии ( ).

При подачеJ=K=1

и С=1, вентиль D1

будет закрыт сигналом «0» с выхода

).

При подачеJ=K=1

и С=1, вентиль D1

будет закрыт сигналом «0» с выхода  .

Так как открывается только вентильD2,

то триггер установится в в нулевое

состояние

.

Так как открывается только вентильD2,

то триггер установится в в нулевое

состояние

Микросхемы.

Микросхемы ТТЛ (74…).

На рисунке показана схема самого распространенного логического элемента — основы микросхем серии К155 и ее зарубежного аналога — серии 74. Эти серии принято называть стандартными (СТТЛ). Логический элемент микросхем серии К155 имеет среднее быстродействие tзд,р,ср.= 13 нс. и среднее значение тока потребления Iпот = 1,5…2 мА. Таким образом, энергия, затрачиваемая этим элементом на перенос одного бита информации, примерно 100 пДж.

Для обеспечения выходного напряжения высокого уровня U1вых. 2,5 В в схему на рисунке потребовалось добавить диод сдвига уровня VD4, падение напряжения на котором равно 0,7 В. Таким способом была реализована совместимость различных серий ТТЛ по логическим уровням. Микросхемы на основе инвертора, показанного на рисунке (серии К155, К555, К1533, К1531, К134, К131, К531), имеют очень большую номенклатуру и широко применяются.

| Параметр | Нагрузка | |||||

|---|---|---|---|---|---|---|

| Российские | Зарубежные | Pпот. мВт. | tзд.р. нс | Эпот. пДж. | Cн. пФ. | Rн. кОм. |

| К155 КМ155 | 74 | 10 | 9 | 90 | 15 | 0,4 |

| К134 | 74L | 1 | 33 | 33 | 50 | 4 |

| К131 | 74H | 22 | 132 | 25 | 0,28 | |

| К555 | 74LS | 2 | 9,5 | 19 | 15 | 2 |

| К531 | 74S | 19 | 3 | 57 | 15 | 0,28 |

| К1533 | 74ALS | 1,2 | 4 | 4,8 | 15 | 2 |

| К1531 | 74F | 4 | 3 | 12 | 15 | 0,28 |

При совместном использовании микросхем ТТЛ высокоскоростных, стандартных и микромощных следует учитывать, что микросхемы серии К531 дают увеличенный уровень помех по шинам питания из-за больших по силе и коротких по времени импульсов сквозного тока короткого замыкания выходных транзисторов логических элементов. При совместном применении микросхем серий К155 и К555 помехи невелики.

| Нагружаемый выход |

Число входов-нагрузок из серий | ||

|---|---|---|---|

| К555 (74LS) | К155 (74) | К531 (74S) | |

| К155, КM155, (74) | 40 | 10 | |

| К155, КM155, (74), буферная | 60 | 30 | 24 |

| К555 (74LS) | 20 | 5 | 4 |

| К555 (74LS), буферная | 60 | 15 | 12 |

| К531 (74S) | 50 | 12 | 10 |

| К531 (74S), буферная | 150 | 37 | 30 |

Выходы однокристальных, т. е. расположенных в одном корпусе, логических элементов ТТЛ, можно соединять вместе. При этом надо учитывать, что импульсная помеха от сквозного тока по проводу питания пропорционально возрастет. Реально на печатной плате остаются неиспользованные входы и даже микросхемы (часто их специально «закладывают про запас») Такие входы логического элемента можно соединять вместе, при этом ток I

| Параметр | Условия измерения | К155 | К531 | К1531 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Мин. | Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Макс. | ||

| U1вх, В схема |

U1вх или U0вх Присутствуют на всех входах | 2 | 2 | 2 | 2 | |||||||

| U0вх, В схема |

0,8 | 0,8 | 0,8 | |||||||||

| U0вых, В схема | Uи.п.= 4,5 В | 0,4 | 0,35 | 0,5 | 0,5 | 0,5 | ||||||

| I0вых= 16 мА | I0вых= 8 мА | I0вых= 20 мА | ||||||||||

| U1вых, В схема |

Uи.п.= 4,5 В | 2,4 | 3,5 | 2,7 | 3,4 | 2,7 | 3,4 | 2,7 | ||||

| I1вых= -0,8 мА | I1вых= -0,4 мА | I1вых= -1 мА | ||||||||||

| I1вых, мкА с ОК схема | U1и.п.= 4,5 В, U1вых=5,5 В | 250 | 100 | 250 | ||||||||

| I1вых, мкА Состояние Z схема |

U1и.п.= 5,5 В, U1вых= 2,4 В на входе разрешения Е1 Uвх= 2 В | 40 | 20 | 50 | ||||||||

| I0вых, мкА Состояние Z схема |

U1и.п.= 5,5 В, Uвых= 0,4 В, Uвх= 2 В | -40 | -20 | -50 | ||||||||

| I1вх, мкА схема | U1и.п.= 5,5 В, U1вх= 2,7 В | 40 | 20 | 50 | 20 | |||||||

| I1вх, max, мА | U1и.п.= 5,5 В, U1вх= 10 В | 1 | 0,1 | 1 | 0,1 | |||||||

| I0вх, мА схема |

U1и.п.= 5,5 В, U0вх= 0,4 В | -1,6 | -0,4 | -2,0 | -0,6 | |||||||

| Iк.з., мА | U1и.п.= 5,5 В, U0вых= 0 В | -18 | -55 | -100 | -100 | -60 | -150 | |||||

Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ]2.5.3. JK-триггеры

JK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JK-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

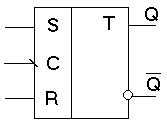

Простейший JK-триггер можно получить из синхронного RS-триггера с динамическим управлением, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний (рис. 2.50.а).

Рис. 2.50.a. Преобразование синхронного RS-триггера в JK-триггер;

Если на входы J и К подать уровень логической единицы, то получим T-триггер, который переключается каждым входным импульсом (рис. 2.50, б).

Рис. 2.50.б. Преобразование JK-триггера в T-триггер;

На рис. 2.50.в приведено условное обозначение JK-триггера и таблица состояний. При входных сигналах J=К=0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет пpохождение сигналов от других его входов и удерживает выходной сигнал в текущем логическом состоянии.

Рис. 2.50.в. условное обозначение JK-триггера

| Установлено | Записано | ||

|---|---|---|---|

| J | K | Qn+1 | /Qn+1 |

| H | H | Без изменений Qn /Qn | |

| Н | В | Н=0 | В=1 |

| В | Н | В=1 | Н=0 |

| В | В | Переброс /Qn Qn | |

Если на входы J и К подать взаимно противоположные уровни, то при подаче перепада напряжения на вход С выходы JK-триггера устанавливаются в такие же состояния. При подаче на входы J и К одновременно напряжений высокого уровня триггер переключается в состояние, противоположное предыдущему, если на вход синхронизации С подать перепад напряжения.

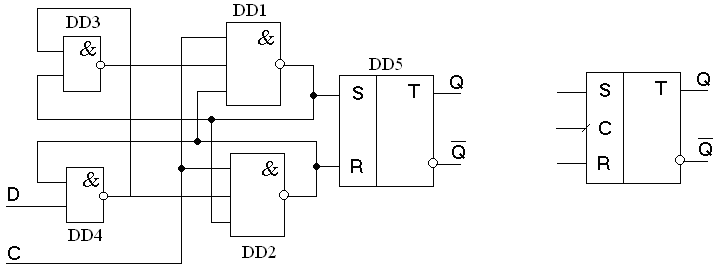

Управление полным тактовым импульсом, подаваемым на вход С, применяется для двухступенчатых триггеров (рис. 2.50.г).

Рис. 2.50.г. двухступенчатый JK-триггер;

Такой триггер тоже имеет обратные связи с выходов на входы, исключающие неопределенное состояние триггера.

Рис. 2.50.д. двухступенчатый JK-триггер на логических элементах И-НЕ

с симметричной схемой управления триггера второй ступени;

Из JK-триггера можно получить D-триггер, если вход К соединить со входом J через дополнительный инвертор (рис. 2.50,д).

Рис. 2.50.е. Схема преобразования JK-триггера в D-триггер

Микросхема TB1 (рис. 2.51) представляет собой универсальный двухступенчатый JK-триггер.

Рис. 2.51. Комбинированный JK-триггер — структура микросхемы, условное обозначение и цоколевка микросхемы ТВ1.

Триггер имеет инверсные асинхронные входы установки /S и сброса /R, т. е. с активным низким уровнем. Если на эти входы подать противоположные уровни (низкий — 0 и высокий — 1), то входы J, K и С не действуют и состояния выходов Q и /Q триггера определяются сигналами на входах /S и /R, таблица состояний (табл. 2.27).

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | Х | Х | Х | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | Х | 0 | 1 |

| Неопределенность | 0 | 0 | Х | Х | Х | X | X |

| Загрузка «1» (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка «0» (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 1 | _/\_ | /Qn | Qn |

| Хранение (нет изменений) | 1 | 1 | 0 | 0 | _/\_ | Qn | /Qn |

Когда на входы /S и /R поданы напряжения высокого уровня, в триггер можно загружать информацию от входов J и K или хранить ее (см. таблицу состояний). Каждый из входов J и K снабжен логическим элементом 3И, т.е. микросхема ТВ1 имеет три входа J и три входа K. Вход синхронизации C инверсный динамический. Состояния двухступенчатого триггера переключаются фронтом и спадом положительного импульса, подаваемого на вход синхронизации C. Информация со входов J и K загружается в триггер первой ступени (элементы DD1.3 и DD1.4), когда напряжение входа C изменяется от низкого уровня к высокому (по фронту) и переносится в триггер второй ступени по отрицательному перепаду импульса синхронизации (по спаду). Сигналы на входах J и K не должны изменяться, если на входе /C присутствует напряжение высокого уровня. Состояния выходов Q и /Q будут неопределенные, если на входы /S и /R одновременно подать напряжение низкого уровня, т. е. комбинация сигналов /S=/R=0 является запрещенной.

Микросхемы ТВ6 и ТВ9, ТВ10 и TB11 содержат по два JK-триггера с общим выводом питания (рис. 2.52).

Рис. 2.52. Структура, условное обозначение и цоколевка микросхем ТВ6, ТВ9;

Рис. 2.52a. Структура, условное обозначение и цоколевка микросхемы ТВ10;

Вход синхронизации С у всех триггеров инверсный динамический, поэтому данные от входов J и К переносятся на выходы Q и /Q по отрицательному перепаду импульса С. Когда импульс на входе С переходит от высокого уровня к низкому, сигналы на входах J и К не должны изменяться. Информацию от входов J и К следует загружать в триггер, когда на входе С присутствует напряжение высокого уровня.

У триггеров микросхемы ТВ6 нет входа предварительной установки /S, поэтому в таблице состояний (комбинированного JK-триггера) необходимо исключить первую строку (асинхронную установку 1). Если на вход /R будет подано напряжение низкого уровня, то входы J, К и С не действуют.

У триггеров микросхемы ТВ10 нет входа предварительного сброса /R, поэтому в таблице состояний комбинированного JK-триггера необходимо исключить вторую строку (асинхронный сброс 0).

Для микросхем ТВ6 и ТВ10 в таблице состояний не имеет смысла и третья строка, т. к, они имеют только по одному асинхронному входу (либо /S, либо /R). Триггеры микросхемы ТВ11 в отличие от триггеров микросхемы ТВ9 имеют две общие цепи управления: вход синхронизации /С и асинхронный вход сброса /R (рис. 2.53).

Рис. 2.53. Условное обозначение и цоколевка микросхемы ТВ11

Микросхемы ТВ14 и ТВ15 содержат по два комбинированных JK-триггера, которые запускаются положительным перепадом импульса синхронизации, т. е. вход С прямой динамический. Отличительной особенностью триггеров данных микросхем является то, что второй информационный вход /К — инверсный, поэтому очень легко такие JK-триггеры превращать в D-триггеры (рис. 2.54).

Рис. 2.54. Структура ТВ15, условные обозначения и цоколевки ТВ14 и ТВ15

Состояние таких триггеров приведено в табл. 2.28.

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | /K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | X | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | X | X | X | 0 | 1 |

| Неопределенность | 0 | 0 | X | X | X | 1 | 1 |

| Загрузка «1» (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка «0» (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 0 | _/\_ | /Qn=1 | Qn=0 |

| Хранение (нет изменений) | 1 | 1 | 0 | 1 | _/\_ | 1 | 0 |

Основные параметры триггеров ТТЛ приведены в табл.2.20.

29.8 Универсальный jk-триггер

Среди триггеров особое место занимают JK-триггеры, имеющие более широкие функциональные возможности.

Универсальный JK-триггер, схема которого представлена на рисунке 29.13, представляет собой двухступенчатый синхронный триггер.

Триггер типа JK имеет выходы установки (J) и сброса (K), подобные входам триггера RS. JK-триггер отличается от синхронного RS-триггера тем, что не имеет запрещенных комбинаций сигналов на входах J и K. Триггер собран по схеме Master–Slave и состоит из двух асинхронных RS-триггеров с инверсными входами и двух комбинационных устройств, каждое из которых содержит две схемы И-НЕ с тремя входами каждая.

Триггер

работает в два такта: на первом информация

записывается в первый триггер, а по

окончанию первого такта информация

переписывается во второй триггер. Один

из входов JK-триггера

всегда заблокирован нулевым сигналом

с выхода Q

или  .

В результате этого триггер не имеет

запрещенных состояний и позволяет

одновременную подачу двух единиц на

входыJ

и K.

.

В результате этого триггер не имеет

запрещенных состояний и позволяет

одновременную подачу двух единиц на

входыJ

и K.

Рисунок 29.13 – Внутренняя структурная схема JK-триггера

В таблице 29.5 приведено описание работы JK-триггера.

Таблица 29.6 – Таблица истинности JK-триггера

J | K | Q0 | Q |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 0 | 1 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 1 |

1 | 1 | 1 | 0 |

Рассмотрим принцип работы JK-триггера. При С = 0 входы J и K заблокированы и, следовательно, оказываются заблокированными входы S и R триггера Т1. При С = 1 в соответствии с информационными сигналами на входах J и K устанавливается состояние ведущего триггера Т1. При этом на входы S и R ведомого триггера Т2 поступают сигналы, при которых его предыдущее состояние сохраняется. При С = 0, когда входы триггера Т1 закрыты для входной информации, входы триггера Т2 открываются и состояние ведущего триггера воспринимается ведомым триггером.

Микросхемы, содержащие JK-триггер, кодируются буквами ТВ.

29.9 Т-триггер

Т-триггер – это счетный триггер. Т-триггер имеет один вход (который является и тактирующим и информационным), куда подают тактирующие (счетные) импульсы. После подачи каждого тактирующего импульса состояние Т-триггера меняется на противоположное (инверсное) предыдущему состоянию (аналогично состоянию JK-триггера при комбинации входных переменных J = 1 и K = 1). Т-триггеры строятся только на базе двухступенчатых (RS, D, JK) триггеров.

На рисунке 29.14 приведено УГО Т-триггера с прямым синхронным входом Т, а на рисунке 29.15 – временные диаграммы, поясняющие его работу.

Рисунок 29.14 – УГО Т-триггера с прямым синхронным входом

Рисунок 29.15 – Временные диаграммы работы Т-триггера

29.10 Синхронные триггеры с динамическим управлением

Синхронный триггер с динамическим управлением по входу С воспринимает информацию для изменения состояния лишь тогда, когда на С-входе совершается переход с уровня 0 на уровень 1, либо наоборот. Динамические триггеры могут изменять свое состояние как передним, так и задним фронтом тактирующих импульсов. Фрагменты схемного обозначения приведены на рисунке 29.16:

Рисунок 29.16 – Фрагменты схемного обозначения линии

синхронизации

Для получения RS-триггера с динамическим входом достаточно построить схему, показанную на рисунке 29.17.

Рисунок 29.17 – Схема RS-триггера с динамическим входом

на элементах И-НЕ

Если при С = 0 на информационные входы поступили какие-либо уровни S и R, то при смене уровня на входе С с лог. 0 на лог. 1 на выходе элемента DD1 образуется лог. 0, который поступает на вход элемента DD3 и обеспечивает на его выходе уровень лог. 1 независимо от последующих значений уровня на входе S. Вход S логически отключается, и никакие изменения уровней на входах S и R триггер не воспринимает, пока не произойдет на входе С переход с уровня лог. 0 на уровень лог. 1.

Аналогично можно построить схему Rs-триггера с динамическим входом на элементах ИЛИ-НЕ (рисунок 29.18).

Рисунок 29.18 – Схема RS-триггера с динамическим входом

на элементах ИЛИ-НЕ

Здесь информация воспринимается триггером со входом S и R при смене уровней С = 1 на С = 0. Условное изображение такого триггера показано на рисунке 29.19.

Рисунок 29.19 – УГО RS-триггера с динамическим входом

синхронизации

Схема D-триггера с динамическим входом и его условное графическое обозначение приведены на рисунке 29.20:

а) б)

а – внутренняя структурная схема D-триггера с динамическим входом;

б – УГО D-триггера с динамическим входом

Рисунок 29.20 – D-триггер с динамическим входом

синхронизации на элементах И-НЕ

Прием в триггер информации со входа D происходит в момент смены на входе С уровня лог. 0 на уровень лог. 1.

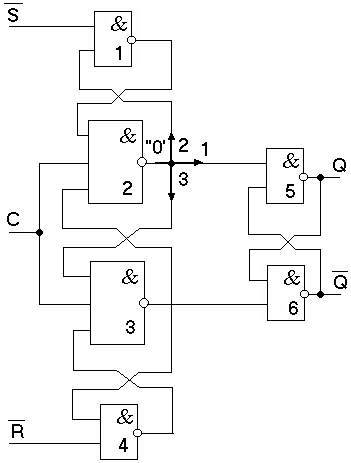

Построение триггеров с динамическим управлением также можно показать на примере так называемого шестиэлементного триггера (другое название – схема «трех триггеров»), внутренняя структурная схема показана на рисунке 29.21.

Рисунок 29.21 – Внутренняя структурная схема синхронного

RS-триггера на основе шестиэлементной схемы

Часть схемы, включающая в себя элементы 2, 3, 5, 6 без цепей перекрестных связей между элементами 2 и 3, образует синхронный RS-триггер с управлением уровнем, чувствительный к изменению информационных сигналов при С = 1. Чтобы получить такую чувствительность только во время фронта сигнала С, нужно блокировать цепи подачи входных сигналов сразу же после изменения синхросигнала с нулевого значения на единичное. Для достижения этого в представленной выше схеме входные сигналы подаются через элементы 1 и 4, которые и будут блокироваться в указанные моменты времени и сохранять блокировку до возвращения С к нулевому уровню. Нулевое значение С устанавливает единицы на выходах элементов 2 и 3 и приводит фиксатор в режим хранения до нового изменения синхросигнала от нуля к единице. В этом состоянии (при С = 0) выходы элементов 1 и 4 дают инверсии входных сигналов, передавая на элементы 2 и 3 значения S и R соответственно.

Что произойдет при поступлении С = 1? Если при этом S =R = 0, то сохранится режим хранения. Если же имеется единичный входной сигнал, то на входе одного из элементов (2 или 3) все входы окажутся единичными, а его выход – нулевым, что даст сигнал установки выходного триггера (элементы 5 и 6) в нужное состояние и, кроме того, отключит входной сигнал, вызвавший воздействие на схему, и также предотвратит возможное воздействие на выходной триггер по его второму входу (на элемент 6).

Три

указанных действия вызываются сигналами

логического нуля, подаваемыми по стрелкам

1, 2 и 3. Предполагается, что единичное

значение имел вход S

( ).

).

На основе рассмотренного шестиэлементного триггера строятся триггеры типов D, T и JK с динамическим управлением.

Счетные Т и JK-триггеры — Help for engineer

Счетные Т и JK-триггеры

Т-триггеры можно построить с помощью любого двухступенчатого триггера. Наличие двух ступеней позволяет избавиться от запрещенных состояний. Ранее мы рассматривали принцип работы D-триггера, именно поэтому построение счетного триггера будем осуществлять на его базе. Он состоит из входа C (синхронизирующий) и выхода Q. Чтобы произвести синтез необходимого нам устройства, нужно инверсный выход соединить со входом:

Счетным Т-триггер называют потому, что он считает количество импульсов, которое поступает к нему на вход. Правда, подсчет ведется лишь до одного. При повторной подаче сигнала на вход – значение выхода сбрасывается. Это свойство дало возможность использовать устройство, как делитель частоты.

С выхода будем снимать импульсы вдвое меньшей частоты, чем было на входе

Для построения счетного устройства мы использовали д-триггер с работой по заднему фронту. Соответственно и полученное будет работать по тому же принципу, временная диаграмма имеет следующий вид:

Собранный T-trigger на логических элементах представлен ниже. Синий провод означает нулевой уровень напряжения, красный – единица. Работает устройство при подаче импульсов с определенной частотой на вход C. Начинает происходить подсчет входящего сигнала, и по заднему фронту, выход меняет значение:

Обозначение ничем не отличается от ранее рассмотренных:

Все это мы говорили об асинхронном т-триггере (работа не контролируется никаким дополнительным сигналом). В синхронном операции начинают выполняться после подачи единицы на вход С. Небольшая модификация позволяет получить синхронный t-триггер, теперь он включится в работу только при подаче синхросигнала:

Временная диаграмма асинхронного устройства приобретает чуть иной характер, появляется прямая зависимость выхода от синхронизирующего входа:

Обозначение на схемах:

JK-trigger не совсем счетный, он считает только при определенной комбинации на входе. Работает он практически так же, как и RS. Его преимущество — не имеет запрещенной комбинации. То есть, по сути, это усовершенствованный rs-триггер. Запрещенная комбинация 1,1 убирается с помощью обратных связей. Для него таблица истинности:

Собираем на ТТЛ (логических) элементах. С помощью анимации намного проще понять, как все работает. Единица в верхнем правом углу рисунка означает первый кадр – начало отсчета. Если на входах появятся две единицы, то при отключении синхросигнала, значение на выходе Q будет меняться на противоположное (счет).

Схематическое обозначение не имеет ярко выраженных особенностей:

Недостаточно прав для комментирования

Динамические параметры микросхем ТТЛ серии

Динамические параметры микросхем ТТЛ серии