| Главная Автомагнитолы DVD Материнские платы Мобильные телефоны Мониторы Ноутбуки Принтеры Планшеты Телевизоры Даташиты Маркировка SMD Форум |

|

Качество y1 smd транзистор для электронных проектов Free Sample Now

Alibaba.com предлагает большой выбор. y1 smd транзистор на выбор в соответствии с вашими потребностями. y1 smd транзистор являются жизненно важными частями практически любого электронного компонента. Их можно использовать для создания материнских плат, калькуляторов, радиоприемников, телевизоров и многого другого. Выбирая правильно. y1 smd транзистор, вы можете быть уверены, что создаваемый вами продукт будет высокого качества и очень хорошо работает. Ключевые факторы выбора продуктов включают предполагаемое применение, материал и тип, среди прочего.

y1 smd транзистор состоят из полупроводниковых материалов и обычно имеют не менее трех клеммы, которые можно использовать для подключения к внешней цепи. Эти устройства работают как усилители или переключатели в большинстве электрических цепей. y1 smd транзистор охватывают два типа областей, которые возникают из-за включения примесей в процессе легирования. В качестве усилителей.

y1 smd транзистор скрывают низкий входной ток в большую выходную энергию, и они направляют небольшой ток для управления огромными приложениями, работающими как переключатели.

Изучите прилагаемые таблицы данных вашего. y1 smd транзистор для определения опорных ног, эмиттера и коллектора для безопасного и надежного соединения. Файл. y1 smd транзистор на сайте Alibaba.com используют кремний в качестве первичной полупроводниковой подложки благодаря их превосходным свойствам и желаемому напряжению перехода 0,6 В. Основные параметры для. y1 smd транзистор для любого проекта включает в себя рабочие токи, рассеиваемую мощность и напряжение источника.

Откройте для себя удивительно доступный. y1 smd транзистор на Alibaba.com для всех ваших потребностей и предпочтений. Доступны различные материалы и стили для безопасной и удобной установки и эксплуатации. Некоторые аккредитованные продавцы также предлагают послепродажное обслуживание и техническую поддержку.

| Тип прибора |

маркировка | структ. код п/п | аналог (прибл.) | Краткие параметры | |

|---|---|---|---|---|---|

|

Типов. |

Рев. | ||||

| ВА316 | А6 | Si-Di | BAW62, 1N4148 | Min, S, 85V, 0.1A, <6ns | |

| BAS17 | А91 | Si-St | ВА314 | Min, Stabi, 0.75…0.83V/10mA | |

| ВА319 | А8 | Si-Di | BAV19 | Min, S, Uni, 120V, 0.2A, <5ms | |

| BAS20 | А81 | Si-Di | BAV20 | Min, S, Uni, 200V, 0. 2A, <5ms 2A, <5ms |

|

| BAS21 | А82 | Si-Di | BAV21 | Min, S, Uni, 250V, 0.2A, <5ms | |

| BAS29 | Si-Di | BAX12 | Min, S, Uni, 300V, 0.25A, <4ms | ||

| BAS31 | L21 | Si-Di | 2XBAX12 | Min, S, Uni, 300V, 0.25A, <4ms | |

| BAS35 | L22 | Si-Di | 2xBAX12 | Min, S, Uni, 300V, 0.25A, <4ms | |

| ВАТ17 | A3 | Pin-Di | BA480 | VHF/UHF-Band-S, 4V, 30mA, 200MHz | |

| ВАТ18 | А2 | Pin-Di | BA482 | VHF/UHF-Band-S, 35V, 0. 1A, 200MHz 1A, 200MHz |

|

| BAV70 | А4 | Si-Di | 2xBAW62 1N4148 | Min, Dual, 70V, 0.1A, <6ns | |

| BAV99 | А7 | Si-Di | 2xBAW62 1N4148 | Min, Dual, 70V, 0.1A, <6ns | |

| BAW56 | А1 | Si-Di | 2xBAW62 1N4148 | Min, Dual, S, 70V, 0.1A, <6ns | |

| BBY31 | 81 | C-Di | BB405, BB609 | UHF-Tuning, 28V, 20mA, Cd=1.8 — 2.8pF | |

| BBY40 | S2 | C-Di | BB809 | UHF-Tuning, 28V, 20mA, Cd=4.3-6pF | |

| ВС807-16 | 5A | 5AR | Si-P | BC327-16 | Min, NF-Tr, 45V, 0. 5A, 100MHz, B= 100-250 5A, 100MHz, B= 100-250 |

| ВС807-25 | 5В | 5BR | Si-P | BC327-25 | Min, NF-Tr, 45V, 0.5A, 100MHz, B= 160-400 |

| ВС807-40 | 5С | 5CR | Si-P | BC327-40 | Min, NF-Tr, 45V, 0.5A, 100MHz, B= 250-600 |

| ВС808-16 | 5Е | 5ER | Si-P | BC328-16 | Min, NF-Tr, 25V, 0.5A, 100MHz, B= 100-250 |

| ВС808-25 | 5F | 5FR | Si-P | BC328-25 | Min, NF-Tr, 25V, 0.5A, 100MHz, B= 160-400 |

| BC808-40 | 5G | 5GR | Si-P | BC328-40 | Min, NF-Tr, 25V, 0. 5A, 100MHz, B= 250-600 5A, 100MHz, B= 250-600 |

| BC817-16 | 6A | 6AR | Si-N | BC337-16 | Min, NF-Tr, 5V, 0.5A, 200MHz, B= 100-250 |

| BC846B | 1В | 1BR | Si-N | BC546B | Min, Uni, 80V, 0.1A, 300MHz |

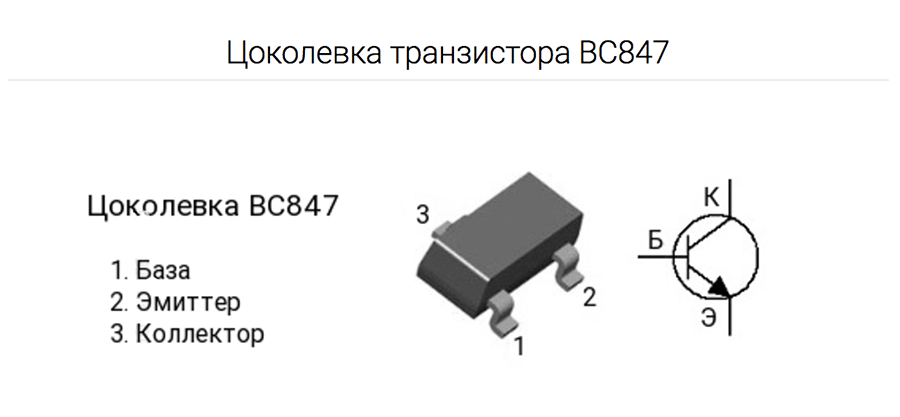

| BC847A | 1E | 1ER | Si-N | BC547A, BC107A | Min, Uni, 45V, 0.1A, 300MHz, B= 110-220 |

| BC847B | 1F | 1FR | Si-N | BC547B, BC107B | Min, Uni, 45V, 0.1A, 300MHz, B= 200-450 |

| BC847C | 1G | 1GR | Si-N | BC547C, BC107C | Min, Uni, 45V, 0. 1A, 300MHz, B= 420-800 1A, 300MHz, B= 420-800 |

| BC848A | U | 1JR | Si-N | BC548A, BC108A | Min, Uni, 30V, 0.1A, 300MHz, B= 110-220 |

| BC848B | 1K | 1KR | Si-N | BC548B, BC108B | Min, Uni, 30V, 0.1A, 300MHz, B= 200-450 |

| BC848C | 1L | 1LR | Si-N | BC548C, BC108C | Min, Uni, 30V, 0.1A, 300MHz, B= 420-800 |

| BC849B | 2В | 2BR | Si-N | BC549B, ВС108В | Min, Uni, ra 30V, 0.1A, 300MHz, B= 200-450 |

| BC849C | 2С | 2CR | Si-N | BC549C, BC109C | Min, Uni, ra, 30V, 0. 1A, 300MHz, B= 420-800 1A, 300MHz, B= 420-800 |

| BC850B | 2F | 2PR | Si-N | BC550B, BCY59 | Min, Uni, ra, 45V, 0.1A, 300MHz, B= 200-450 |

| BC850C | 2G | 2GR | Si-N | BC550C, BCY59 | Min, Uni, ra, 45V, 0.1A, 300MHz, B= 420-800 |

| BC856A | ЗА | 3AR | Si-P | BC556A | Min, Uni, 65V, 0.1A, 150MHz, B= 125-250 |

| BC856B | 3В | 3BR | Si-P | BC556B | Min, Uni, 65V, 0.1A, 150MHz, B= 220-475 |

| BC857A | ЗЕ | 3ER | Si-P | BC557A, BC177A | Min, Uni, 45V, 0. 1A, 150MHz, B= 125-250 1A, 150MHz, B= 125-250 |

| BC857B | 3F | 3FR | Si-P | BC557B, BC177B | Min, Uni, 45V, 0.1A, 150MHz, B= 220-475 |

| ВС857С | 3G | 3GR | Si-P | BC557C | Min, Uni, 45V, 0.1A, 150MHz, B= 420-800 |

| ВС858А | 3J | 3JR | Si-P | BC558A, BC178A | Min, Uni, 30V, 0.1A, 150MHz B= 125-250 |

| ВС858В | ЗК | 3KR | Si-P | BC558B, BC178B | Min, Uni, 30V, 0.1A, 150MHz B= 220-475 |

| ВС858С | 3L | 3LR | Si-P | BC558C | Min, Uni, 30V, 0. 1A, 150MHz B= 420-800 1A, 150MHz B= 420-800 |

| ВС859А | 4А | 4AR | Si-P | BC559A, BC179A, BCY78 | Min, Uni, га, 30V, 0.1A, 150MHz, B= 150 |

| ВС859В | 4В | 4BR | Si-P | BC559B, BCY79 | Min, Uni, rа,30V, 0.1A, 150MHz, B= 220-475 |

| ВС859С | 4С | 4CR | Si-P | BC559C, BCY79 | Min, Uni, га, 30V, 0.1A, 150MHz, B= 420-800 |

| ВС860А | 4Е | 4ER | Si-P | BC560A, BCY79 | 45V, 0.1A, 150MHz, B= 150 |

| ВС860В | 4F | 4FR | Si-P | BC560B, BCY79 | Min, Uni, га, 45V, 0. 1A, 150MHz, B= 220-475 1A, 150MHz, B= 220-475 |

| ВС860С | 4G | 4GR | Si-P | BC560C, BCY79 | Min, Uni, га, 45V, 0.1A, 150MHz, B= 420-800 |

| BCF29 | С7 | С77 | Si-P | BC559A, BCY78, BC179 | Min, NF-V, га, 32V, 0.1A, 150MHz, |

| BCF30 | С8 | С9 | Si-P | BC559B, BCY78 | Min, NF-V, га, 32V, 0.1A, 150MHz, |

| BCF32 | 07 | 077 | Si-N | BC549B, BCY58, BC109 | Min, NF-V, га, 32V, 0.1A, 300MHz, |

| BCF33 | D8 | D81 | Si-N | BC549C, BCY58 | Min, NF-V, га, 32V, 0. 1A, 300MHz, 1A, 300MHz, |

| BCF70 | Н7 | Н71 | Si-P | BC560B, BCY79 | Min, NF-V, га, 50V, 0.1A, 1500MHz, |

| BCF81 | К9 | К91 | Si-N | BC550C | Min, NF-V, 50V, 0.1A, 300MHz, га |

| BCV71 | К7 | К71 | Si-N | BC546A | NF/S, 80V,0.1A, 300MHz, B=110-220 |

| BCV72 | К8 | К81 | Si-N | BC546B | NF/S, 80V,0.1A, 300MHz, B=200-450 |

| BCW29 | С1 | С4 | Si-P | BC178A, BC558A | Min, Uni, 30V, 0.1A, 150MHz, B= >120 |

| BCW30 | С2 | С5 | Si-P | BC178B, BC558B | Min, Uni, 30V, 0. 1A, 150MHz, В= >215 1A, 150MHz, В= >215 |

| BCW31 | D1 | D4 | Si-N | ВС108А,ВС548А | Min, Uni, 30V, 0.1A, 300MHz, В= >110 |

| BCW32 | 02 | D5 | Si-N | ВС108В, ВС548 | Min, Uni, 30V, 0.1A, 300MHz, B= >200 |

| BCW33 | D3 | 06 | Si-N | ВС108С, ВС548С | Min, Uni, 30V, 0.1A, 300MHz, B= >420 |

| BCW60A | АА | Si-N | ВС548А | Min, Uni, 32V, 0.1A, 250MHz, B= 110-220 | |

| BCW60B | АВ | Si-N | ВС548В | Min, Uni, 32V, 0.1A, 250MHz, S= 200-450 | |

| BCW60C | АС | Si-N | ВС548В | Min, Uni, 32V, 0. 1A, 250MHz, B= 420-600 1A, 250MHz, B= 420-600 |

|

| BCW60D | AD | Si-N | ВС548С | Min, Uni, 32V, 0.1A, 250MHz, B= 620-800 | |

| BCW61A | ВА | Si-P | BC558A | Min, Uni, 32V, 0.2A, 180MHz, B= 110-220 | |

| BCW61B | ВВ | Si-P | BC558B | Min, Uni, 32V, 0.2A, 250MHz, B= 200-450 | |

| BCW61C | ВС | Si-P | BC558B | Min, Uni, 32V, 0.2A, 250MHz, B= 420-620 | |

| BCW61D | BD | Si-P | BC558C | Min, Uni, 32V, 0.2A, 250MHz, B= 600-800 | |

| BCW69 | Н1 | Н4 | Si-P | ВС557А | Min, Uni, 50V, 0. 1A, 150MHz, B>120 1A, 150MHz, B>120 |

| BCW70 | Н2 | Н5 | Si-P | ВС557В | Min, Uni, 50V, 0.1A, 150MHz, B>215 |

| BCW71 | К1 | К4 | Si-N | ВС547А | Min, NF, 50V, 0.1A, 300MHz, B>110 |

| BCW72 | К2 | К5 | Si-N | ВС 547В | Min, NF, 50V, 0.1A, 300MHz, B>200 |

| BCW81 | КЗ | К31 | Si-N | ВС547С | Min, NF, 50V, 0.1A, 300MHz, B>420 |

| BCW89 | НЗ | Н31 | Si-P | ВС556А | Min, Uni, 80V, 0. 1A, 150MHz, B>120 1A, 150MHz, B>120 |

| BCX17 | Т1 | Т4 | Si-P | ВС327 | Min, NF-Tr, 50V,0.5A, 100MHz |

| BCX18 | Т2 | Т5 | Si-P | ВС328 | Min, NF-Tr, 30V.0.5A, 100MHz |

| BCX19 | U1 | U4 | Si-N | BC337 | Min, NF-Tr, 50V.0.5A, 200MHz |

| BCX20 | U2 | U5 | Si-N | ВС 33 8 | Min, NF-Tr, 30V,0.5A, 200MHz |

| BCX70G | AG | Si-N | BC107A, BC547A | Min, Uni, 45V, 0.2A, 250MHz, B= 110-220 | |

| BCX70H | AH | Si-N | ВС 107В, BC547B | Min, Uni, 45V, 0. 2A, 250MHz, B= 200-450 2A, 250MHz, B= 200-450 |

|

| BCX70J | AJ | Si-N | ВС107В, BC547B | Min, Uni, 45V, 0.2A, 250MHz, B= 420-620 | |

| BCX70K | AK | Si-N | ВС107С, BC547C | Min, Uni, 45V, 0.2A, 250MHz, B= 600-800 | |

| BCX71G | BG | Si-P | ВС177А, BC557A | Min, Uni, 45V, 0.2A,180MHz, B= 125-250 | |

| BCX71H | BH | Si-P | ВС 177В, BC557B | Min, Uni, 45V, 0.2A.180MHz, B= 220-475 | |

| BCX71J | BJ | Si-P | ВС 177В, BC557B | Min, Uni, 45V, 0.2A,180MHz, B= 420-650 | |

| BCX71K | BK | Si-P | ВС557С | Min, Uni, 45V, 0. 2A.180MHz, B= 620-800 2A.180MHz, B= 620-800 |

|

| BF510 | S6 | N-FET | BF410A | Min, VHF-ra, 20V, ldss= 0.7-3mA, Vp= 0.8V | |

| BF511 | S7 | N-FET | BF410B | Min, VHF-ra, 20V, !dss= 2.5-7mA, Vp= 1.5V | |

| BF512 | S8 | N-FET | BF410C | Min, VHF-ra, 20V, ldss= 6-12mA, Vp= 2.2V | |

| BF513 | S9 | N-FET | BF410D | Min, VHF-ra, 20V, ldss= 10-18mA, Vp= 3V | |

| BF536 | G3 | SI-P | BF936 | Min, VHF-M/0, 30V, 25mA, 350MHz | |

| BF550 | G2 | G5 | Si-P | BF450 | Min, HF/ZF, 40V, 25mA, 325MHz |

| BF569 | G6 | Si-P | BF970 | Min, UHF-M/0, 40V, 30mA, 900MHz | |

| BF579 | G7 | Si-P | BF979 | Min, VHF/UHF, 20V, 25mA, 1. 35GHZ 35GHZ |

|

| BF660 | G8 | G81 | Si-P | BF606A | Min, VHF-0, 40V, 25mA, 650MHz |

| BF767 | G9 | Si-P | BF967 | Min, VHF/YHF-ra, 30V,20mA,900MHz | |

| BF820 | S-N | BF420 | Min, Vid, 300V, 25-50mA, >60MHz | ||

| BF821 | 1W | Si-P | BF421 | Min, Vid, 300V, 25-50mA, >60MHz | |

| BF822 | 1Х | Si-N | BF422 | Min, Vid, 250V, 25-50mA, >60MHz | |

| BF823 | 1Y | Si-P | BF423 | Min, Vid, 250V, 25-50mA, >60MHz | |

| BF824 | F8 | Si-P | BF324 | Min, FM-V, 30V, 25mA, 450MHz | |

| BF840 | F3 | Si-N | BF240 | Min, Uni, 15V, 0 1A, 0. 3W,>90MHz 3W,>90MHz |

|

| BF841 | F31 | SI-N | BF241 | Min, AM/FM-ZF, 40V,25mA, 400MHz | |

| BFR30 | М1 | N-FET | BFW-11, BF245 | Min, Uni, 25V, ldss>4mA, YP<5V | |

| BFR31 | М2 | N-FET | BFW12, BF245 | Min, Uni, 25V, ldss>1mA, YP<2 5V | |

| BFR53 | N1 | N4 | Si-N | BFW30, BFW93 | Min, YNF-A, 18V, 50mA, 2GHz |

| BFR92 | Р1 | Р4 | Si-N | BFR90 | Min, YHF-A, 20V, 25mA, 5GHz |

| BFR92A | Р2 | РЬ | Si-N | BFR90 | Min, YHF-A, 20V, 25mA, 5GHz |

| BFR93 | R1 | R4 | Si-N | BFR91 | Min, YHF-A, 15V, 35mA, 5-6GHz |

| BFR93A | R2 | R5 | Si-N | BFR91 | Min, YHF-A, 15V, 35mA, 5-6GHz |

| BFS17, (BFS17A) | Е1 (Е2) | Е4 (F5) | Si-N | BFY90, BFW92(A) | Min, VHP/YHF, 25V, 25mA, 1-2GHz |

| BFS18 | F1 | F4 | Si-N | BF185, BF495 | Min, HF, 30V, 30mA, 200MHz |

| BFS19 | F2 | F5 | Si-N | BF184, BF494 | Min, HF, 30V, 30mA, 260MHz |

| BFS20 | G1 | G4 | Si-N | BF199 | Min, HF, 30V, 30mA,450MHz |

| BFT25 | V1 | V4 | Si-N | BFT24 | Min, UHF-A, 8v, 2. 5mA, 2.3GHZ 5mA, 2.3GHZ |

| BFT46 | МЗ | NFT | BFW13, BF245 | Min, NF/HF, 25V, ldss>0.2mA, Up<1.2V | |

| BFT92 | W1 | W4 | Si-P « | BFQ51, BFQ52 | Min, UHF-A, 20V, 25mA, 5GHz |

| BFT93 | Х1 | Х4 | Si-P | BFQ23, BFQ24 | Min, UHF-A, 15V,35mA, 5GHz |

| BRY61 | А5 | BYT | BRY56 | 70V | |

| BRY62 | А51 | Tetrode | BRY56, BRY39 | Tetrode, Min, 70V, 0.175A | |

| BSR12 | B5 | В8 | Si-P | 2N2894A | Min, S, 15V,0. 1A,>1.5GHz <20/30ns 1A,>1.5GHz <20/30ns |

| BSR13 | U7 | U71 | Si-N | 2N2222, Ph3222 | Min, HF/S, 60V, 0.8A, <35/285ns |

| BSR14 | U8 | U81 | Si-N | 2N2222A, Ph3222A | Min, HF/S, 75V, 0.8A, <35/285ns |

| BSR15 | T7 | T71 | Si-P | 2N2907, Ph3907 | Min, HF/S, 60/40V, 0.6A, <35/110ns |

| BSR16 | T8 | T81 | Si-P | 2N2907A, Ph3907A | Min, HF/S, 60/60V, 0.6A, <35/110ns |

| BSR17 | U9 | U91 | Si-N | 2N3903 | Min, HF/S, 60V, 0. 2A, <70/250ns, B-50-150 2A, <70/250ns, B-50-150 |

| BSR17A | U92 | U93 | Si-N | 2N3904 | Min, HF/S, 60V, 0.2A, <70/225ns, B= 100-300 |

| BSR18 | T9 | T91 | Si-P | 2N3905 | Min, HF/S, 40V, 0.2A, 200MHz |

| BSR18A | T92 | T93 | Si-P | 2N3906 | Min, HF/S, 40V, 0.2A, 250MHz |

| BSR19 | U35 | Si-N | 2N5550 | Min, HF/S, 160V, 0.6A, >100MHz | |

| BSR19A | U36 | Si-N | 2N5551 | Min, HF/S, 180V, 0.6A, >100MHz | |

| BSR20 | T35 | Si-P | 2N5400 | Min, HF/S, 130V, 0. 6A, >100MHz 6A, >100MHz |

|

| BSR20A | T36 | Si-P | 2N5401 | Min, HF/S, 160V, 0.6A, >100MHz | |

| BSR56 | M4 | N-FET | 2N4856 | Min, S, Chopper, 40V, Idss >40mA, Up <10V | |

| BSR57 | M5 | N-FET | 2N4857 | Min, S, Chopper, 40V, Idss >20mA, Up <6V | |

| BSR58 | M6 | N-FET | 2N4858 | Min, S, Chopper, 40V, Idss >8mA, Up <4V | |

| BSS63 | T3 | T6 | Si-P | BSS68 | Min, Uni, 110V, 0.1A, 85MHz |

| BSS64 | U3 | U6 | Si-N | BSS38 | Min, Uni, 120V, 0. 1A, 100MHz 1A, 100MHz |

| BSV52 | B2 | B3 | Si-N | Ph3369, BSX20 | Min, S, 20V, 0.1A, <12/18ns |

| BZX84-… | см.пр им. | Si-St | BZX79 | Min, Min/Vrg Uz= 2.4-75V, P=0.3W | |

| PBMF4391 | M62 | N-FET | — | Min, 40V, ldss= 50mA, Up= 10V | |

| PBMF4392 | M63 | N-FET | — | Min, 40V, ldss= 25mA, Up= 5V | |

| PBMF4393 | M64 | N-FET | — | Min, 40V, ldss= 5mA, Up= 3V | |

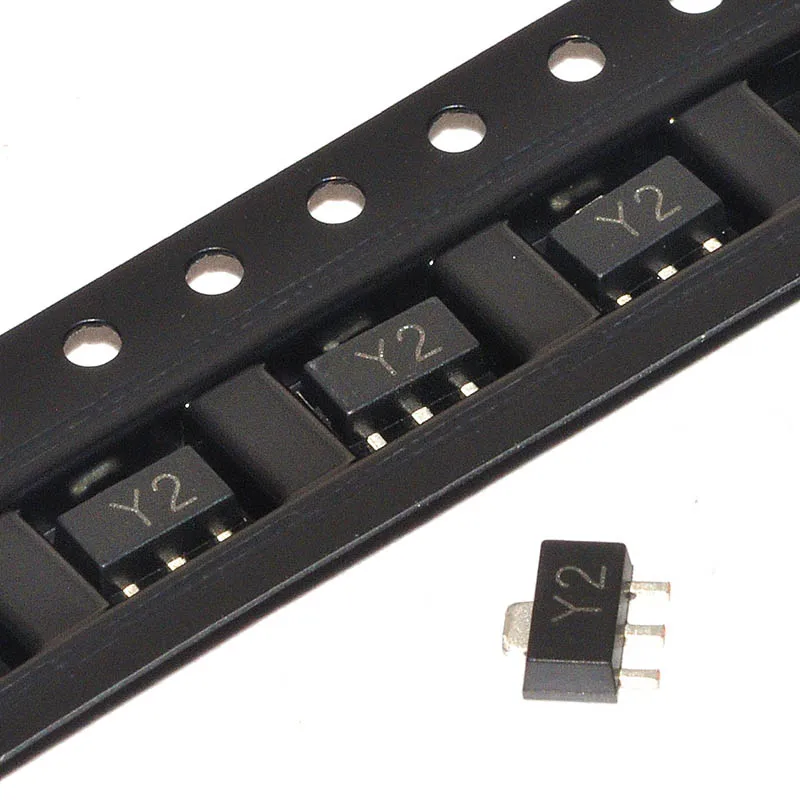

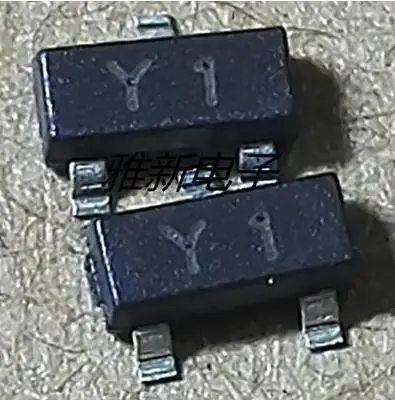

Оригинальные электронные компоненты QZ SS8050 Y1, транзисторы с пластиковой оболочкой SOT-23 SS8050

Описание и отзывы

Характеристики

|

Продукт основные параметры |

|

|

Номер изделия: |

SS8050 |

|

Категория продукта |

Транзистор |

|

Время выполнения заказа |

В наличии на складе |

|

Состояние |

Новый и оригинальный |

|

D/C (код даты) |

Новейший (случайный при доставке) |

|

Диапазон рабочих температур |

-55 ℃-+ 150 ℃ |

|

Пакет |

СОТ-23 |

|

Вес единицы |

1 г/шт. |

|

Без свинца статус |

Без свинца |

|

По ограничению на использование опасных материалов в производстве статус |

По ограничению на использование опасных материалов в производстве, отвечающих требованиям |

|

MPQ упаковка |

3000 шт./катушка |

|

Техническое описание |

Если вам это нужно, пожалуйста, свяжитесь с нами. |

|

Упаковка, оплата, время выполнения заказа, доставка и гарантия |

|||

|

Упаковка |

1. 2. Нейтральная белая упаковка коробки 3. По вашему требованию. |

||

|

Оплата |

1. Элементы оплаты: T/T, L/C, PayPal, Western union и т. Д. 2. Политика оплаты: 30% депозита и 70% баланса перед отправкой. |

||

|

Время выполнения заказа |

15-30 дней для новых деталей заказа и 3-5 дя на складеДетали. |

||

|

Доставка |

1. По морю (пожалуйста, сообщите нам ваш порт назначения) 2. По воздуху (пожалуйста, сообщите нам ваш воздушный порт) 3. 4. Вашим агентом (Если ваш агент в Гуанчжоу, мы можем отправить им С помощью бесплатного соответственно) |

||

Почему стоит выбрать «QZ»?

1. По цене-прямые поставки с фабрики, наиболее приемлемые цены

2. Для вас-лучший и быстрый сервис, и лучшее послепродажное обслуживание.

3. Для качества-гарантируем отличное качество продукции, долгий срок службы

4. Для своевременной доставки, быстрая и точная доставка.

5. Для поставок-сильная способность производства, большой собственный запас.

6. Для точности-профессиональная Минимальная точность, бесшумная работа,

С низким уровнем потерьИ хорошая стабильность размеров!

7. Для сотрудничества-Оптимизация процессов покупки и оплаты.

Для сотрудничества-Оптимизация процессов покупки и оплаты.

Очень удобно для вас!

8. Для дизайна-профессиональная команда OEM, может проектировать и производить любые

В соответствии с вашими требованиями!

Лабораторная работа № 7. Исследование базовых логических элементов

Методические указания

Лабораторный макет позволяет исследовать статические характеристики и параметры, а также параметры быстродействия логических элементов ТТЛ (транзисторно-транзисторная логика) и ЭСЛ (эмиттерно-связанная логика) цифровых микросхем. Он включает в себя источник входного напряжения, формирователь импульсов и исследуемые микросхемы. Напряжение источника входного напряжения определяется положением переключателей (как сумма их показаний) с учетом множителя. Полярность выходного напряжения устанавливается тумблером. Уровни логического «0» и «1» для каждого типа исследуемых микросхем выведены на соответствующие гнезда. Формирователь импульсов «ФИ» формирует короткие импульсы положительной полярности, подаваемые на вход исследуемой микросхемы для определения параметров быстродействия.

Полярность выходного напряжения устанавливается тумблером. Уровни логического «0» и «1» для каждого типа исследуемых микросхем выведены на соответствующие гнезда. Формирователь импульсов «ФИ» формирует короткие импульсы положительной полярности, подаваемые на вход исследуемой микросхемы для определения параметров быстродействия.

Характеристики и параметры базовых логических (БЛЭ) элементов делятся на статические и динамические. Статические характеристики определяют связь постоянных токов и напряжений, действующих на выводах ЛЭ. Основными статическими характеристиками ЛЭ являются: входная, выходная и передаточная характеристики.

Входная характеристика — зависимость входного тока от входного напряжения Iвх=f(Uвх) для одного из входов при заданном количестве нагрузок на выходе. На другие входы подаются уровни логического нуля «О» либо логической единицы «1» в зависимости от логической функции выполняемой ЛЭ.

Выходная характеристика — зависимость выходного тока от выходного напряжения Iвых=f(Uвых). Характеристика снимается для двух состояний элемента: на выходе элемента низкий уровень напряжения U0вых и на выходе высокий уровень U1вых.

Характеристика снимается для двух состояний элемента: на выходе элемента низкий уровень напряжения U0вых и на выходе высокий уровень U1вых.

Рис.7.1. Основные параметры логических элементов |

Передаточная характеристика — это зависимость выходного напряжения от входного, подаваемого на один из входов Uвых=f(Uвх). Характеристика определяется для заданного количества нагрузок на выходе элемента при подаче напряжения на один из входов, на остальные входы подают уровни «О» либо «1».

К основным статическим параметрам относятся напряжение логического нуля U0 и напряжение логической единицы U1 по входу и по выходу (рис.7.1). Под этими напряжениями принято понимать соответственно максимальное и минимальное значение, при которых схема находится в заданных состояниях. Запас помехоустойчивости характеризуется разностью между значениями выходного и входного сигналов данного уровня:

U1пом = U1вых — U1вх; U0пом = U0вых — U0вх

Динамические параметры и характеристики определяют быстродействие логического элемента. Параметры быстродействия определяют по временным диаграммам. На рис.7.1 представлены временные диаграммы для инвертирующего элемента. Важнейшим параметром быстродействия является время задержки распространения сигнала, определяемое как промежуток времени между прохождением уровня, соответствующего половине уровня логической единицы, входным и выходным сигналами. Различают время задержки распространения при переходе от логической единицы к нулю t10зд. р (промежуток между точками 2 и 5 на рис.7.1), время задержки распространения при переходе от уровня логического нуля к единице t01зд. р (промежуток между точками 9 и 11 на рис.7.1). Обобщающим является среднее время распространения

Параметры быстродействия определяют по временным диаграммам. На рис.7.1 представлены временные диаграммы для инвертирующего элемента. Важнейшим параметром быстродействия является время задержки распространения сигнала, определяемое как промежуток времени между прохождением уровня, соответствующего половине уровня логической единицы, входным и выходным сигналами. Различают время задержки распространения при переходе от логической единицы к нулю t10зд. р (промежуток между точками 2 и 5 на рис.7.1), время задержки распространения при переходе от уровня логического нуля к единице t01зд. р (промежуток между точками 9 и 11 на рис.7.1). Обобщающим является среднее время распространения

tзд. р.ср = (t10зд. р + t01зд. р)/2

Важное значение имеют также входные токи логического нуля I0вх и логической единицы I1вых, а также потребляемая мощность Pпот или токи потребления Iпот. К числу основных параметров относят также коэффициент объединения по входу Kоб, указывающий число входов элемента, и коэффициент разветвления Kраз, который показывает, сколько элементов такого же типа можно подсоединить к выходу.

Параметры элементов лабораторного макета

Тип элемента 155 (ТТЛ) 500 (ЭСЛ)

I0вх мА -1,6 0,0005

U0вх В 0,8 -1,83

I1вх мА 0,04 0,265

U1вх В 2 -0,86

U0вых В 0,4 -1,83 — -1,63

U1вых В 2,4 -0,90 — -0,72

Tзд. р.ср нс 18 2,9

Iпот. ср мА 15 25

R1 = 360 Ом R2 = 590 Ом R3 = 1 кОм

C1 = 50 пФ C2 = 200 пФ

Рабочее задание

1. Исследовать базовый логический элемент транзисторно-транзисторной логики (ТТЛ). Составить таблицу истинности элемента. Уровни «О» и «1», используемые при исследовании элемента, выведены на гнезда лабораторной панели.

1.1. Снять входную характеристику по схеме, приведенной на рис.7.2,а.

A | Б |

Рис.7.2. Схема для измерения входных характеристик элементов ТТЛ (а) и ЭСЛ (б). |

Полярность подключения миллиамперметра зависит от направления входного тока, втекающего или вытекающего из микросхемы.

1.2. Снять выходную характеристику элемента ТТЛ по схеме, приведенной на рис.7.3,а.

A | Б |

Рис.7.3. Схема для измерения выходных характеристик элементов ТТЛ (а) и ЭСЛ (б) |

Характеристика снимается при отключенной внешней нагрузке для двух состояний элемента — выключено U1вых и включено U0вых (состояние элемента определяют уровни напряжений, подаваемые на X1 и X2, в соответствии с таблицей истинности). В состоянии «элемент выключен», выходной ток вытекает из схемы, а в состоянии «элемент включен» — ток втекает в микросхему.

1.3. Снять передаточную характеристику Uвых=f(Uвх) по схеме рис.7.4,а.

A | Б |

Рис.7.4. Схема для измерения передаточных характеристик элементов ТТЛ (а) и ЭСЛ (б) |

Значение входного напряжения определяется по положению двух переключателей, дискретно регулирующих уровень напряжения на входе.

1.4. Определить параметры быстродействия (t10зд. р и t01зд. р ) по схеме, приведенной на рис.7.5,а.

Рис.7.5. Схема для измерения временных параметров логических элементов |

Параметры быстродействия определяются следующим образом. На вход исследуемой микросхемы подается прямоугольный импульс, снимаемый с выхода формирователя импульсов «ФИ». Формирователь импульсов запускается от внутреннего генератора (тумблер «запуск» в положении «внутр.»).С помощью осциллографа наблюдают и зарисовывают форму сигнала на входе и на выходе исследуемого логического элемента. Сигналы подаются на вход «Y» осциллографа через делитель. Можно использовать делитель, расположенный на лабораторном макете. Выходной сигнал подается на вход делителя, а вход осциллографа подключается к его выходу. Входной и выходной сигналы необходимо рисовать на графиках, масштабная сетка которых совпадает с сеткой, нанесенной на экране осциллографа. Осциллограф работает в ждущем режиме, внешний синхронизирующий сигнал снимается со входа формирователя импульсов и подается на вход «X» осциллографа. Период развертки на осциллографе устанавливается минимально возможным.

Осциллограф работает в ждущем режиме, внешний синхронизирующий сигнал снимается со входа формирователя импульсов и подается на вход «X» осциллографа. Период развертки на осциллографе устанавливается минимально возможным.

Параметры быстродействия определить для: 1)отсутствия нагрузки на выходе элемента; 2)Rн = 360 Ом; 3) Rн = 1 кОм; 4)Cн = 50 пФ; 5) Cн = 200 пФ.

2. Исследовать базовый логический элемент эмиттерно-связанной логики (ЭСЛ). Составить таблицу истинности элемента. Уровни «О» и «1», используемые при исследовании элемента, выведены на гнезда лабораторной панели.

2.1. Снять входную характеристику по схеме, приведенной на рис.7.2,б.

Полярность подключения миллиамперметра зависит от направления входного тока, втекающего или вытекающего из микросхемы.

2.2. Снять выходную характеристику элемента ЭСЛ по схеме, приведенной на рис.7.3,б. Характеристика снимается при отключенной внешней нагрузке для двух состояний элемента — выключено U1вых и включено U0вых (состояние элемента определяют уровни напряжений, подаваемые на X1 и X2, в соответствии с таблицей истинности). Зависимость Iвых=f(Uвых) снимается по обоим выходам схемы (инвертирующему и неинвертирующему)

Зависимость Iвых=f(Uвых) снимается по обоим выходам схемы (инвертирующему и неинвертирующему)

2.3. Снять передаточную характеристику Uвых=f(Uвх) по схеме рис.7.4,б. Передаточная характеристика также снимается по инвертирующему и неинвертирующему входам.

Краткие теоретические сведения

Перед выполнением и защитой лабораторной работы необходимо изучить основные параметры и характеристики логических элементов, а также принцип действия логических элементов на биполярных транзисторах.

Логическими элементами называются функциональные устройства, с помощью которых реализуются элементарные логические функции. Основой логического устройства является сложный электронный ключ. Этот ключ носит название базового логического элемента. В данной работе рассматриваются элементы, выполненные по биполярной технологии — ТТЛ и ЭСЛ.

Транзисторно-транзисторная логика наиболее распространена в современных вычислительных устройствах благодаря высокому быстродействию, высокой помехоустойчивости, умеренному энергопотреблению, хорошей нагрузочной способности и малой стоимости. Выходные и входные напряжения этих серий имеют так называемые стандартные уровни ТТЛ (U1=2,4·4,5 В, U0<0,4В) и одинаковые напряжения питания 5В. В этой серии выпускаются универсальные (К133,К155), повышенного быстродействия (К130, К131), быстродействующие с транзистором Шотки — ТТЛШ (К530, К531, К1531) и другие микросхемы.

Выходные и входные напряжения этих серий имеют так называемые стандартные уровни ТТЛ (U1=2,4·4,5 В, U0<0,4В) и одинаковые напряжения питания 5В. В этой серии выпускаются универсальные (К133,К155), повышенного быстродействия (К130, К131), быстродействующие с транзистором Шотки — ТТЛШ (К530, К531, К1531) и другие микросхемы.

Рис.7.6. Схема базового логического элемента транзисторно-транзисторной логики. |

Схема базового логического элемента ТТЛ серии К155 приведена на рис.7.6. Базовый элемент состоит из входного каскада на многоэмиттерном транзисторе VT1, выполняющим функцию «И», каскада управления выходными ключами на транзисторе VT2 и выходных ключей VT3, VT4, выполняющих функцию усиления и инвертирования. Часто второй и третий каскад объединяют вместе и называют сложным инвертором. При подаче на входы, или хотя бы на один из них, низкого уровня напряжения соответствующие эмиттерные переходы смещаются в прямом направлении. На любом из этих переходов падает О,7 В, чего явно недостаточно для отпирания трех последовательно включенных p-n переходов: коллекторный VT1, эмиттерные VT2 и VT4 Ток базы транзистора VT2, а следовательно, и ток базы транзистора VT4 равен нулю. Ток базы транзистора VT3 определяется резистором R2 и он открыт. При этом на выходе логического элемента присутствует высокий уровень напряжения. При подаче на все входы высокого уровня напряжения напряжения эмиттерные переходы VT1 смещены в обратном направлении. Напряжение питания открывает три перечисленных выше последовательных p-n перехода. Наличие коллекторного тока уменьшает ток базы транзистора VT3 до нуля. На выходе логического элемента действует напряжение открытого до режима насыщения транзистора VT4 — низкий уровень. В соответствии с приведенным описанием базовый логический элемент ТТЛ выполняет логическую функцию «И-НЕ». В современных логических элементах для защиты от выбросов напряжения на входе обычно ставятся диоды. Диод VD4 предназначен для надежного запирания транзистора VT3, так как падение напряжения на нем повышает потенциал эмиттера и напряжение база-эмиттер снижается.

В современных сериях широкое применение находят транзисторы Шотки. Как известно из принципа работы ключей на биполярных транзисторах, для предотвращения перехода транзистора в режим насыщения в них параллельно коллекторному переходу включается диод Шотки. Это, естественно, существенно повышает быстродействие.

Для расширения функциональных возможностей логических элементов у некоторых типов микросхем в серии на выходе установлен транзистор, коллекторная цепь которого остается свободной. Это логические элементы с открытым коллектором. При использовании в схеме в коллекторную цепь включается резистор, светодиод или любая другая нагрузка.

Еще одним своеобразным видом микросхем в ТТЛ сериях являются микросхемы с тремя устойчивыми состояниями. Третье состояние возникает при поступлении управляющего сигнала, когда выходные транзисторы оказываются запертыми, микросхема практически полностью отключена от нагрузки. Такое состояние называют высокоимпедансным.

Логические элементы эмиттерно-связанной логики имеют наибольшее быстродействие из всех широко распространенных логических элементов, выполненных из кремния по биполярной технологии. Для логических элементов этой группы характерны большая нагрузочная способность, независимость тока потребления от частоты переключения, небольшая энергия переключения. Высокое быстродействие ЭСЛ обеспечивается схемотехническим построением и выбором соответствующих режимов работы транзисторов. Благодаря глубокой отрицательной обратной связи на общем резисторе в цепи эмиттеров транзисторы не переходят в режим насыщения, а находятся в активном режиме. К недостаткам этой серии следует отнести большую потребляемую мощность и низкую помехоустойчивость. На основе ЭСЛ выпускаются микросхемы серий К5ОО и К15ОО, а также микропроцессорные БИС серии К18ОО. Эти серии микросхем, несколько отличаясь друг от друга схемотехническим построением, совместимы по уровням входных и выходных напряжений (U1=-0,9 В, U0=-1,7 В). Для повышения помехозащищенности коллекторы транзисторов заземляются, то есть на эмиттеры подается отрицательное напряжение питания — 5,2_В. В результате все логические уровни ЭСЛ находятся в отрицательной области и они непосредственно не совместимы с другими логическими схемами, что является недостатком этой серии. Также для повышения помехозащищенности разделяют шину земли эмиттерных повторителей и остальной схемы.

Рис.7.7. Схема базового логического элемента эмиттерно-связанной логики |

Схема базового элемента ЭСЛ серии К5ОО приведена на рис.7.7. Основой элемента служит входной дифференциальный каскад, выполненный на параллельно соединенных транзисторах VT1 и VT2, (левое плечо) и VT3 (правое плечо). В цифровой технике такой каскад получил название ключа на переключателе тока — токовый переключатель. Нагрузками каскада служат резисторы R3 и R5, в эмиттерную цепь включен токозадающий резистор R4. Напряжение на выходы Y1 и Y2 ЛЭ подается с выходов токового переключателя через эмиттерные повторители на транзисторах VT5 и VT6. В схему базового логического элемента ЭСЛ входит также источник опорного напряжения на транзисторе VT4, диодах VD1 и VD2 и резисторах R6-R8. Значение опорного напряжения относительно общей точки составляет — 1,3 В. Это напряжение подается на базу транзистора VTЗ. Использование диодов в схеме позволяет термостабилизировать рабочую точку транзистора, так как с ростом температуры одновременно с увеличением коллекторного тока транзистора VTЗ уменьшается падение напряжения на диодах и коллекторный ток возвращается к исходному значению.

Если на оба входа ЛЭ подан низкий уровень напряжения, то есть -1,7 В, то транзисторы VT1 и VT2 закрыты, а транзистор VTЗ открыт. При этом напряжение на коллекторах транзисторов VT1 и VT2 близко к напряжению источника питания. Это высокое напряжение передается на выход Y2 через эмиттерный повторитель на транзисторе VT5. Причем его уровень представляет собой нормализованный высокий уровень этой серии, то есть -0,9 В. При этом через транзистор VT3 протекает ток коллектора, задаваемый резистором R4 и напряжение на коллекторе этого транзистора определяется падением напряжения на резисторе R2. Этот низкий уровень напряжения передается на выход Y1 через эмиттерный повторитель на транзисторе VT6 и составляет, как и ожидается -1,7 В. Если на один из входов либо на два входа одновременно подано напряжение большее, чем опорное напряжение на базе транзистора VT3, а именно -1,7 В, то левое плечо токового ключа начинает пропускать ток и транзистор VTЗ закрывается. В результате теперь уже на выходе Y1 появится высокий уровень. Соответственно транзисторы VT1 и VT2 теперь будут открыты, а на выходе Y2 появится низкий уровень. Таким образом, базовый элемент ЭСЛ выполняет функцию «ИЛИ-НЕ» по выходу Y2 (инвертирующий выход) и функцию «ИЛИ» по выходу Y1 (неинвертирующий выход).

Поскольку рассматриваемый элемент выполняет логическую функцию «ИЛИ», то в случае использования при работе части входов на неиспользуемые входы необходимо подавать напряжение логического «О» — низкий уровень. В базовом логическом элементе это достигается включением на входе резисторов R1 и R2. Их сопротивление достаточно велико (100 кОм), так что они практически не влияют на статические характеристики элемента.

В большинстве случаев в качестве эмиттерного сопротивления выходного эмиттерного повторителя служит сопротивление нагрузки или входное сопротивление следующего каскада. При этом, кроме улучшения коэффициента передачи эмиттерного повторителя, появляется возможность реализации операции монтажного ИЛИ. Это осуществляется непосредственным соединением выходов двух микросхем, то есть при появлении сигнала на выходе одной из микросхем тот же потенциал поддерживается и на их соединении. В результате при прежнем количестве микросхем удается реализовать большее число функций.

Чтобы еще более расширить функциональные возможности элемента ЭСЛ, применяется двух — или трехуровневое переключение тока. Для этого на входе ставится эмиттерный повторитель, позволяющий сдвинуть уровнь входного сигнала до значений, необходимых для переключения логического элемента. При этом ток может переключаться несколько раз, в зависимости от уровней смещения во входных эмиттерных повторителях.

Для понимания хода характеристик необходимо разобраться, в каком состоянии (открытом или закрытом) находятся входные и выходные транзисторы схемы, после чего ход характеристик легко можно понять на основании закона Ома.

Записи по теме

| Подробная информация о производителях — в GUIDE’е, о типах корпусов — здесь | |||||

| код | наименование | функция | корпус | производитель | примечания |

|---|---|---|---|---|---|

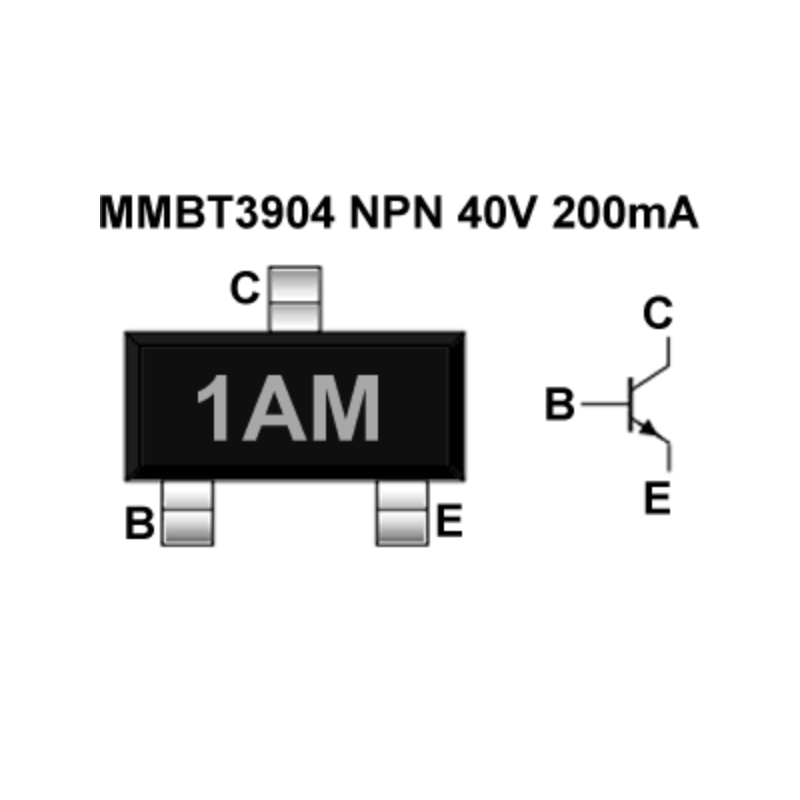

| Y1 | BZX84-C11 | стабилитрон 11В, 250мВт | sot23 | Fairchild, Taiwan Semi, Diodes | |

| Y1 | SS8050/W | npn: 25В/1,5А | sot23/323 | Galaxy Semi | |

| Y1## | R1210N512C | повышающий dc-dc: 5,1В 100кГц +LTD | sot23-5 | Ricoh | ## — lot-код |

| Y10 | BZX84-C27 | стабилитрон 27В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y11 | BZX84-C30 | стабилитрон 30В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y12 | BZX84-C33 | стабилитрон 33В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y13 | BZX84-C36 | стабилитрон 36В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y14 | BZX84-C39 | стабилитрон 39В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y15 | BZX84-C43 | стабилитрон 43В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y16 | BZX84-C47 | стабилитрон 47В, 250мВт | sot23 | Taiwan Semi, NXP | |

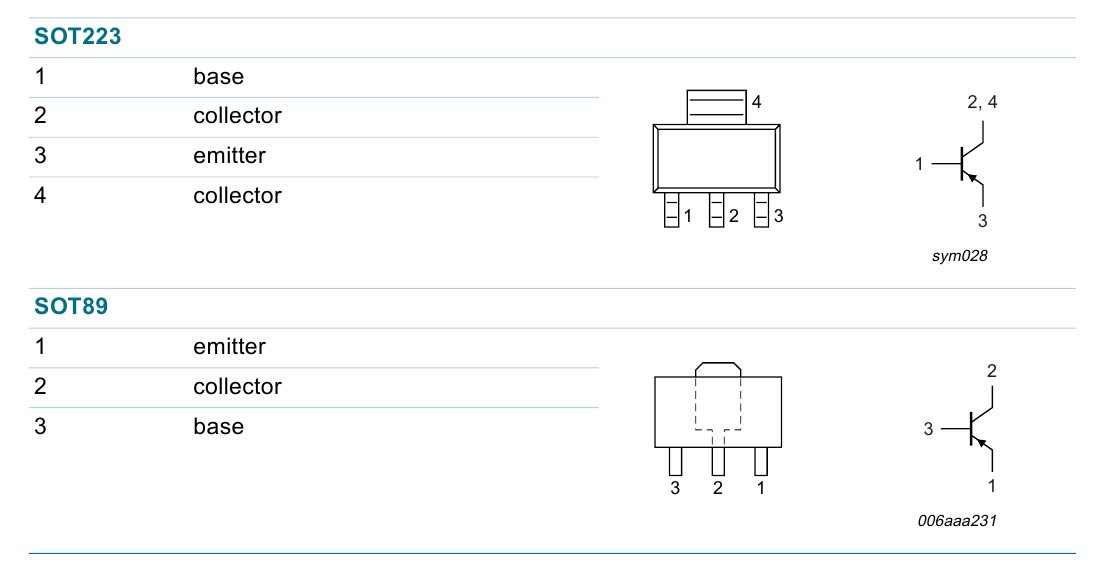

| Y1766 | 2SC1766 | npn: 50В/2А h31=180…390 | sot89 | Galaxy Semi | |

| Y17 | BZX84-C51 | стабилитрон 51В, 250мВт | sot23 | Taiwan Semi, NXP | |

| Y18 | BZX84-C56 | стабилитрон 56В, 250мВт | sot23 | NXP | |

| Y19 | BZX84-C62 | стабилитрон 62В, 250мВт | sot23 | NXP | |

| Y1p | BZX84-C11 | стабилитрон 11В, 250мВт | sot23 | NXP | @Hong Kong |

| Y1t | BZX84-C11 | стабилитрон 11В, 250мВт | sot23 | NXP | @Malaysia |

| Y1W | BZX84-C11 | стабилитрон 11В, 250мВт | sot23 | NXP | @China |

uxcell 150pcs SS8050 Транзистор Y1 NPN 25V 1500mA 300mW поверхностный монтаж SOT-23: Amazon.com: Industrial & Scientific

В настоящее время недоступен.

Мы не знаем, когда и появится ли этот товар в наличии.

- Убедитесь, что это подходит введя номер вашей модели.

- Название продукта: Транзистор СОТ23;

- Ic: 1500 мА; Vceo: 25 В; HFE: 120-350; PCM: 300 мВт; Модель: SS8050-Y1; Тип транзистора: NPN; Материал: пластик, электронные компоненты

- Широко используется в области цепи переключения, бессвинцовый / электронный компонент / поверхностный монтаж

- Возможность высокого прямого импульсного тока / высокотемпературная пайка / низкие потери мощности, высокая эффективность

- Содержание упаковки: 150 (+/- 2%) шт. X транзистор SOT23

Характеристики данного продукта

| Фирменное наименование | uxcell |

|---|---|

| Номер детали | a18071200ux0706 |

| Спецификация соответствует | Rohs |

| Код UNSPSC | 41000000 |

% PDF-1.3 % 796 0 объект > эндобдж xref 796 276 0000000016 00000 н. 0000005873 00000 н. 0000036983 00000 п. 0000037142 00000 п. 0000037290 00000 п. 0000037557 00000 п. 0000037865 00000 п. 0000038170 00000 п. 0000038452 00000 п. 0000038633 00000 п. 0000038887 00000 п. 0000039059 00000 п. 0000039267 00000 п. 0000039458 00000 п. 0000039706 00000 п. 0000039931 00000 н. 0000040228 00000 п. 0000040527 00000 п. 0000040761 00000 п. 0000041004 00000 п. 0000041175 00000 п. 0000041439 00000 п. 0000041604 00000 п. 0000041800 00000 п. 0000042088 00000 п. 0000042346 00000 п. 0000042611 00000 п. 0000042890 00000 н. 0000043166 00000 п. 0000043421 00000 п. 0000043637 00000 п. 0000043894 00000 п. 0000044070 00000 п. 0000044261 00000 п. 0000044564 00000 п. 0000044781 00000 п. 0000045017 00000 п. 0000045220 00000 п. 0000045474 00000 п. 0000045726 00000 п. 0000045932 00000 п. 0000046178 00000 п. 0000046428 00000 н. 0000046643 00000 п. 0000046944 00000 п. 0000047162 00000 п. 0000047439 00000 п. 0000047748 00000 п. 0000048035 00000 п. 0000048258 00000 п. 0000048566 00000 п. 0000048815 00000 н. 0000049058 00000 н. 0000049298 00000 п. 0000049595 00000 п. 0000049848 00000 п. 0000050096 00000 п. 0000050359 00000 п. 0000050719 00000 п. 0000051085 00000 п. 0000051438 00000 п. 0000051611 00000 п. 0000051830 00000 п. 0000052094 00000 п. 0000052368 00000 п. 0000052660 00000 п. 0000052951 00000 п. 0000053330 00000 п. 0000053721 00000 п. 0000054020 00000 п. 0000054216 00000 п. 0000054419 00000 п. 0000054764 00000 н. 0000054931 00000 п. 0000054983 00000 п. 0000055209 00000 п. 0000055427 00000 п. 0000055769 00000 п. 0000056151 00000 п. 0000056455 00000 п. 0000056829 00000 п. 0000057115 00000 п. 0000057441 00000 п. 0000057781 00000 п. 0000058071 00000 п. 0000058426 00000 п. 0000058967 00000 п. 0000059289 00000 п. 0000059593 00000 п. 0000059957 00000 н. 0000060387 00000 п. 0000060600 00000 п. 0000060806 00000 п. 0000061042 00000 п. 0000061094 00000 п. 0000061392 00000 п. 0000061629 00000 п. 0000061861 00000 п. 0000062159 00000 п. 0000062339 00000 п. 0000062542 00000 п. 0000062786 00000 п. 0000063148 00000 п. 0000063388 00000 п. 0000063643 00000 п. 0000063942 00000 п. 0000064185 00000 п. 0000064412 00000 п. 0000064644 00000 п. 0000064926 00000 п. 0000065214 00000 п. 0000065513 00000 п. 0000065788 00000 п. 0000066035 00000 п. 0000066321 00000 п. 0000066533 00000 п. 0000066780 00000 п. 0000067022 00000 п. 0000067240 00000 п. 0000067442 00000 п. 0000067651 00000 п. 0000067819 00000 п. 0000068009 00000 п. 0000068176 00000 п. 0000068379 00000 п. 0000068640 00000 п. 0000068830 00000 н. 0000069030 00000 н. 0000069211 00000 п. 0000069383 00000 п. 0000069621 00000 п. 0000069863 00000 п. 0000070112 00000 п. 0000070386 00000 п. 0000070628 00000 п. 0000070868 00000 п. 0000071075 00000 п. 0000071289 00000 п. 0000071490 00000 п. 0000071729 00000 п. 0000071914 00000 п. 0000072117 00000 п. 0000072304 00000 п. 0000072528 00000 п. 0000073729 00000 п. 0000074308 00000 п. 0000074481 00000 п. 0000074706 00000 п. 0000074931 00000 п. 0000075091 00000 п. 0000075270 00000 п. 0000075449 00000 п. 0000075647 00000 п. 0000075840 00000 п. 0000076052 00000 п. 0000076301 00000 п. 0000076541 00000 п. 0000076769 00000 п. 0000076977 00000 п. 0000077186 00000 п. 0000077384 00000 п. 0000077552 00000 п. 0000077744 00000 п. 0000077924 00000 п. 0000078112 00000 п. 0000078281 00000 п. 0000078445 00000 п. 0000078654 00000 п. 0000078853 00000 п. 0000079045 00000 п. 0000079215 00000 п. 0000079431 00000 п. 0000079647 00000 п. 0000079825 00000 п. 0000080015 00000 п. 0000080297 00000 п. 0000080580 00000 п. 0000080776 00000 п. 0000081069 00000 п. 0000081329 00000 п. 0000081593 00000 п. 0000081806 00000 п. 0000082061 00000 п. 0000082348 00000 п. 0000083153 00000 п. 0000083410 00000 п. 0000083608 00000 п. 0000083874 00000 п. 0000084392 00000 п. 0000084444 00000 п. 0000084858 00000 н. 0000085113 00000 п. 0000085286 00000 п. 0000085495 00000 п. 0000085676 00000 п. 0000085915 00000 п. 0000086079 00000 п. 0000086346 00000 п. 0000086571 00000 п. 0000086784 00000 п. 0000087002 00000 п. 0000087254 00000 п. 0000087476 00000 п. 0000087729 00000 п. 0000087963 00000 п. 0000088162 00000 п. 0000088371 00000 п. 0000088529 00000 п. 0000088704 00000 п. 0000088878 00000 н. 0000089053 00000 п. 0000089216 00000 п. 0000089456 00000 п. 0000089697 00000 п. 0000089920 00000 н. 00000 00000 п. 00000 00000 п. 00000 00000 п. 0000093023 00000 п. 0000093238 00000 п. 0000093432 00000 п. 0000093685 00000 п. 0000093962 00000 п. 0000094181 00000 п. 0000094402 00000 п. 0000094674 00000 п. 0000094921 00000 п. 0000095166 00000 п. 0000095389 00000 п. 0000095660 00000 п. 0000095905 00000 п. 0000096167 00000 п. 0000096404 00000 п. 0000096678 00000 н. 0000096842 00000 п. 0000097008 00000 п. 0000097272 00000 п. 0000097325 00000 п. 0000097566 00000 п. 0000097838 00000 п. 0000098047 00000 п. 0000098290 00000 п. 0000098556 00000 п. 0000098791 00000 п. 0000098988 00000 п. 0000099236 00000 п. 0000099414 00000 н. 0000099924 00000 н. 0000100122 00000 н. 0000100329 00000 н. 0000100547 00000 н. 0000100771 00000 н. 0000100969 00000 н. 0000101175 00000 п. 0000101872 00000 н. 0000102080 00000 н. 0000102302 00000 п. 0000102523 00000 н. 0000102728 00000 н. 0000102962 00000 н. 0000103183 00000 п. 0000103415 00000 н. 0000103643 00000 п. 0000103838 00000 п. 0000104049 00000 н. 0000104258 00000 н. 0000104487 00000 н. 0000104717 00000 н. 0000104924 00000 н. 0000105140 00000 н. 0000105363 00000 п. 0000105598 00000 п. 0000105796 00000 н. 0000105989 00000 п. 0000005930 00000 н. 0000036958 00000 п. трейлер ] >> startxref 0 %% EOF 797 0 объект > эндобдж 1070 0 объект > транслировать HTY8 5! CK% DRQKBDFZMU ڢ 7] kJoph ע E + Z5b2 [\ Դ

Улучшенное усиление и работа вентилятора в полностью магнитном транзисторе

Круглый диск диаметром 200 нм и толщиной 40 нм, состоящий из Ni 80 Fe 20 (Py) используется для образования стабильного магнитного вихря.Система связанных двух вихрей формируется путем размещения другого диска Py того же размера рядом с первым диском, и аналогичным образом система из трех вихрей формируется путем размещения трех таких дисков в ряд. На рис. 1 (a, b) показаны связанные двух- и трех-вихревые системы с полярностями ядра (+1, −1) и (+1, −1, −1) соответственно. Усредненная по пространству x-составляющая намагниченности рассматривается как индикатор смещения сердечника от его положения равновесия. Квадрат амплитуды преобразования Фурье рассматривается как спектральная плотность энергии (ESD), которая показывает пиковую мощность, соответствующую максимальному смещению сердечника.

Рисунок 1Конфигурация спина в основном состоянии магнитного диска диаметром 200 нм и толщиной 40 нм, расположенных в связанных ( a ) двух вихревых системах с междисковым разделением ( S ) 10 нм и ( b ) трехвихревую систему с разделением между левым и центральным вихрями ( S 1) 10 нм и разделением между центральным и правым вихрями ( S 2) 100 нм.

Пара связанных вихрей

Перед оптимизацией усиления MVT и других связанных операций MVT мы исследовали коэффициент передачи энергии в системе связанных двух вихрей как функцию разделения между дисками.На рисунке 2 (а) показаны ESD для левого и правого вихря для связанных двух вихревых систем с четырьмя различными расстояниями между дисками. Здесь только левый вихрь возбуждается локальным полем. Для больших расстояний (60 и 100 нм) наблюдается одна мода гирации, а для более низких расстояний наблюдаются три связанные моды. Расщепление мод представляет собой интересную проблему и подробно изучено в предыдущей литературе 11,12,13,35,36 . Однако здесь учитывается только центральный пик, соответствующий самому высокому значению электростатического разряда, для расчета усиления передачи энергии.Коэффициент усиления рассчитывается как разница между максимальным значением ESD правого и левого вихря. Для всех четырех разнесений наблюдается большой выигрыш. Коэффициент усиления ( B ) систематически изображен как функция расстояния между дисками ( S ) на рис. 2 (b). Здесь B показывает почти линейный рост с уменьшением S и достигает 25,55 дБ при S = 60 нм. Для S <60 нм, B внезапно снижается до 22,77 дБ, за которым следует еще один более резкий рост до S = 10 нм, где он достигает максимального значения насыщенности 42.15 дБ и дальше не увеличивается. Чтобы оправдать выбор полярностей сердцевины, мы изменили полярности сердцевины связанной вихревой системы с расстояниями S = 10 нм и 60 нм на (+1, +1) и наблюдали значительно меньшее усиление в последних случаях. (22,0 дБ для S = 10 нм и 7,0 дБ для S = 60 нм) по сравнению с 42,15 дБ ( S = 10 нм) и 22,77 дБ ( S = 60 нм) для первых случаев. Более подробные сведения об этом наблюдении можно найти на дополнительном рисунке 1S (а).

Рисунок 2( a ) Энергетические спектральные плотности (ESD) для связанных двух вихревых систем с различным междисковым расстоянием ( S ). ( b ) Изменение усиления ( B ) с S для связанного вихря.

Чтобы понять это немонотонное увеличение B с S , мы изучили временную эволюцию паразитного магнитного поля. На рисунке 3 (а) показано распределение поля рассеяния одиночного вихря в два разных момента времени (t = 0 и 5 нс), и ясно, что распределение поля рассеяния изменяется со временем, когда ядро вихря начинает вращаться даже при одиночный вихрь.На рисунке 3 (b) показаны снимки смоделированных полей рассеяния для четырех различных двух вихревых систем в определенные моменты времени динамики. Дополнительные фильмы M1 – M4 подробно показывают динамику. Более ранние работы показали, что передача энергии от левого вихря к правому опосредуется антивихрями рассеянного поля, которые движутся от левого диска и сталкиваются с правым диском. Это также подразумевается в исх. 39 из единственного изученного случая , то есть S = 50 нм, усиление происходит, когда между двумя дисками отсутствует петля обратной связи антивихревой траектории поля рассеяния.Обратная связь вызывает перебалансировку энергии и препятствует усилению. Однако подробное исследование изменения коэффициента усиления в зависимости от расстояния между дисками, представленное здесь, показывает, что усиление может происходить даже при наличии петли обратной связи и даже когда антивихрь не сталкивается напрямую с правым вихрем. Для S = 100 нм антивихрь генерируется после начала динамики и проходит через зазор между двумя дисками без единого столкновения ни с одним из дисков, а энергия передается только за счет изменения силовых линий с время, что дает выигрыш 17.80 дБ. С уменьшением S, столкновение антивихря начинает происходить с обоими дисками, что приводит к усилению передачи энергии, хотя и с обратной связью, которая препятствует очень большому значению усиления. Механизм обратной связи ослабевает с дальнейшим уменьшением S , вызывая непрерывное увеличение значения усиления. Однако для S , близкого к 60 нм, возникает особая ситуация, когда антивихрь рассеянного поля присутствует даже в основном состоянии до начала динамики, как показано желтым кружком на рис.3 (c), и передача энергии происходит сразу после начала динамики, вызывая дальнейшее ослабление механизма обратной связи. Однако, когда S значительно отклоняется от 60 нм, этот антивихрь исчезает из основного состояния, и передача энергии начинается после создания антивихря рассеянного поля после начала вращения в левом вихре. По мере дальнейшего уменьшения S механизм обратной связи и последующая перебалансировка энергии исчезают, а односторонняя передача энергии от левого вихря к правому вызывает накопление энергии в правом вихре и происходит усиление усиления.Это продолжает увеличиваться с дальнейшим снижением S из-за более быстрой передачи энергии. Наконец, насыщение происходит при S ≤ 10 нм, когда очень высокая энергия дипольного взаимодействия между ближайшими краевыми областями дисков запрещает антивихрю входить в эту зону, и он передает энергию только в нижней половине диска.

Рис. 3Показаны распределения поля рассеяния для одиночного вихря ( a ) в момент времени t = 0 и 5 нс и ( b ) двух магнитостатически связанных вихревых систем с четырьмя различными расстояниями между дисками.Зелеными стрелками показаны пути антивихревых солитонов. ( c ) Показана конфигурация поля рассеяния в основном состоянии магнитостатически связанной двухвихревой системы с междисковым расстоянием 60 нм при t = 0 нс, а антивихрь отмечен желтым кружком. Цветные полосы показаны внизу рисунка. Раскраска контура основана на сумме квадратов компонентов x и y паразитного поля, а цветовая полоса отображается в дБ. Ядро вихря отмечено синей точкой.

Магнитный вихревой транзистор (MVT)

Для работы MVT мы начинаем с последовательности из трех вихрей с поляризациями +1, -1 и -1, которая успешно работала в нашей предыдущей работе 39 . Здесь мы варьируем расстояние между левым и средним вихрями ( S1 ) и средним и правым вихрями ( S2 ), чтобы оптимизировать усиление B . В симметричном MVT максимальный достигнутый коэффициент усиления составил 14,8 дБ для S1 = S2 = 50 нм 39 .Основываясь на моделировании путем систематического изменения значений S1 и S2 , мы показываем здесь, что введение асимметрии в расположении трех вихрей приводит к повышенному усилению в MVT, и усиление может поддерживаться в сложных схемах вдоль различных ветвей. . Асимметрия достигается за счет того, что расстояние между центральным вихрем и правым вихрем ( S2 ) больше, чем между левым вихрем и средним вихрем ( S1 ). Оптимальное значение достигается установкой S1 = 10 нм, что обеспечивает максимальное усиление для системы связанных двух вихрей.Различные аспекты динамики MVT были представлены на рисунках 4 и 5. На рисунке 4 (а) показаны ESD MVT для S1 = 10 нм и для S2 в диапазоне от 10 до 175 нм. Рисунок 4 (b) показывает, что усиление увеличивается с увеличением S2 , и максимум 28,28 дБ наблюдается на S2 = 100 нм, за пределами которого он уменьшается при дальнейшем увеличении S2 . Это двукратное увеличение коэффициента усиления AMVT замечательно и может привести к применению в магнитоэлектронных схемах, требующих усиления сигнала.Чтобы оправдать выбор полярности сердцевины, мы изменили полярности сердцевины трех вихревой системы с расстояниями S1 = 10 нм и S2 = 100 нм на (+1, +1, +1), (+1, + 1, −1) и (+1, −1, +1). Мы наблюдали намного меньшее усиление в этих комбинациях полярностей сердечника по сравнению с первым случаем (+1, -1, -1). Коэффициент усиления выходного вихря составляет -4,5 дБ, 5,0 дБ и 16,5 дБ для комбинации полярностей (+1, +1, +1), (+1, +1, -1) и (+1, -1, +1 ), соответственно. Более подробные сведения об этом наблюдении можно найти на дополнительном рисунке 1S (b).Чтобы понять связь между усилением MVT и относительным смещением ядра ( r = смещение ядра вихря в диске 3 — смещение ядра вихря в диске 1), мы построили график на рис. 4 (c), r как функция S2 для некоторых выбранных значений S2 . Аналогичный характер изменения относительного смещения сердечника с S2 наблюдается и с изменением коэффициента усиления B . Чтобы понять это усиление, мы снова исследовали временную эволюцию магнитного поля рассеяния, как показано на рис.5, а более подробную информацию о динамике можно найти в дополнительных фильмах M5 – M10. Мы видим, что механизм передачи энергии от левого вихря к центру для всех случаев такой же, как и в системе связанных двух вихрей с S1 = 10 нм. Однако механизм переноса от центра к правому вихрю меняется с S2 . Следовательно, окончательное усиление вихревого транзистора определяется динамикой поля рассеяния между центром и правым вихрем. При S1 = S2 = 10 нм антивихри, созданные между центром и правым вихрем, очень малы по размеру и, следовательно, очень мало энергии передается правому вихрю, что приводит к меньшему усилению 14.76 дБ. По мере увеличения S2 создаются более крупные антивихри, и они проходят почти эллиптические пути через поле рассеяния между центром и правым вихрем. Длина главной оси этого эллиптического пути, по-видимому, определяет количество передаваемой энергии, и она представлена как функция S2 на рис. 4 (d). Ясно, что эта длина увеличивается с увеличением S2 и достигает максимума при S2 = 100 нм, за которым она падает. Это изменение согласуется с изменением усиления и, следовательно, мы считаем, что они сильно коррелированы.Далее мы исследовали изменение коэффициента усиления оптимизированной структуры AMVT ( S1 = 10 нм и S2 = 100 нм) с амплитудой входного сигнала h 0 . На рисунке 4 (е) показан график изменения коэффициента усиления от логарифма амплитуды сигнала h 0 . Здесь ядро левого вихря перевернулось за ч 0 = 5 мТл, поэтому мы ограничиваемся 4 мТл. Для более низких значений h 0 , усиление остается почти постоянным на уровне B active = 28.28 дБ. Это считается активной областью AMVT, и B активный напоминает усиление слабого сигнала электронного транзистора с биполярным переходом. При 5 мТл ядро левого вихря переключается, и усиление внезапно падает, определяя область отсечки. В отличие от симметричного MVT нелинейное искажение усиления от B активного при более высоком уровне сигнала (до отсечки) в AMVT не наблюдается.

Рисунок 4( a ) ESD для MVT и AMVT.( b ) Изменение усиления ( B ) с S2 для AMVT. ( c ) Изменение относительного смещения ядра ( r ) правого вихря относительно левого вихря с S2 для AMVT. ( d ) Изменение длины большой оси эллипса с S2 для AMVT. ( e ) Изменение усиления ( B ) в зависимости от силы приложенного магнитного поля.

Рисунок 5Профили случайного поля для MVT и AMVT.

Зеленые линии представляют собой траектории антивихревых солитонов. Цветные полосы показаны внизу рисунка. Раскраска контура основана на сумме квадратов компонентов x и y паразитного поля, а цветовая полоса отображается в дБ.

Fan-Out

Симметричный MVT не показал успешной операции разветвления, поскольку антивихревой солитон не легко расщепляется, что приводит к асимметрии в передаче энергии в двух плечах схемы разветвления. Здесь мы исследуем возможность разветвления с помощью AMVT.Оптимизированный AMVT с горизонтальным расстоянием между левым и центральным вихрями ( S x1 ) как 10 нм и между центральным и правым вихрями ( S x2 ) как 100 нм с аналогичным ядром полярность (+1, -1, -1) как AMVT используется здесь как единица измерения. Мы разместили два AMVT вертикально выше и ниже исходного AMVT, сохраняя левый вихрь верхней и нижней ветвей и правый вихрь исходной AMVT на одной линии и варьируя вертикальные расстояния верхнего ( S y1 ) и ниже ( S y2 ) AMVT со входом AMVT для настройки усиления на двух выходах.Электростатические разряды и профили поля рассеяния для цепей разветвления с различными значениями S y1 и S y2 показаны на рис. 6. Подробная временная эволюция магнитных полей рассеяния представлена в дополнительных фильмах M11 – M13.

Рисунок 6( a – c ) ESD для операции разветвления. ( d – f ) Профили рассеянного поля для разветвления. Зеленые линии представляют собой пути солитонов антивихря, а антивихри отмечены зелеными и фиолетовыми кружками.Время взаимодействия (T) указано на каждом рисунке. Цветовая полоса показана внизу рисунка. Раскраска контура основана на сумме квадратов компонентов x и y паразитного поля, а цветовая полоса отображается в дБ.

Сначала мы начали с симметричной схемы разветвления, установив S y1 = S y2 = 50 нм. Усиление наблюдается на обоих выходах (O1 и O2), но усиление в верхней ветви намного выше, чем усиление в нижней ветви ( B O1 — B O2 = 6.33 дБ). Чтобы устранить эту асимметрию в усилении, мы ввели второй уровень асимметрии в схему разветвления. Систематическое изменение S y1 и S y2 показывает, что для S y1 = 50 нм и S y2 = 30 нм ESD на O1 и O2 почти одинаковы, и, следовательно, прирост также одинаков: B O1 = B O2 = 5.4 дБ. При дальнейшем уменьшении S y2 усиление O2 становится выше, чем O1. Рисунок 6 (c) показывает, что B O2 — B O1 = 2,77 дБ.

Чтобы понять это поведение, мы подробно изучили динамику поля рассеяния (рис. 6 (d – f)) схем разветвления. Наблюдается движение антивихревого солитона от левого вихря верхнего AMVT к левому вихрю нижнего AMVT через правый вихрь входного AMVT.Размер и скорость этого антивихревого солитона и время взаимодействия (T) с правым вихрем входного AMVT определяются степенью асимметрии в структуре. Для первого случая, показанного здесь ( S y1 = S y2 = 50 нм), четыре антивихря, отмеченные фиолетовыми кружками, наблюдаются вблизи среднего и правого вихрей верхнего и нижнего AMVT. (Рис. 6 (d)). Среди этих четырех антивихрей два расположены между правым вихрем верхнего и нижнего AMVT.Более крупный антивихрь неподвижен на полпути между правым вихрем верхней и нижней ветвей AMVT, а меньший движется к правому вихрю верхней ветви AMVT. В результате верхний AMVT (O2) показывает более высокое усиление для симметричной схемы разветвления.

В случае успешного разветвления ( S y1 = 50 нм, S y2 = 30 нм) механизм передачи энергии отличается от такового в симметричном случае.Здесь мы наблюдаем три антивихря, отмеченные фиолетовыми кружками вблизи среднего и правого вихрей верхней и нижней ветвей (рис. 6 (е)). Два из них сначала объединяются, а затем снова разделяются на два антивихря. Эти два антивихря движутся к правому вихрю верхней и нижней ветвей AMVT и передают энергию одинаково. В третьем случае ( S y1 = 50 нм, S y2 = 10 нм), помимо упомянутых антивихрей, около правого вихря нижнего ветвь (отмечена фиолетовыми кружками), в результате чего передача энергии в нижней ветви значительно выше по сравнению с двумя предыдущими случаями (рис.6 (е)).

В дополнение к распределению энергии между двумя выходами в схеме разветвления мы также наблюдаем интересную тенденцию в сумме энергии, передаваемой на два выхода, и ее связи с динамикой антивихревого поля рассеяния. Когда S y1 = S y2 , антивихревой солитон, отмеченный зеленым кружком, довольно большой и очень быстро перемещается между двумя ветвями (время взаимодействия T ≈ 0,55 нс). В результате сумма выходных усилений велика (O1 + O2 = 12.71 дБ). Когда мы нарушаем симметрию, слегка приподнимая нижнюю ветвь к входу AMVT, сумма усилений уменьшается до 11,67 дБ. В этом случае размер антивихревого солитона (отмечен зеленым кружком), движущегося от левого вихря верхней ветви AMVT к левому вихрю нижней ветви AMVT через правый вихрь входного AMVT, несколько уменьшается по сравнению с размером антивихревого вихря входного AMVT. симметричная схема разветвления. Время взаимодействия (T) около 0,51 нс почти такое же, как и для симметричного случая, и сумма коэффициентов усиления также аналогична.По мере дальнейшего увеличения асимметрии ( S y2 = 10 нм) размер антивихря уменьшается (отмечен зеленым кружком), и он очень медленно перемещается между левым вихрем верхней и нижней ветвей цепь через правый вихрь входа AMVT (время взаимодействия, T ≈ 1.02 нс). В результате сумма коэффициентов усиления на двух выходных ветвях значительно уменьшается (O1 + O2 = 6,31 дБ).

Патент США на схемный модуль для моделирования цифровой схемы и устройства моделирования, включая Патент на схемный модуль (Патент №10,783302, выданный 22 сентября 2020 г.)

ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИНастоящая заявка испрашивает приоритет по 35 U.§ 119 (a) S.C. к заявке на патент Кореи № 10-2018-0079299, поданной 9 июля 2018 г., которые полностью включены в настоящий документ посредством ссылки.

Уровень техники 1. Область техникиРазличные варианты осуществления в целом относятся к схемному модулю для моделирования цифровой схемы и устройству моделирования, включающему схемный модуль.

2. Уровень техникиБыли разработаны различные методы моделирования работы цифровой схемы в соответствии с переходом входного сигнала.

Коммерческие микросхемы включают в себя большое количество цифровых схем. Симуляция Spice, которая обычно используется, требует очень много времени для симуляции. Следовательно, очень сложно проверить работу микросхемы при низкой скорости моделирования. Соответственно, существует потребность в методике эффективного сокращения времени моделирования цифровой схемы.

КРАТКОЕ ОПИСАНИЕВ соответствии с настоящими идеями, схемный модуль включает в себя модельную схему, сконфигурированную для генерации выходного сигнала на основе одного или нескольких входных сигналов и соответствующих цифровой схеме, и справочную таблицу (LUT), хранящую один или несколько управляющих сигналов и один или несколько рабочих параметров, которые должны использоваться для реализации модельной схемы, один или несколько управляющих сигналов и один или несколько рабочих параметров, соответствующих индексу, определенному комбинацией одного или нескольких входных сигналов и выходной сигнал.

В соответствии с настоящими идеями устройства моделирования включают в себя схему модели, сконфигурированную для генерации выходного сигнала на основе одного или нескольких входных сигналов и соответствующие цифровой схеме, справочную таблицу (LUT), хранящую один или несколько сигналов управления. и один или несколько рабочих параметров, которые должны использоваться для реализации модельной схемы, один или несколько управляющих сигналов и один или несколько рабочих параметров, соответствующих индексу, определенному комбинацией одного или нескольких входных сигналов и выходного сигнала, и схему управления, сконфигурированную для моделирования цифровой схемы путем управления схемой модели и LUT.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙСопроводительные чертежи, на которых одинаковые ссылочные позиции относятся к идентичным или функционально подобным элементам на отдельных изображениях, вместе с подробным описанием, приведенным ниже, включены в описание и составляют его часть и служат для дальнейшего иллюстрируют варианты осуществления концепций, которые включают заявленную новизну, и объясняют различные принципы и преимущества этих вариантов осуществления.

РИС. 1 показана блок-схема, иллюстрирующая цифровую схему.

РИС. 2 показывает блок-схему, иллюстрирующую устройство моделирования согласно варианту осуществления настоящего раскрытия.

РИС. 3 и 4 показаны принципиальные схемы, иллюстрирующие схемы с переменной задержкой согласно вариантам осуществления настоящего раскрытия.

РИС. 5-8 показывают таблицы, иллюстрирующие структуру справочной таблицы (LUT) согласно варианту осуществления настоящего раскрытия.

РИС. 9 показывает блок-схему, иллюстрирующую способ создания схемного модуля согласно варианту осуществления настоящего раскрытия.

РИС. 10 показывает пример моделирования согласно варианту осуществления настоящего раскрытия.

РИС. 11 показывает график, иллюстрирующий работу устройства моделирования согласно варианту осуществления настоящего раскрытия.

РИС. 12 показывает блок-схему, иллюстрирующую цифровую схему, имеющую множество выходных сигналов, согласно варианту осуществления настоящего раскрытия.

РИС. 13 показывает блок-схему, иллюстрирующую эквивалентную цифровую схему цифровой схемы, показанной на фиг.12 согласно варианту осуществления настоящего раскрытия.

ПОДРОБНОЕ ОПИСАНИЕСледующее подробное описание ссылается на сопроводительные чертежи в описании иллюстративных вариантов осуществления, согласующихся с этим раскрытием. Варианты осуществления представлены в иллюстративных целях и не являются исчерпывающими. Возможны дополнительные варианты осуществления, не проиллюстрированные или не описанные явно. Кроме того, в представленные варианты осуществления могут быть внесены модификации в рамках настоящего изобретения.Подробное описание не предназначено для ограничения этого раскрытия. Скорее, объем настоящего раскрытия определяется в соответствии с представленной формулой изобретения и ее эквивалентами.

РИС. 1 показывает блок-схему, иллюстрирующую цифровую схему 1 .

Ссылаясь на фиг. 1, цифровая схема 1 может генерировать выходной сигнал y 1 на основе двух входных сигналов a 1 и 2 .

Цифровая схема 1 может включать в себя схему цифрового затвора, такую как затвор И-НЕ, затвор ИЛИ-И или т.п.

Цифровая схема 1 может включать в себя множество логических вентилей, которые объединяются для генерации одного выходного сигнала y 1 на основе двух входных сигналов a 1 и 2 .

Здесь и далее предполагается, что цифровая схема 1 является логическим элементом И-НЕ.

РИС. 2 показывает блок-схему, иллюстрирующую устройство моделирования согласно варианту осуществления настоящего раскрытия.

Устройство моделирования выполняет моделирование с использованием схемного модуля, который моделирует цифровую схему 1 на фиг.1.

В этом варианте осуществления схемный модуль включает в себя схему модели 10 и справочную таблицу (LUT) 20 .

В этом варианте осуществления устройство моделирования дополнительно включает в себя схему управления 30 для управления схемой модели 10 и LUT 20 для выполнения операции моделирования.

Схема управления 30, может подавать один или несколько сигналов управления или один или несколько параметров работы в схему модели 10 , обращаясь к LUT 20 в соответствии с изменением входного сигнала, например.g., 1 и / или 2 , введенные в схемный модуль во время операции моделирования.

LUT 20 хранит множество сигналов управления и рабочих параметров для управления работой модельной схемы 10 , которые определены как соответствующие комбинациям входных сигналов a 1 и 2 и выходной сигнал y 1 .

Схема модели 10 включает в себя множество схем инвертора задержки , 100, и 200, , каждая из которых задерживает соответствующий входной сигнал, 1, или 2 , и схему переключения 300 , соединяющую один из инверторов задержки. схемы 100 и 200 с выходным узлом N 1 , где выдается выходной сигнал y 1 .

Схема модели 10 может дополнительно включать в себя конденсатор 400 , подключенный к выходному узлу N 1 .

Емкость C конденсатора 400 может храниться в LUT 20 .

Первая схема инвертора задержки 100 включает в себя первую схему переменной задержки 110 для задержки первого входного сигнала a 1 в соответствии с первым сигналом управления задержкой D 1 и первую схему инвертора 120 для инвертируют выход первой схемы переменной задержки , 110, .

Вторая схема инвертора задержки 200 включает в себя вторую схему переменной задержки 210 для задержки второго входного сигнала a 2 в соответствии со вторым сигналом управления задержкой D 2 и вторую схему инвертора 220 для инвертируют выход второй схемы переменной задержки 210 .

Величина задержки первой схемы переменной задержки 110 устанавливается первым сигналом управления задержкой D 1 , поступающим из LUT 20 , а величина задержки второй схемы переменной задержки 210 устанавливается посредством второй сигнал управления задержкой D 2 предоставляется из LUT 20 .

В это время первый и второй сигналы управления задержкой D 1 и D 2 могут иметь значения для прямого обозначения величин задержки первой и второй схем переменной задержки , 110, и , 210, , соответственно.

В другом варианте осуществления первая схема с регулируемой задержкой , 110, имеет конфигурацию, показанную на фиг. 3, а вторая схема с регулируемой задержкой , 210, имеет конфигурацию, показанную на фиг. 4.

В это время первая и вторая схемы переменной задержки , 110, и , 210, имеют по существу одинаковую конфигурацию.

Ссылаясь на фиг. 3, первая схема с регулируемой задержкой , 110, включает в себя множество схем задержки , 111, и , 112, для задержки первого входного сигнала, , 1, , в соответствии с различными величинами задержки, и схему выбора , 113, , для выбора одного из выходов. из множества схем задержки 111 и 112 .

Хотя две схемы задержки 111 и 112 показаны на фиг. 3 , количество схем задержки, включенных в первую схему переменной задержки , 110, , может быть установлено по-разному согласно вариантам осуществления.

Сигнал выбора SEL 1 , подаваемый на схему выбора 113 , сохраняется в LUT 20 . Это будет подробно описано ниже.

В настоящем варианте осуществления первая схема инвертора , 120, , включенная в первую схему инвертора задержки , 100, , включает в себя PMOS-транзистор P 1 и NMOS-транзистор N 1 , затворы которых соединены совместно с входным узлом и чьи стоки соединены вместе с выходным узлом.Входной узел первой схемы инвертора , 120, соединен с первой схемой переменной задержки , 110, , а выходной узел первой инверторной схемы , 120, соединен со схемой переключения , 300, .

В этом варианте LUT 20 хранит рабочие параметры PMOS-транзистора P 1 и NMOS-транзистора N 1 .

Рабочие параметры, предоставленные первой схеме инвертора , 120, , устанавливают время перехода нарастания или спада выходного сигнала y 1 .

Параметры работы PMOS-транзистора P 1 включают крутизну GMP 1 и пороговое напряжение THP 1 , а параметры работы NMOS-транзистора N 1 включают крутизну GMN 1 и пороговое напряжение. ТНН 1 .

Ссылаясь на ФИГ. 4, вторая схема с регулируемой задержкой , 210, включает в себя множество схем задержки , 211, и , 212, для задержки второго входного сигнала a, 2, , на различные величины задержки и схему выбора , 213, для выбора одного из выходов множество схем задержки 211 и 212 .

Хотя две схемы задержки 211 и 212 показаны на фиг. 4, количество схем задержки, включенных во вторую схему , 210, переменной задержки, может варьироваться согласно вариантам осуществления.

Сигнал выбора SEL 2 , подаваемый на схему выбора 213 , сохраняется в LUT 20 . Это будет подробно описано ниже.

В настоящем варианте осуществления вторая схема инвертора , 220, , включенная во вторую схему инвертора задержки 200 , включает в себя PMOS-транзистор P 2 и NMOS-транзистор N 2 , затворы которых соединены совместно с входным узлом и чьи стоки соединены вместе с выходным узлом.Входной узел второй схемы инвертора , 220, соединен со второй схемой переменной задержки , 210, , а выходной узел второй инверторной схемы , 220, соединен со схемой переключения , 300, .

Рабочие параметры, предоставленные второй схеме инвертора 220 , задают время перехода нарастания или спада выходного сигнала y 1 .

В этом варианте LUT 20 хранит рабочие параметры PMOS-транзистора P 2 и NMOS-транзистора N 2 .

Рабочие параметры PMOS-транзистора P 2 включают крутизну GMP 2 и пороговое напряжение THP 2 , а рабочие параметры NMOS-транзистора N 2 включают крутизну GMN 2 и пороговое напряжение. ТНН 2 .

Количество схем инвертора задержки, включенных в схему модели 10 , соответствует количеству входных сигналов.

Например, если имеется N (N — натуральное число) входных сигналов, N схем инвертора задержки могут быть включены в схему модели 10 .

Схема переключения 300 включает в себя первый переключатель 310 для обеспечения вывода первой схемы инвертора задержки 100 на выходной узел N 1 в ответ на первый сигнал переключения SW 1 и второй переключатель 320 для обеспечения вывода второй схемы инвертора задержки 200 на выходной узел N 1 в ответ на второй сигнал переключения SW 2 .

Число переключателей, включенных в схему переключения 300 , соответствует количеству схем инвертора задержки, включенных в схему модели 10 .

Например, если есть N схем инвертора задержки в модельной схеме 10 , N переключателей могут быть включены в схему переключения 300 .

В этом случае каждый из переключателей обеспечивает вывод соответствующей схемы инвертора задержки на выходной узел N 1 в ответ на соответствующий сигнал переключателя.

Когда имеется одна схема инвертора задержки, переключающая схема , 300, может включать в себя один переключатель, и, таким образом, выход схемы инвертора задержки может быть напрямую подключен к выходному узлу N 1 через один переключатель.

Значение выходного узла N 1 соответствует выходному сигналу y 1 .

РИС. 5-8 показаны таблицы, иллюстрирующие LUT 20 на фиг. 2 согласно варианту осуществления настоящего раскрытия.

Здесь и далее раскрывается способ генерации LUT 20 , предполагая, что цифровая схема 1 является логическим элементом И-НЕ.

РИС. 5 показывает таблицу для установки переменных состояния, соответствующих комбинациям входных сигналов a 1 и 2 .

В дальнейшем таблица, показанная на фиг. 5 может называться первой таблицей 21.

В настоящем варианте осуществления состояние 1 соответствует случаю, когда входные сигналы a 1 и 2 равны (0, 0), состояние 2 соответствует случаю где входные сигналы a 1 и 2 равны (0, 1), состояние 3 соответствует случаю, когда входные сигналы a 1 и 2 равны (1, 0), а состояние 4 соответствует в случае, когда входные сигналы 1 и 2 равны (1, 1).

Таким образом, каждое из состояний в первой таблице 21 соответствует соответствующей комбинации входных сигналов a 1 и 2 .

РИС. 6 показывает таблицу для установки индексной переменной, соответствующей изменению состояния, вызывающего изменение выходного сигнала y 1 .

В дальнейшем таблица, показанная на фиг. 6 может называться второй таблицей 22.

На фиг. 5 случай, когда выходной сигнал y 1 изменяется с 1 на 0, соответствует случаю, когда текущее состояние является одним из 1, 2 и 3, а следующее состояние равно 4, и случаю, когда выходной сигнал y 1 изменяется с 0 на 1, что соответствует случаю, когда текущее состояние равно 4, а следующее состояние — одно из 1, 2 и 3.

Во второй таблице 22 на фиг. 6 значение индекса дается для каждой из шести комбинаций текущего состояния и следующего состояния.

В настоящем варианте осуществления индекс 1 соответствует случаю, когда текущее состояние равно 1, а следующее состояние — 4, индекс 2 соответствует случаю, когда текущее состояние равно 2, а следующее состояние — 4, индекс 3 соответствует случай, когда текущее состояние — 3, а следующее состояние — 4, индекс 4 соответствует случаю, когда текущее состояние — 4, а следующее состояние — 1, индекс 5 соответствует случаю, когда текущее состояние — 4, а следующее состояние — 2, а индекс 6 соответствует случаю, когда текущее состояние — 4, а следующее состояние — 3.

ФИГ. 7 и 8 показаны таблицы для хранения сигналов управления и рабочих параметров, подаваемых в модельную схему 10 на фиг. 2 для каждого индекса на фиг. 6.

В дальнейшем в таблицах, показанных на фиг. 7 и 8 могут называться третьими таблицами 23 и 23-1 соответственно.

Каждый индекс на фиг. 6 соответствует случаю, когда выходной сигнал y 1 переходит, как показано на фиг. 5.

Каждый индекс на фиг. 6 соответствует случаю, когда выходной сигнал y 1 переходит, как показано на фиг.5.

Третья таблица 23-1 на фиг. 8 хранит сигналы выбора SEL 1 и SEL 2 , первый и второй сигналы переключения SW 1 и SW 2 , а также рабочие параметры GMP 1 , THP 1 , GMP 2 , THP 2 и C должны быть предоставлены в схему модели 10 в то время, когда выходной сигнал y 1 переходит. Третья таблица 23-1 на фиг. 8 может дополнительно сохранять рабочие параметры GMN 1 , THN 1 , GMN 2 и THN 2 .

В дальнейшем будет описана работа схемы управления , 30, , когда входной сигнал изменяется.

Схема управления 30 определяет, что случай, когда входные сигналы 1 и 2 изменяются с (0, 0) на (1, 1), соответствует случаю, когда переменная состояния изменяется с 1 на 4, и соответствует индексу 1 при обращении к первой и второй таблицам 21 и 22, соответственно, показанным на фиг. 5 и 6.

Когда схема управления 30 определяет, что изменение входных сигналов a 1 и 2 соответствует индексу 1, схема управления 30 выдает сигналы управления задержкой или сигналы выбора. , сигналы переключения и рабочие параметры, соответствующие индексу 1 в схеме модели 10, со ссылкой на третью таблицу 23 или 23-1.

Когда переменная состояния изменяется с 1 на 4, выходной сигнал y 1 изменяется с 1 на 0, что соответствует инвертированию входного сигнала a 1 . Входной сигнал a 1 изменяется с 0 на 1.

Соответственно, первый и второй сигналы переключения SW 1 и SW 2 , соответствующие индексу 1 в третьей таблице 23 или 23-1, устанавливаются так, что первый переключатель 310 включен, а второй переключатель 320 выключен.

В этом варианте осуществления LUT 20 может включать в себя первую таблицу 21, вторую таблицу 22 и третью таблицу 23 или 23-1, описанные выше.

Структура каждой таблицы, включенной в LUT 20 , может варьироваться в соответствии с вариантами осуществления.

РИС. 9 показывает блок-схему, иллюстрирующую способ создания схемного модуля согласно варианту осуществления настоящего раскрытия.

Сначала выполняется предварительное моделирование на этапе S 100 .

В процессе предварительного моделирования выполняется имитация специй для цифровой схемы 1 с использованием модели специй, соответствующей реальному производственному процессу.

В это время логические значения выходного сигнала y 1 для всех комбинаций входных сигналов a 1 и 2 , величина задержки и время перехода выходного сигнала y 1 на основе при изменении входных сигналов a 1 и 2 могут быть получены из результата процесса предварительного моделирования.

Затем LUT 20 генерируется на S 200 .

Например, первая таблица 21, показанная на фиг.5 создается путем присвоения значения состояния каждой комбинации входных сигналов a 1 и 2 , а вторая таблица 22, показанная на фиг. 6 генерируется путем присвоения значения индекса каждой комбинации изменений состояния.

Тогда третья таблица 23 или 23-1, соответственно, показанная на фиг. 7 или 8 генерируется так, чтобы можно было выделить управляющие сигналы и рабочие параметры, соответствующие каждому индексу.