НОУ ИНТУИТ | Лекция | Последовательностные функциональные узлы. Триггеры

Аннотация: Рассматривается принцип действия триггеров как простейших элементов электронной памяти.

Цифровое устройство называется последовательностным [1, с.91], если его выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. Поэтому говорят, что такие функциональные узлы «обладают памятью».

Триггер — это логическая схема с положительной обратной связью, которая может находиться только в одном из двух устойчивых состояний, принимаемых за состояние логического нуля и логической единицы.

В отличие от всех рассмотренных ранее комбинационных схем, работа которых определяется только входными сигналами, состояние триггера в текущий момент зависит и от его состояния в предыдущий момент времени. Иными словами, триггер — это схема с запоминанием [2].

Иными словами, триггер — это схема с запоминанием [2].

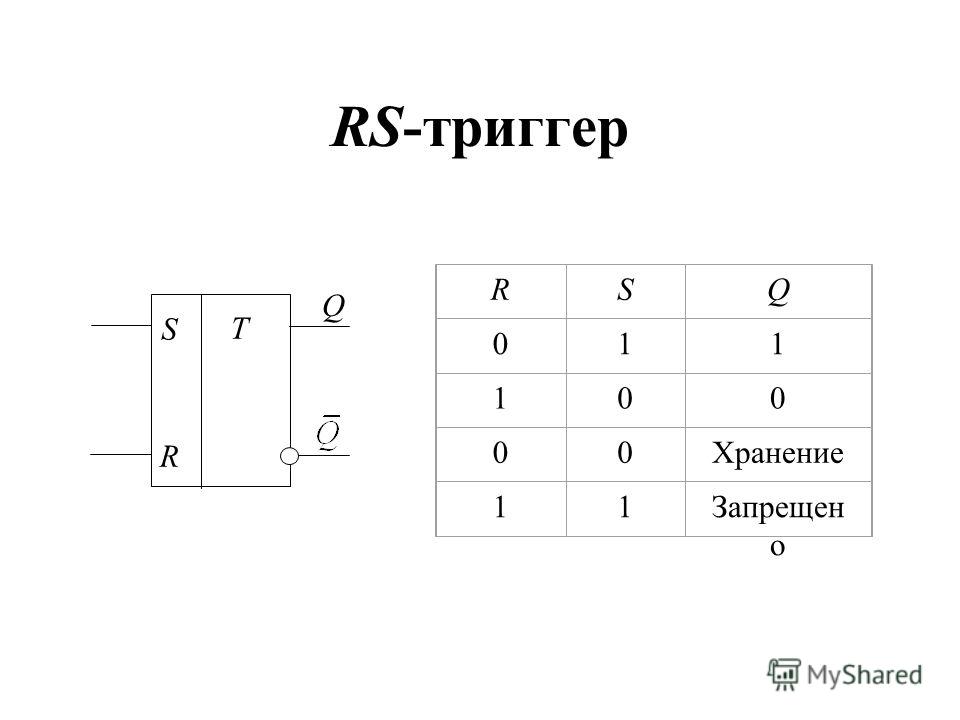

RS-триггеры

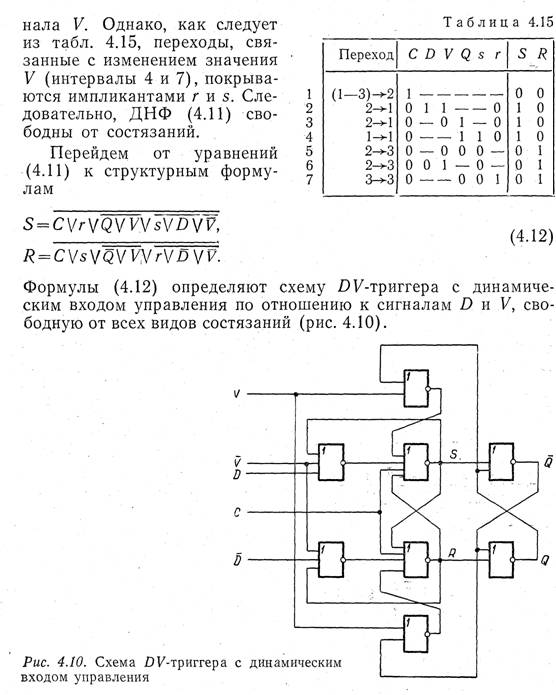

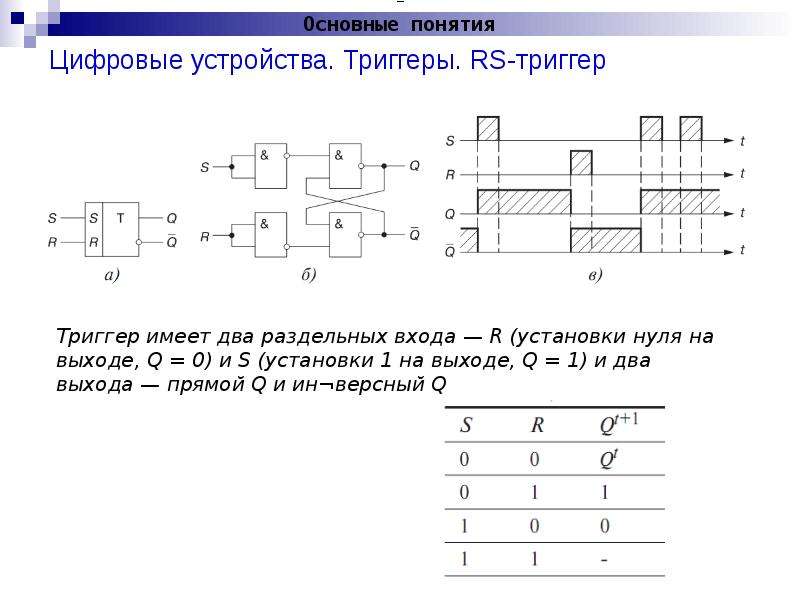

Простейшая функциональная схема RS — триггера в базисе ИЛИ-НЕ приведена на рис. 7.1,а. Здесь (от англ. Reset — сброс) — вход сброса триггера в состояние логического нуля, S (от англ. Set — устанавливать) — вход установки триггера в логическую единицу, — прямой выход триггера (состояние считается для триггера единичным, а противоположное, при , — нулевым), — инверсный выход триггера.

Рис. 7.1. RS-триггер в базисе ИЛИ-НЕ: а — функциональная схема; б — УГО

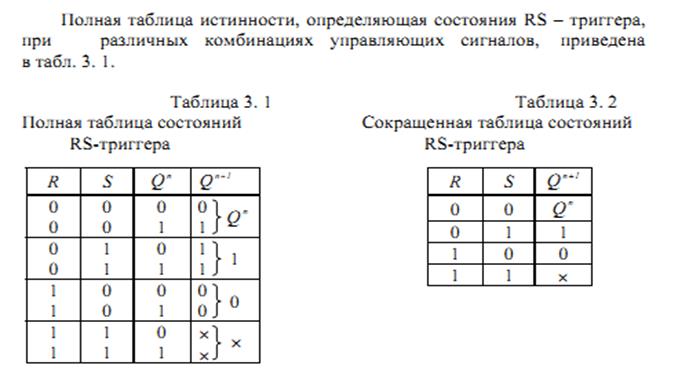

Очевидно, при наличии двух входных сигналов, возможны 4 варианта работы схемы (табл. 7.1). Начнем анализ с состояний, когда на один из входов подается решающий для элемента ИЛИ-НЕ сигнал логической 1.

Первая такая комбинация: , .

Вторая комбинация: , . Решающий для ИЛИ-НЕ сигнал переключит выход в нулевое состояние, а сочетание и обеспечит переключение инверсного выхода в состояние . Триггер сброшен — то есть пришел в устойчивое нулевое состояние.

Если на оба входа подать , то состояние

Если же триггер был сброшен, то есть было и , тогда решающий сигнал бу дет через положительную обратную связь подан на верхний элемент ИЛИ-НЕ и состояние будет подтверждено. На входы нижнего элемента ИЛИ-НЕ будет подано сочетание сигналов и . Таким образом,

Если же триггер был сброшен, то есть было и , тогда решающий сигнал бу дет через положительную обратную связь подан на верхний элемент ИЛИ-НЕ и состояние будет подтверждено. На входы нижнего элемента ИЛИ-НЕ будет подано сочетание сигналов и . Таким образом, Рассмотрим последнюю, четвертую комбинацию входных сигналов: , . На входы обоих логических элементов ИЛИ-НЕ поданы решающие сигналы логической единицы, поэтому на выходах обоих элементов будут логические нули, то есть и . Если теперь одновременно подать , то за счет положительных обратных связей на оба логических элемента будут поданы 0, поэтому на выходах ИЛИ-НЕ установятся две решающие логические единицы, которые будут стремиться перевести выход другого ИЛИ-НЕ в логический 0. Кто победит в этом «поединке», зависит от того, в каком из элементов ИЛИ-НЕ переходный процесс закончится раньше. Допустим, в верхнем элементе процесс завершится раньше, тогда подается на вход нижнего элемента ИЛИ-НЕ и приводит к переключению .

Для рассматриваемой схемы характерно также и то, что оба элемента триггера переключаются не одновременно, а последовательно друг за другом. Поэтому в ходе переходного процесса переключения триггера в противоположное состояние будут моменты времени, когда и на прямом, и на инверсном выходах будут одинаковые уровни. Это недопустимо по определению, поскольку триггер должен быть либо в устойчивом состоянии логического ( и ), либо в

Поскольку решающим для элементов ИЛИ-НЕ является сигнал логической единицы, в УГО входные управляющие сигналы и являются прямыми.

Поскольку решающим для элементов ИЛИ-НЕ является сигнал логической единицы, в УГО входные управляющие сигналы и являются прямыми.Функциональная схема простейшего триггера в базисе И-НЕ показана на рис. 7.2.а. Поскольку для функции И-НЕ решающим является сигнал логического нуля, активный уровень входных сигналов будет нулевым (табл. 7.2), что отражается на УГО триггера (рис. 7.2,б) в виде инверсного изображения входов и .

Рис. 7.2. RS-триггер в базисе И-НЕ: а — функциональная схема; б — УГО

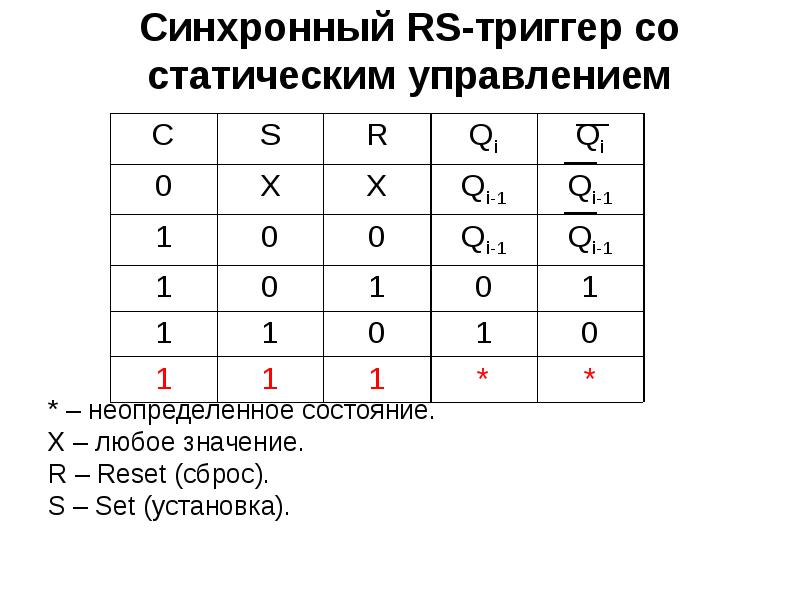

Синхронный RS-триггер

4.2 в

«Функциональные узлы комбинаторной логики. Дешифраторы»

). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал (рис. 7.3,а). При неактивном уровне на выходах первого и второго логических элементов И-НЕ будет логическая . Она не является решающей для функции И-НЕ, поэтому триггер на третьем и четвертом элементах будет хранить записанную ранее информацию. Таким образом, триггер не реагирует на изменения входных сигналов при . Если же синхросигнал становится активным ( ), то схема пропускает все переключения входных сигналов и (табл. 7.3). Поскольку входные ключи производят инверсию входных сигналов и , активным их уровнем будет логическая (рис. 7.3,б).

4.2 в

«Функциональные узлы комбинаторной логики. Дешифраторы»

). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал (рис. 7.3,а). При неактивном уровне на выходах первого и второго логических элементов И-НЕ будет логическая . Она не является решающей для функции И-НЕ, поэтому триггер на третьем и четвертом элементах будет хранить записанную ранее информацию. Таким образом, триггер не реагирует на изменения входных сигналов при . Если же синхросигнал становится активным ( ), то схема пропускает все переключения входных сигналов и (табл. 7.3). Поскольку входные ключи производят инверсию входных сигналов и , активным их уровнем будет логическая (рис. 7.3,б).Рис. 7.3. Синхронный RS-триггер: а — функциональная схема; б — УГО

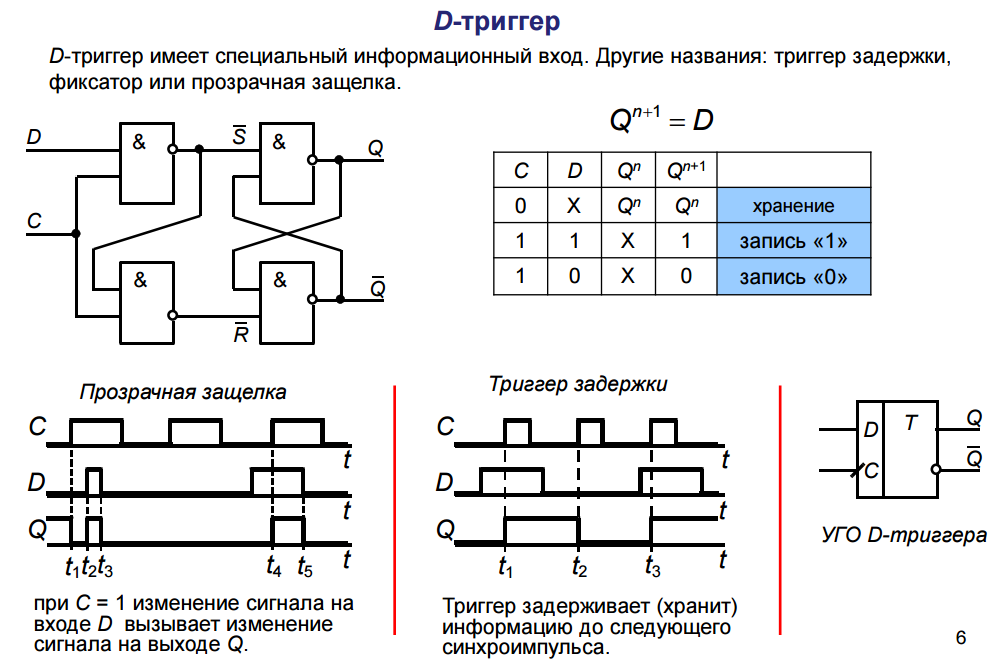

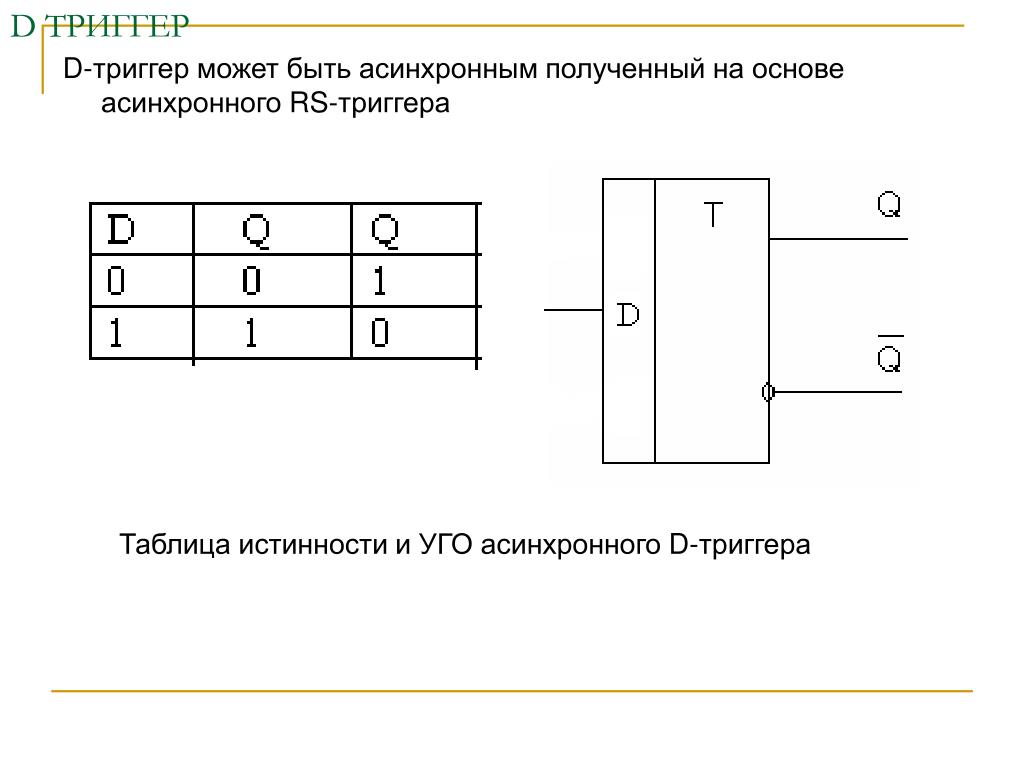

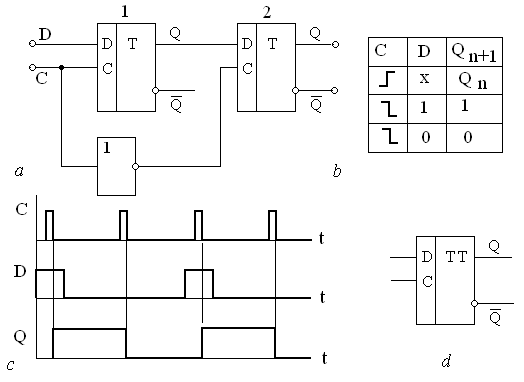

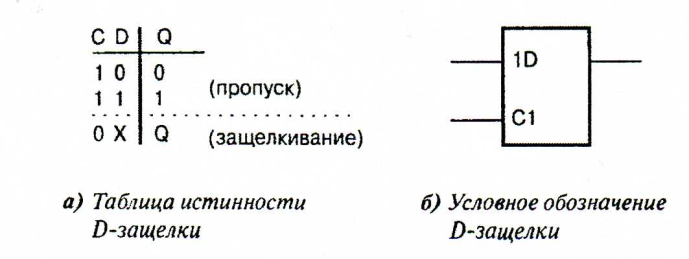

D-триггер: принцип действия, таблица истинности

Триггер – элементарное устройство, представляющее собой цифровой автомат с двумя состояниями устойчивости, одному из которых присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды устройств: T-триггер, D-триггер, JK-триггер, RS-триггеры. Естественно, здесь перечислены наиболее распространенные варианты, но кроме них существуют автоматические устройства и других типов.

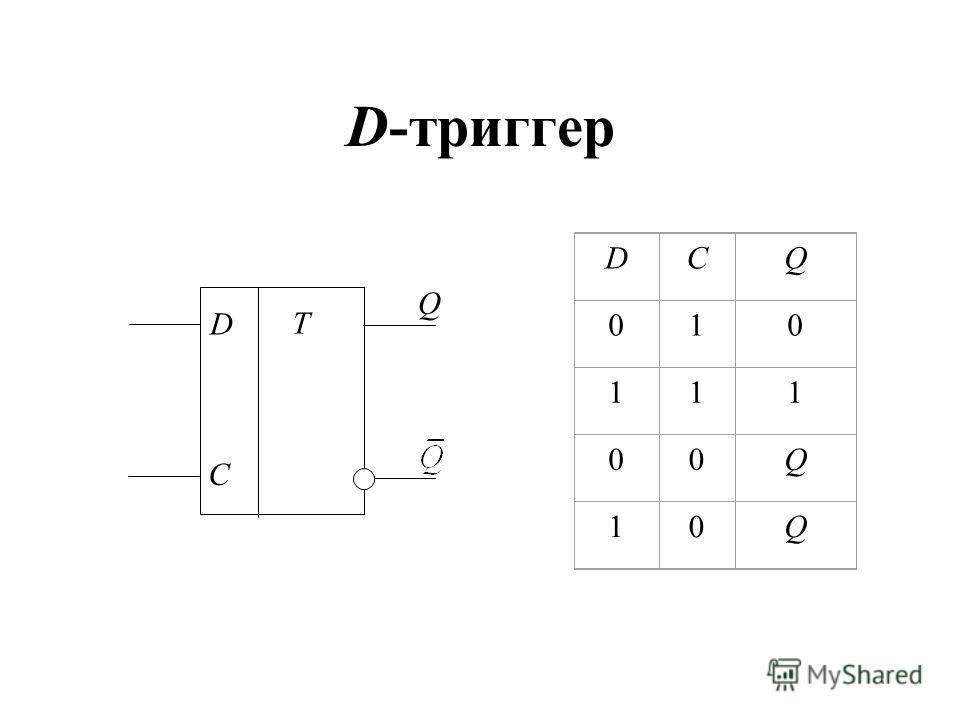

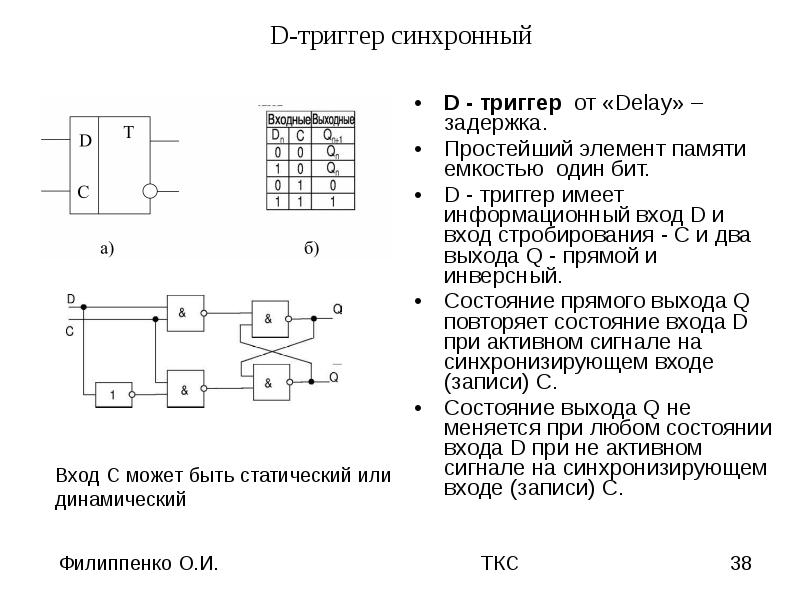

В этой статье мы более подробно рассмотрим D-триггер. Упомянутый автомат имеет один-единственный информационный (D) вход, таким образом, он предназначен для реализации функции временной задержки.

Принцип работы

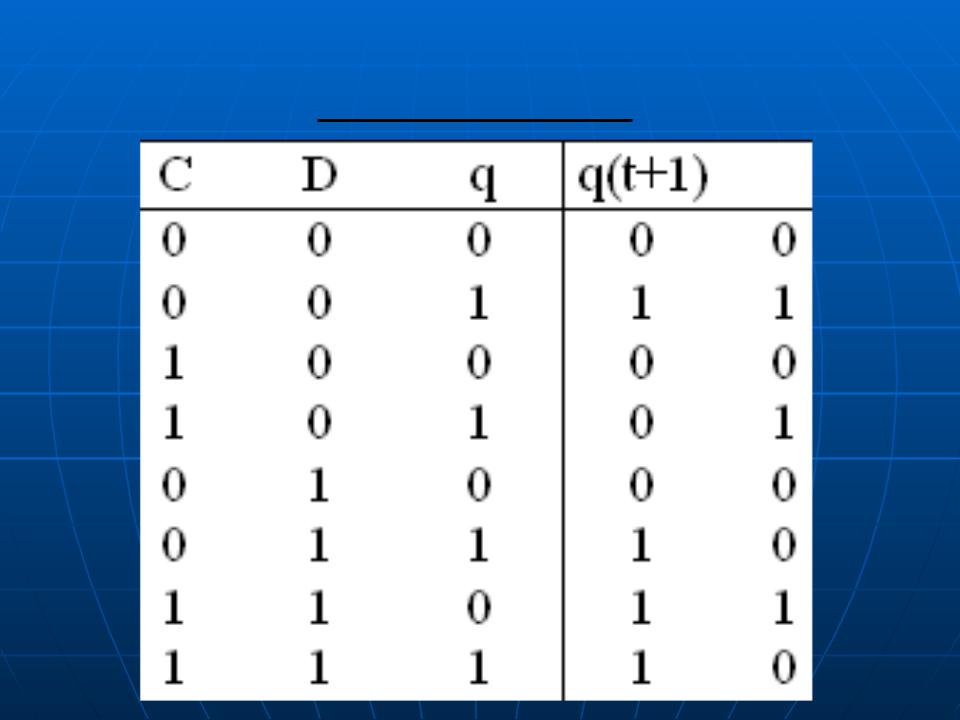

Характеристическое уравнение Q(t+1)=Dt описывает функционирование такого типа устройства, как D-триггер. Таблица истинности (таблица переходов) для данного цифрового автомата приведена ниже.

Как видим, в первой и четвертой строке значения сигналов Q в моменты времени t и t+1 совпадают. То есть D-триггер является элементом задержки сигнала. В результате рассматриваемые приборы асинхронного типа не нашли своего применения, так как на выходе будет повторяться входной сигнал с небольшой временной задержкой.

То есть D-триггер является элементом задержки сигнала. В результате рассматриваемые приборы асинхронного типа не нашли своего применения, так как на выходе будет повторяться входной сигнал с небольшой временной задержкой.

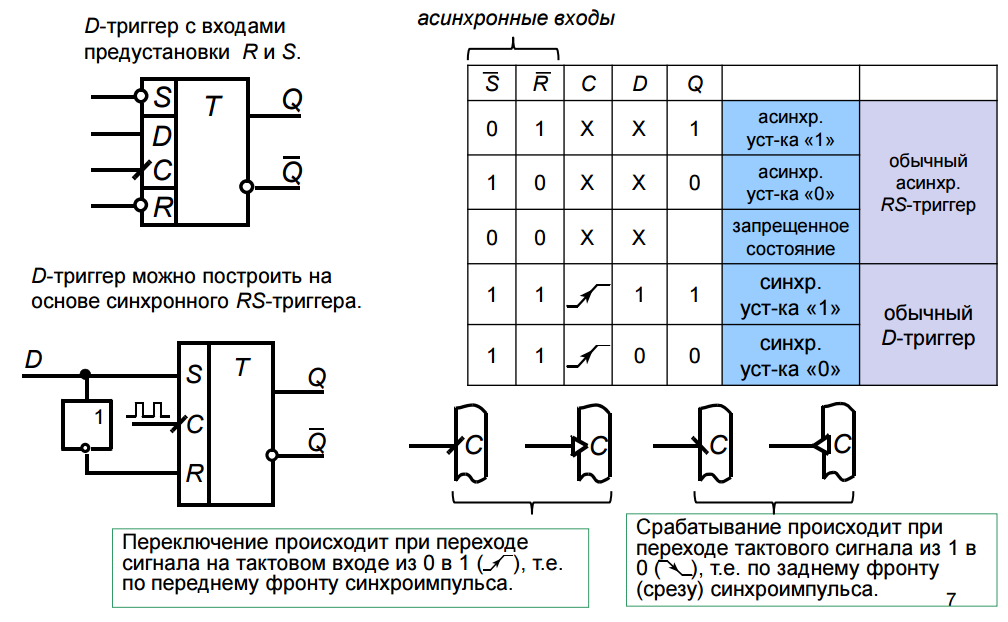

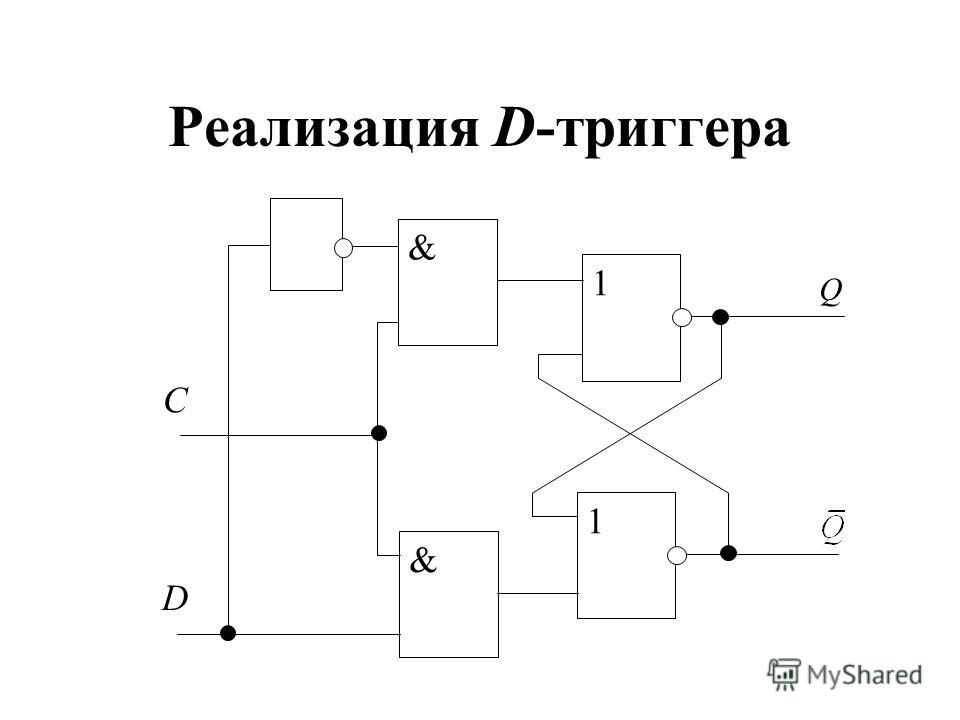

D-триггер синхронного типа строится из одноуровневых (одноступенчатых) и двухуровневых (двухступенчатых) RS-устройств такого же типа. Упомянутые автоматы функционируют согласно таблице переходов.

Одноступенчатый D-триггер может быть выполнен из одноуровневого синхронного RS-устройства и одного элемента И-НЕ1, который соединяет в единый информационный (D) вход оба инверсных входа D-триггера.

При поступлении логического нуля на синхронизирующий вход автомат типа RS заблокирован уровнем логической единицы с выходов элементов И-НЕ2 и И-НЕ3. При смене сигнала синхронизации уровень, поданный на информационный вход, создаст логический нуль либо на входе S (при D=1), либо на входе R (при D=0) асинхронного триггера Т. Он переключится в состояние, соответствующее логическому уровню D. Одноступенчатый триггер D-типа задерживает распространение входного на время паузы между синхронизирующими сигналами.

Одноступенчатый триггер D-типа задерживает распространение входного на время паузы между синхронизирующими сигналами.

D-триггер с динамическим управлением. Описание работы, функциональная схема

Автоматическое устройство такого вида конструируется из трех RS-триггеров асинхронного типа. Они построены на элементах И-НЕ, при этом два из них выполняют коммутирующую функцию, а третий является выходным. Выходные сигналы коммутирующих триггеров предназначены для управления выходным триггером.

При уровне сигнала С, равного логическому нулю, на входы выходного триггера поступает нейтральная для него комбинация сигналов, и он переключается в режим хранения. При изменении информационного сигнала коммутирующие триггеры переходят в режим ожидания, и как только поступает сигнал логической единице на разрешающий вход триггера С, выходной автомат устанавливается в новое состояние, которое соответствует информационному сигналу на D-входе в предыдущем такте.

В случае если изменение уровня информационного сигнала пройдет в период установки выходного триггера, тогда коммутирующие устройства сигнал не пропустят. Получается, что цель коммутирующих триггеров заключается в приеме информационных сигналов, передаче их на вход выходного прибора в момент перемены сигнала на управляющем входе С от логического нуля к логической единице и самоблокировки от воздействия сигнала на информационном входе.

Получается, что цель коммутирующих триггеров заключается в приеме информационных сигналов, передаче их на вход выходного прибора в момент перемены сигнала на управляющем входе С от логического нуля к логической единице и самоблокировки от воздействия сигнала на информационном входе.

Logisim 1.0 D/J-K триггеры

Поведение

Эти компоненты существуют только для обратной совместимости с Logisim 1.0X; для новых схем вместо них рекомендуются триггеры из библиотеки Память.

Каждый триггер хранит один бит данных, который выдаётся на выход Q на восточном крае. В нормальном состоянии значением можно управлять через входы на западном крае. В частности, значение меняется, когда значение на

| D триггер | J-K триггер |

|---|---|

- D триггер: когда значение на тактовом входе возрастает с 0 до 1, значение, хранящееся в триггере, становится значением входа D (Данные) в тот момент.

Контакты

- Западный край, отмечен треугольником (вход, разрядность равна 1)

- Тактовый вход: в момент, когда значение на этом входе меняется с 0 на 1 (передний фронт), значение триггера будет обновлено в соответствии с другими входами на западном крае. Пока значение на этом входе остаётся 0 или 1, другие входы на западном крае не имеют эффекта.

- Западный край, другой отмеченный контакт(ы) (вход(ы), разрядность равна 1)

- Эти входы управляют тем, как значение триггера меняется в момент срабатывания тактового входа. Их точное поведение зависит от триггера; приведенная выше таблица описывает его.

- Восточный край, отмечен Q, северный контакт (выход, разрядность равна 1)

- Выдаёт значение, хранящееся в данный момент в триггере.

- Восточный край, южный контакт (выход, разрядность равна 1)

- Выдаёт дополнение для значения, хранящегося в данный момент в триггере.

Атрибуты

Нет.

Поведение Инструмента Нажатие

Нет.

Поведение Инструмента Текст

Нет.

Назад к Справке по библиотеке

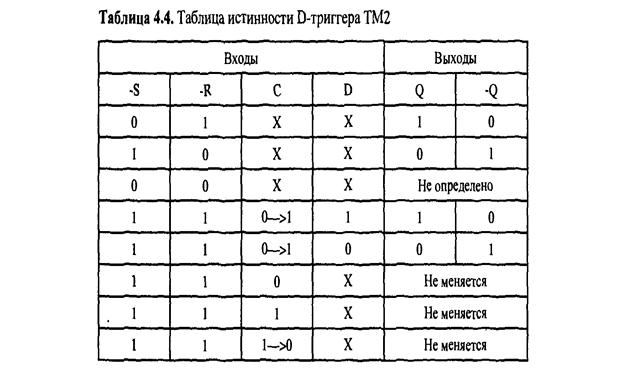

Исследование триггеров rs- и d-типов

ЦЕЛЬ РАБОТЫ: Исследовать триггеры RS-типа на элементах ИЛИ-НЕ, в интегральном исполнении на микросхеме К155ТМ2, триггера D-типа

Триггер rs типа на элементах или-не

Trigger

– (англ. ) – спусковой крючок. Устройство,

обладающее двумя состояниями устойчивого

равновесия и способное скачком переходить

из одного состояния в другое под

воздействием внешнего управляющего

сигнала.

) – спусковой крючок. Устройство,

обладающее двумя состояниями устойчивого

равновесия и способное скачком переходить

из одного состояния в другое под

воздействием внешнего управляющего

сигнала.

У словное обозначение триггера на логических элементах ИЛИ-НЕ. Выходной информационный выход триггера обозначается через Q, инверсионный – .

С хема RS триггера

Входы триггера:

S-set-установка 1, Reset-сброс 1, т.е. установка 0 на выходе Q.

При S=1 и R=0 на выходе Q устанавливается уровень логической 1, т.е. говорят, что триггер установлен в состояние 1.

При S=0, R=1 происходит очистка выхода Q, на нем устанавливается уровень логического 0.

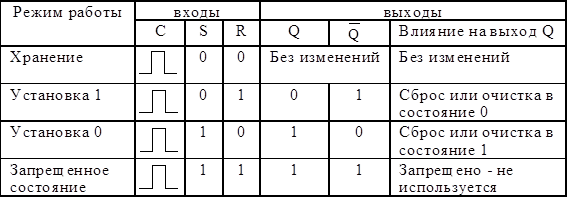

Режим работы | Входы | Выходы | Влияние на выход Q | ||

S | R | Q | |||

Запрещенное состояние | 1 | 1 | 0 | 0 | Не используется |

Установка 1 | 1 | 0 | 1 | 0 | Для установки Q в 1 |

Установка 0 | 0 | 1 | 0 | 1 | Для установки Q в 0 |

Хранение | 0 | 0 | Q | Зависит от предыдущего состояния | |

Таблица истинности для RS триггера

Временные диаграммы сигналов

Триггер rs – типа на элементах и-не

Активный

входной уровень для триггера на элементах

И-НЕ – логический 0. Для индикации

входного уровня используются инверторы

D2.4, D2.3 и светодиоды HL1 и HL2.

Для индикации

входного уровня используются инверторы

D2.4, D2.3 и светодиоды HL1 и HL2.

Схема — триггера Условное графическое обозначение

Таблица истинности -триггера

Режим работы | Входы | Выходы | Влияние на выход Q | ||

S | R | Q | |||

Запрещенное состояние | 0 | 0 | 1 | 1 | Запрещено – не использовать |

Установка 1 | 0 | 1 | 1 | 0 | Для установки Q в 1 |

Установка 0 | 1 | 0 | 0 | 1 | Для установки Q в 0 |

Хранение | 1 | 1 | Q | Зависит от предыдущего состояния | |

Временные диаграммы сигналов

Триггер rs-типа в интегральном исполнении на имс типа к155 тм2

Схема

RS-триггера

берется из справочника по интегральным

микросхемам.

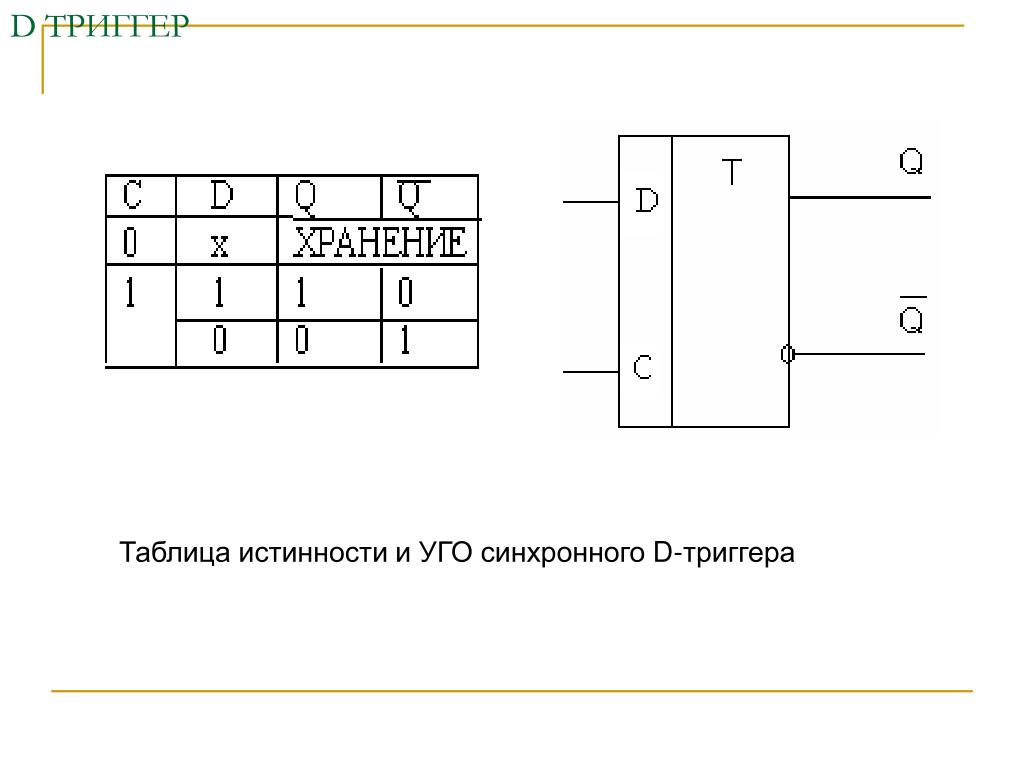

Тактируемый d-триггер

Условное обозначение D-триггера

D-триггер переходит в состояние Q =1, если в момент прихода синхронизирующего сигнала С=1 на его информационном входе сигнал D=1. В этом состоянии триггер остается и после снятия сигнала на входе D до прихода очередного синхронизирующего сигнала, возвращающего триггер в состояние Q =0.

D-триггер получил название от слова delay – задерживать.

Сигнал на выходе Q в такте n+1 повторяет сигнал, который был на входе D в предыдущем такте n.

С войства D-триггера: он запоминает и хранит на выходе Q сигнал, который находится на входе D в момент спада импульса С.

Работа

проводится на плате П2 с технологическими

картами II-1

– II-4.

На этих каратах изображены принципиальные

схемы триггеров RS-типа

на элементах ИЛИ-НЕ (II-1),

И-НЕ (II-2)

в интегральном исполнении на ИМС типа

К155ТМ2, на карте II-4

– схема D-триггера

на ИМС типа К155ТМ2.

При домашней подготовке:

Зарисовать схемы RS-триггеров, выполненных на логических элементах И-НЕ и ИЛИ-НЕ.

Добавляя необходимые логические элементы к RS-триггеру, получить и зарисовать схемы синхронного RS-триггера, D-триггера, Т-триггера.

Нарисовать временные диаграммы, иллюстрирующие работу перечисленных типов триггеров.

4. Продумать формы отчетных таблиц.

При выполнении работы:

Для каждого устройства составить таблицу изменений состояний в зависимости от входных сигналов (таблицы должны содержать все возможные комбинации входных сигналов). Проанализировать режимы работы триггеров (режим хранения, записи, запрещенный режим).

Для тактируемого D-триггера по полученной таблице составить временную диаграмму напряжений на выходе Q по известным сигналам на входах D и С.

Провести эксперимент, подтверждающий, что запись информации в D-триггер (карта II-4) происходит по фронту синхроимпульса.

Предложить схему изменений на плате П2, превращающей D-триггер в Т-триггер – (установить перемычку между У1 и Х2).

Исследовать работу Т-триггера.

При защите лабораторной работы:

Объяснить назначение и применение исследуемых схем, их работу, полученные результаты.

Объяснить назначение R-, S-, D-, С-, Т-входов триггеров. Знать, что такое активный уровень. Почему RS-триггер на элементах 2И-НЕ называют триггером с инверсными входами?

Уметь объяснить отличия синхронных и асинхронных триггеров, статических и динамических. Уметь объяснить характер «запрещенного» состояния в RS-триггере и методы его устранения в остальных типах триггеров.

Лабораторная работа № 3

ИССЛЕДОВАНИЕ ПОСЛЕДОВАТЕЛЬНОГО, ПАРАЛЛЕЛЬНОГО

И УНИВЕРСАЛЬНОГО РЕГИСТРОВ

ЦЕЛЬ РАБОТЫ: Исследовать последовательный регистр сдвига на D-триггерах, параллельный кольцевой регистр сдвига на JК-триггерах

Счетные Т и JK-триггеры — Help for engineer

Счетные Т и JK-триггеры

Т-триггеры можно построить с помощью любого двухступенчатого триггера. Наличие двух ступеней позволяет избавиться от запрещенных состояний. Ранее мы рассматривали принцип работы D-триггера, именно поэтому построение счетного триггера будем осуществлять на его базе. Он состоит из входа C (синхронизирующий) и выхода Q. Чтобы произвести синтез необходимого нам устройства, нужно инверсный выход соединить со входом:

Счетным Т-триггер называют потому, что он считает количество импульсов, которое поступает к нему на вход. Правда, подсчет ведется лишь до одного. При повторной подаче сигнала на вход – значение выхода сбрасывается. Это свойство дало возможность использовать устройство, как делитель частоты.

Правда, подсчет ведется лишь до одного. При повторной подаче сигнала на вход – значение выхода сбрасывается. Это свойство дало возможность использовать устройство, как делитель частоты.

С выхода будем снимать импульсы вдвое меньшей частоты, чем было на входе

Для построения счетного устройства мы использовали д-триггер с работой по заднему фронту. Соответственно и полученное будет работать по тому же принципу, временная диаграмма имеет следующий вид:

Собранный T-trigger на логических элементах представлен ниже. Синий провод означает нулевой уровень напряжения, красный – единица. Работает устройство при подаче импульсов с определенной частотой на вход C. Начинает происходить подсчет входящего сигнала, и по заднему фронту, выход меняет значение:

Обозначение ничем не отличается от ранее рассмотренных:

Все это мы говорили об асинхронном т-триггере (работа не контролируется никаким дополнительным сигналом). В синхронном операции начинают выполняться после подачи единицы на вход С. Небольшая модификация позволяет получить синхронный t-триггер, теперь он включится в работу только при подаче синхросигнала:

В синхронном операции начинают выполняться после подачи единицы на вход С. Небольшая модификация позволяет получить синхронный t-триггер, теперь он включится в работу только при подаче синхросигнала:

Временная диаграмма асинхронного устройства приобретает чуть иной характер, появляется прямая зависимость выхода от синхронизирующего входа:

Обозначение на схемах:

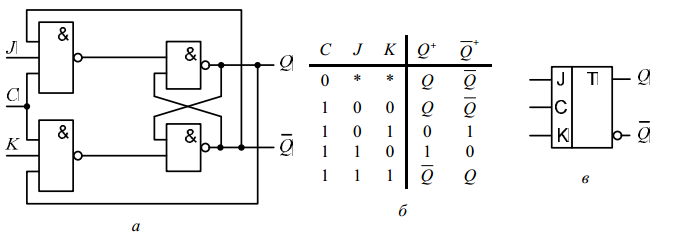

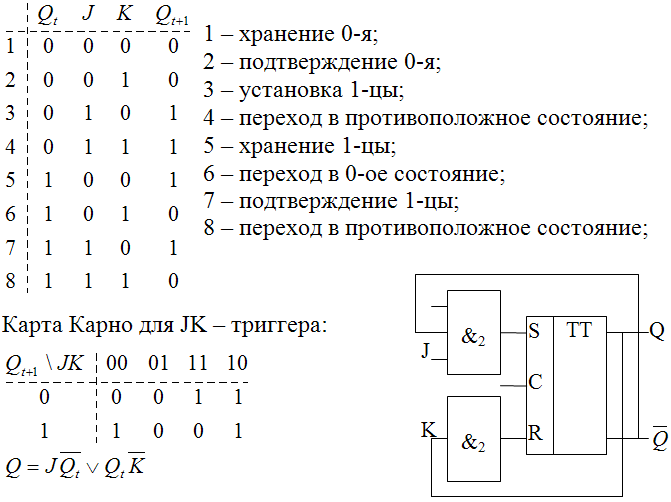

JK-trigger не совсем счетный, он считает только при определенной комбинации на входе. Работает он практически так же, как и RS. Его преимущество — не имеет запрещенной комбинации. То есть, по сути, это усовершенствованный rs-триггер. Запрещенная комбинация 1,1 убирается с помощью обратных связей. Для него таблица истинности:

Собираем на ТТЛ (логических) элементах. С помощью анимации намного проще понять, как все работает. Единица в верхнем правом углу рисунка означает первый кадр – начало отсчета. Если на входах появятся две единицы, то при отключении синхросигнала, значение на выходе Q будет меняться на противоположное (счет).

Если на входах появятся две единицы, то при отключении синхросигнала, значение на выходе Q будет меняться на противоположное (счет).

Схематическое обозначение не имеет ярко выраженных особенностей:

Недостаточно прав для комментирования

ТРИГГЕРЫ НА МИКРОСХЕМАХ

Если мультивибратор это прибор с двумя неустойчивыми состояниями, который самопроизвольно переходит из одного состояния в другое, то триггер ему полностью противоположен. Это прибор с двумя устойчивыми состояниями и эти состояния он меняет только под внешнем воздействии. Благодаря этому свойству триггеры используются в запоминающих устройствах [1]. В данной работе предлагаются к повторению широко распространенные схемы триггеров, которые можно реализовать на одной логической микросхеме К155ЛА3. Питание подается на 14 выход микросхемы, общий провод 7. Питание осуществляется от стабилизированного источника питания напряжением 5 В.

Асинхронный RS-триггер

Самый простой тип триггера, который является основой для сборки остальных триггеров в данной лабораторной работе. Он собирается на паре логических элементов И-НЕ, хотя аналогично можно использовать ИЛИ-НЕ [2]

Он собирается на паре логических элементов И-НЕ, хотя аналогично можно использовать ИЛИ-НЕ [2]

Как видно на электрической принципиальной схеме данное электронное устройство обладает симметрией. Если поменять местами входы S и R, одновременно с выходами Q и Q1, то по сути мы получим туже самую схему. Таким образом то где у триггера прямой выход, а где инверсный это по сути вопрос договора.

Для практической реализации схемы используются самодельные модули для изучения микросхем. При подаче питания триггер устанавливается в случайное состояние.

Используя данное устройство можно проследить за выполнением таблицы истинности асинхронного RS-триггер.

Таблица истинности асинхронного RS-триггера

В частности, можно увидеть, что данный триггер переключается просто от прикосновения к проводам и пронаблюдать запрещенное состояние.

Синхронный RS-триггер

Схема асинхронного RS-триггера проста, но за это приходится заплатить целым рядом недостатков: наличие запрещенного состояния, установка 0 и 1 по отдельным линиям отсутствие синхронизации, низкая помехоустойчивость. Эти недостатки частично устраняются в синхронном RS-триггере, который представляет собой асинхронный RS-триггер к которому добавлена схема синхронизации.

Эти недостатки частично устраняются в синхронном RS-триггере, который представляет собой асинхронный RS-триггер к которому добавлена схема синхронизации.

В целом работа данного триггера аналогична, с той поправкой, что при наличии на входе синхронизации низкого логического уровня триггер хранит предыдущее состояние, не реагируя на сигналы по входным линиям, т.е. в этот момент он как минимум гораздо более помехоустойчив.

Синхронный статический D-триггер

В основе данного устройства также лежит асинхронный RS-триггер, к которому присоединена схема синхронизации.

Статический D-триггер имеет один информационный вход и один вход синхронизации. Таким образом, устраняется недостаток RS-триггер – установка 0 и 1 по отдельным линиям. При наличии низкого логического уровня на входе синхронизации данное устройство хранит информацию. При подаче на вход синхронизации высокого логического уровня возможна запись информации в устройство.

Таблица истинности синхронного статического D-триггера [2]

Литература

- Отряшенков Ю.

М. Юный кибернетик – М.: Детская литература, 1978

М. Юный кибернетик – М.: Детская литература, 1978 - Ямпольский В.С. Основы автоматики и электронно-вычислительной техники – М. Просвещение, 1991

Специально для сайта Радиосхемы — Denev

Форум

Форум по обсуждению материала ТРИГГЕРЫ НА МИКРОСХЕМАХ

Последовательностные системы — триггеры

Последовательностные системы — триггеры| Справочное руководство по Electronics Workbench |

3.3.1 Последовательностные системы — триггеры

Раздел: Цифровая схемотехника

Теоретическое введение:

Триггер — цифровой автомат,

имеющий два устойчивых состояния равновесия либо 0, либо 1. Состояние триггера

распознается по его входному сигналу. Под влиянием входного сигнала триггер

скачкообразно переходит из одного устойчивого состояния в другое, при этом

скачкообразно изменяется уровень напряжения его выходного сигнала. на его инверсном

выходе).

на его инверсном

выходе).

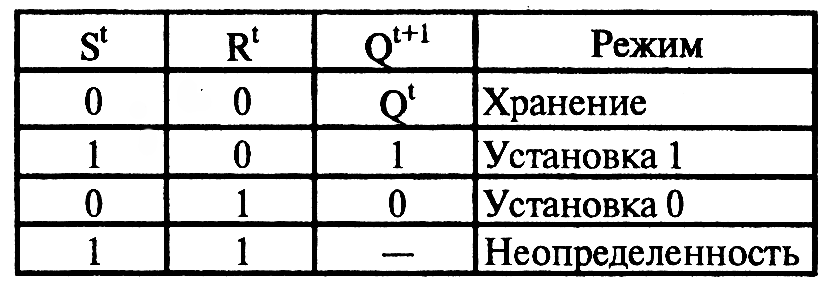

Законы функционирования триггеров задаются таблицами переходов с компактной записью, при которой в столбце состояний может быть указано, что новое состояние совпадает с предыдущим либо является его отрицанием

Типы триггеров.

Триггер типа RS имеет два входа раздельной установки в нулевое и единичное состояния. Воздействие по входу S (обозначен по первой букве слова set – установка) приводит триггер в единичное состояние, а воздействие по входу R (от первой буквы слова reset – сброс) – в нулевое. Одновременная подача сигналов S и R не допускается, что является недостатком для RS-триггера.

Асинхронный RS-триггер на

элементах И-НЕ показан на рисунке 3.3.1.1. Триггер

образован из двух комбинационных схем И-НЕ, соединенных таким образом, что

возникают положительные обратные связи, благодаря которым в устойчивом состоянии

выходной транзистор одной схемы ИЛИ-НЕ закрыт, а другой открыт. Таблица 3.1.1.1 определяет закон функционирования триггера. На рисунке 3.3.1.2 приведена временная диаграмма иллюстрирующая

работу асинхронного RS-триггера.

Таблица 3.1.1.1 определяет закон функционирования триггера. На рисунке 3.3.1.2 приведена временная диаграмма иллюстрирующая

работу асинхронного RS-триггера.

Рисунок 3.3.1.1 — Схема асинхронного RS-триггера на элементах И-НЕ

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

0 |

1 |

1 |

Установка 1 |

|

1 |

0 |

0 |

Установка 0 |

|

1 |

1 |

— |

Запрещено |

Таблица 3. 3.1.1 — Таблица переходов асинхронного

RS-триггера на элементах ИЛИ-НЕ

3.1.1 — Таблица переходов асинхронного

RS-триггера на элементах ИЛИ-НЕ

Рисунок 3.3.1.2 — Диаграмма работы асинхронного RS-триггера

При R=1 и S=0 триггер устанавливается в нулевое состояние Q=0; при R=0 и S=1 он устанавливается в единичное состояние Q=1; при R=S=0 триггер сохраняет состояние, в котором он находился до момента поступления на его входы нулевых сигналов. При R=S=1 на прямом и инверсном выходах устанавливается нулевой сигнал. Триггероное кольцо превращается в два независимых инвертора, и при переходе к хранению (R=S=0) триггер может устанавливаться в любое состояние. Поэтому такая комбинация входных сигналов запрещена.

Синхронизируемый однотактный

RS-триггер приведен на рисунке 3.3.1.3. Такие RS-триггеры имеют два

информационных входа R и S и вход синхронизации C. Кроме того, триггер может

иметь несинхронизируемые входы R и S. В этом случае функционирование триггера

осуществляется либо под воздействием несинхронизируемых входов при С=0, либо под

воздействием синхронизируемых входов. В последнем случае на несинхронизируемых

входах должны присутствовать сигналы, которые не влияют на состояние схемы.

На рисунке 3.3.1.4 приведена временная диаграмма

иллюстрирующая работу синхронного однотактного RS-триггера.

В этом случае функционирование триггера

осуществляется либо под воздействием несинхронизируемых входов при С=0, либо под

воздействием синхронизируемых входов. В последнем случае на несинхронизируемых

входах должны присутствовать сигналы, которые не влияют на состояние схемы.

На рисунке 3.3.1.4 приведена временная диаграмма

иллюстрирующая работу синхронного однотактного RS-триггера.

Рисунок 3.3.1.3 — Схема синхронного RS-триггера

Рисунок 3.3.1.4 — Диаграмма работы синхронного RS-триггера

Таблица 3.3.1.2 определяет переходы RS-триггера для синхронизируемых входов R и S. Работа в соответствии с данной таблицей осуществляется при сигнале несинхронизируемого входа R=1 и при С=1.

|

R |

S |

Q |

Примечание |

|

1 |

1 |

Q |

Хранение |

|

1 |

0 |

1 |

Установка 1 |

|

0 |

1 |

0 |

Установка 0 |

|

0 |

0 |

— |

Запрещено |

Таблица 3. 3.1.2 — Таблица

переходов для однотактного RS-триггера

3.1.2 — Таблица

переходов для однотактного RS-триггера

Входная информация заносится в синхронизируемый однотактный RS-триггер через элементы входной логики 1 и 2 в момент поступления сигнала синхронизации С. В отсутствие сигнала синхронизации триггер может быть установлен в состоянии 0 путем подачи на несинхронизируемые вход R сигнала R=0.

Двухтактный RS-триггер.

Устойчивая работа однотактных RS- триггеров в схеме с передачей информации между

триггерами возможно только в случае, если занесение в триггер информации

осуществляется после завершения передачи информации о прежнем его состоянии в

другой триггер (см. рисунок 3.3.1.5).

Это достаточно просто обеспечивается при использовании двух серий находящихся в

противофазе синхросигналов. Таблица 3.3.1.3 задает закон

функционирования такого двухтактного триггера. Этот тирггер изменяет свои

состояния только после окончания действия сигнала синхронизации С=1 (переход в

режим хранения информации). Поэтому из двухтактных триггеров можно строить

произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

Поэтому из двухтактных триггеров можно строить

произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

1 |

0 |

0 |

Установка 0 |

|

0 |

1 |

1 |

Установка1 |

|

1 |

1 |

— |

Запрещено |

Таблица 3. =1, первый RS- триггер перейдет в режим хранения,

а второй примет то же состояние, что и первый. В результате к следующему такту

на входе двухтактного RS- триггера появится сигнал нового состояния. На рисунке 3.3.1.6, приведена временная диаграмма иллюстрирующая

работу двухтактного RS-триггера.

=1, первый RS- триггер перейдет в режим хранения,

а второй примет то же состояние, что и первый. В результате к следующему такту

на входе двухтактного RS- триггера появится сигнал нового состояния. На рисунке 3.3.1.6, приведена временная диаграмма иллюстрирующая

работу двухтактного RS-триггера.

Рисунок 3.3.1.6 — Диаграмма работы двухтактного RS-триггера

Проектирование схем в Electronics Workbench

При проектировании схем в Electronics Workbench использовались элементы панели инструментов «Digital» и соответствующие функциональные элементы : Or, Nor, And, Nand.

Рисунок 3.3.1.7 — Панель инструментов «Digital»

Триггер типа D (от слова delay – задержка)

принимает информацию по одному входу и реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый

D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

Синхронизируемы однотактный D-триггер задерживает рапространение входного

сигнала на время паузы между синхросигналами (задержка на полпериода). Для

задержки на период (на один такт) используется двухтактный D-триггер.

D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый

D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

Синхронизируемы однотактный D-триггер задерживает рапространение входного

сигнала на время паузы между синхросигналами (задержка на полпериода). Для

задержки на период (на один такт) используется двухтактный D-триггер.

|

Inputs |

Outputs | |||||

|

D |

C |

S |

R |

Q |

Q^ |

|

|

X |

X |

1 |

0 |

0 |

1 | |

|

X |

X |

0 |

1 |

1 |

0 | |

|

X |

X |

0 |

0 |

1 |

0 | |

|

X |

0 |

1 |

1 |

Q’ |

QB’ | |

|

X |

1 |

1 |

1 |

Q’ |

QB’ | |

|

0 |

RE |

1 |

1 |

0 |

1 | |

|

1 |

RE |

1 |

1 |

1 |

0 | |

Таблица 3. —

инверсный информационный выход

—

инверсный информационный выход

Параметры S и

R служат для задания начальных условий

Триггер типа JK — универсален, с раздельной установкой нулевого и единичного состояния, в зависимости от соединения его входов он может работать как RS, T, D триггера. В отличие от триггера типа RS в нем не запрещена одновременная подача сигналов на оба входа. Входы J и K эквивалентны входам S и R установки триггера соответственно в состояния “1” и “0”.При объединении входов J и K и при подаче на них счетных импульсов.Вход J при раздельном использовании входов играет роль входа установки в единицу, а вход K — роль входа установки в нуль.

Рисунок 3.3.1.9 — Условное обозначение JK-триггера

Параметры синхронного JK-триггера:

C

— синхронизирующий входJ и K — информационные входы триггера

S — установка 1

R — установка 0

Q — информационный выход

Q^ — инверсный информационный выход

Параметры S и R служат для задания начальных условий (см.

X

X

X

1

0

0

1

X

X

X

0

1

1

0

X

X

X

0

0

1

0

X

X

0

1

1

Q’

QB’

X

X

1

1

1

Q’

QB’

0

0

FE

1

1

Q’

QB’

0

1

FE

1

1

0

1

1

0

FE

1

1

1

0

1

1

FE

1

1

QB’

Q’

Таблица 3. 3.1.5 — Таблица

истинности синхронного JK-триггера

3.1.5 — Таблица

истинности синхронного JK-триггера

Триггер типа T называется триггером со счетным входом (или счетным триггером). Он изменяет свое состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал. Обозначение триггера пришло от первой буквы анг.слова toggle-защелка.

Т.к. в Electronics Workbench не приводится T-триггер его можно получить объединив информационные входы JK-триггера.

Задание:

— схемы триггеров;

— временные диаграммы работы триггеров.

Задания выполняются соответственно по вариантам:

- Схема двухтактного RS-триггера на базе элементов ИЛИ-НЕ;

- Схема двухтактного RS-триггера с использованием микросхемы приведенной Electronics Workbench;

- Схема D -триггера с использованием микросхемы приведенной в Electronics Workbench;

- Схема JK-триггера с использованием микросхемы приведенной в Electronics Workbench;

- Схема T-триггера с использованием микросхемы приведенной в Electronics Workbench.

Примечание: Для построения и анализа работы T, D и JK триггеров используйте их условные обозначения.

Вернуться к содержанию

Вьетнамки | Таблица истинности и различные типы

Триггер — это электронная схема с двумя стабильными состояниями, которая может использоваться для хранения двоичных данных. Сохраненные данные можно изменить, применяя различные входные данные. Триггеры и защелки являются фундаментальными строительными блоками систем цифровой электроники, используемых в компьютерах, средствах связи и многих других типах систем. Оба используются в качестве элементов хранения данных. Это основной элемент хранения в последовательной логике. Но сначала давайте проясним разницу между защелкой и шлепанцем.

Триггеры и защелки являются фундаментальными строительными блоками систем цифровой электроники, используемых в компьютерах, средствах связи и многих других типах систем. Оба используются в качестве элементов хранения данных. Это основной элемент хранения в последовательной логике. Но сначала давайте проясним разницу между защелкой и шлепанцем.

Флип-флоп с защелкой

Основное различие между защелкой и триггером — это стробирующий или синхронизирующий механизм.

Простыми словами. Триггер срабатывает по фронту, а защелка срабатывает по уровню.

Полное сравнение триггеров с защелкой читайте здесь

Например, поговорим о защелках SR и триггерах SR. В этой схеме, когда вы устанавливаете S как активный, выход Q будет высоким, а Q ’будет низким. Это независимо ни от чего. (Это цепь с активным низким уровнем, поэтому активный здесь означает низкий уровень, но для цепи с активным высоким уровнем активный означает высокий уровень)

Защелка SR Триггер, с другой стороны, является синхронным и также известен как защелка SR с синхронизацией или синхронизацией.

На этой принципиальной схеме выход изменяется (т. Е. Изменяются сохраненные данные) только тогда, когда вы подаете активный тактовый сигнал. В противном случае, даже если S или R активны, данные не изменятся. Давайте посмотрим на типы шлепанцев, чтобы лучше понять.

SR Вьетнамки

Существует четыре основных типа триггеров, наиболее распространенным из которых является SR-триггер. Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). В этой системе, когда вы устанавливаете «S» как активный, выход «Q» будет высоким, а «Q ‘ »будет низким.После того, как выходы установлены, подключение схемы сохраняется до тех пор, пока «S» или «R» не станут высокими, или пока не будет отключено питание. Как показано выше, он самый простой и легкий для понимания. Два выхода, как показано выше, противоположны друг другу. Таблица истинности SR Flip-Flop выделена ниже.

| S | R | Q | Q ’ |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | ∞ | ∞ |

JK Триггер

Из-за неопределенного состояния в триггере SR требуется другой триггер в электронике. Триггер JK является усовершенствованием триггера SR, где S = R = 1 не является проблемой.

Триггер JK является усовершенствованием триггера SR, где S = R = 1 не является проблемой.

Условие входа J = K = 1 дает выход, инвертирующий состояние выхода. Однако при практическом тестировании схемы выходы такие же.

Проще говоря, если входные данные J и K различаются (т.е. высокий и низкий), то выход Q принимает значение J на следующем фронте тактового сигнала. Если J и K оба низкие, то никаких изменений не происходит. Если J и K оба имеют высокий уровень на фронте тактового сигнала, выход будет переключаться из одного состояния в другое.JK Flip-Flops могут функционировать как Set или Reset Flip-flops

| Дж | К | Q | Q ’ |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

Флип-флоп D

Триггер D — лучшая альтернатива, очень популярная в цифровой электронике. Они обычно используются для счетчиков, регистров сдвига и синхронизации входов.

Они обычно используются для счетчиков, регистров сдвига и синхронизации входов.

В этом случае выход может быть изменен только на фронте тактового сигнала, и если вход изменяется в другое время, выход не будет затронут.

| Часы | Д | Q | Q ’ |

| ↓ »0 | 0 | 0 | 1 |

| ↑ »1 | 0 | 0 | 1 |

| ↓ »0 | 1 | 0 | 1 |

| ↑ »1 | 1 | 1 | 0 |

Изменение состояния выхода зависит от нарастающего фронта тактового сигнала.Выход (Q) такой же, как и вход, и может изменяться только по нарастающему фронту тактового сигнала.

T Вьетнамки

T-триггер похож на JK-триггер. По сути, это версия триггеров JK с одним входом. Эта модифицированная форма триггера JK получается путем соединения обоих входов J и K. У него есть только один вход вместе с входом часов.

Эта модифицированная форма триггера JK получается путем соединения обоих входов J и K. У него есть только один вход вместе с входом часов.

Эти триггеры называются T-триггерами из-за их способности дополнять свое состояние (т. Е.) Toggle, отсюда и название Toggle flip-flop.

| т | Q | Q (т + 1) |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

Применение триггеров

Это различные типы триггеров, используемых в цифровых электронных схемах, и области применения триггеров указаны ниже.

- Счетчики

- Делители частоты

- Регистры сдвига

- Регистры памяти

Эта статья была впервые опубликована 17 августа 2017 г.

и обновлена 29 июня 2021 г.

и обновлена 29 июня 2021 г.Вьетнамки типа D

- Изучив этот раздел, вы сможете:

- Понимание работы триггеров типа D и банки:

- • Опишите типичные области применения триггеров типа D.

- • Распознавайте стандартные обозначения схем для триггеров типа D.

- • Распознавать триггерные интегральные схемы типа D.

- Узнайте об альтернативных формах шлепанцев типа D.

- • Триггеры типа D с синхронизацией по фронту.

- • Переключить шлепанцы.

- • Прочее.

- Постройте временные диаграммы, поясняющие работу триггеров типа D.

- Используйте программное обеспечение для моделирования триггеров типа D.

Рис. 5.3.1 Триггер типа D с триггером уровня

Вьетнамки типа D

Главный недостаток триггера SR (т. е. его неопределенный выход и недопустимые логические состояния), описанный в модуле цифровой электроники 5.2, преодолевается триггером типа D. Этот триггер, показанный на рис. 5.3.1 вместе с его таблицей истинности и типичным условным обозначением схемы, может быть назван триггером данных из-за его способности «фиксировать» и запоминать данные, или триггером задержки. потому что фиксация и запоминание данных могут использоваться для создания задержки в прохождении этих данных по цепи.Поэтому, чтобы избежать двусмысленности в названии, его обычно называют просто D-типом. Самая простая форма триггера типа D — это, по сути, высокоактивный тип SR с дополнительным инвертором, чтобы гарантировать, что входы S и R не могут одновременно иметь высокий или низкий уровень. Эта простая модификация предотвращает как неопределенные, так и недопустимые состояния триггера SR. Входы S и R теперь заменены одним входом D, и все триггеры типа D имеют вход синхронизации.

е. его неопределенный выход и недопустимые логические состояния), описанный в модуле цифровой электроники 5.2, преодолевается триггером типа D. Этот триггер, показанный на рис. 5.3.1 вместе с его таблицей истинности и типичным условным обозначением схемы, может быть назван триггером данных из-за его способности «фиксировать» и запоминать данные, или триггером задержки. потому что фиксация и запоминание данных могут использоваться для создания задержки в прохождении этих данных по цепи.Поэтому, чтобы избежать двусмысленности в названии, его обычно называют просто D-типом. Самая простая форма триггера типа D — это, по сути, высокоактивный тип SR с дополнительным инвертором, чтобы гарантировать, что входы S и R не могут одновременно иметь высокий или низкий уровень. Эта простая модификация предотвращает как неопределенные, так и недопустимые состояния триггера SR. Входы S и R теперь заменены одним входом D, и все триггеры типа D имеют вход синхронизации.

Операция.

Пока на входе тактовой частоты низкий уровень, изменения на входе D не влияют на выходы. Таблица истинности на рис. 5.3.1 показывает это как состояние «безразличие» (X). Базовый триггер типа D, показанный на рис. 5.3.1, называется триггером типа D с запуском по уровню, потому что то, активен ли вход D или нет, зависит от логического уровня входа часов.

Таблица истинности на рис. 5.3.1 показывает это как состояние «безразличие» (X). Базовый триггер типа D, показанный на рис. 5.3.1, называется триггером типа D с запуском по уровню, потому что то, активен ли вход D или нет, зависит от логического уровня входа часов.

При условии, что на входе CK высокий уровень (при логической 1), то какое бы логическое состояние ни было на D, появится на выходе Q и (в отличие от триггеров SR) Q всегда является инверсией Q).

На рис. 5.3.1, если D = 1, то S должно быть 1, а R должно быть 0, поэтому Q устанавливается равным 1.

Или

Если D = 0, тогда R должно быть 1, а S должно быть 0, в результате чего Q сбрасывается на 0.

Защелка данных

Название Data Latch относится к триггеру типа D, который запускается по уровню, так как данные (1 или 0), появляющиеся в D, могут быть удержаны или ‘зафиксированы’ в любое время, пока вход CK находится на высоком уровне (логика 1).

Как видно из временной диаграммы, представленной на рис 5. 3.2, если данные в D изменяются в течение этого времени, выход Q принимает тот же логический уровень, что и D.

3.2, если данные в D изменяются в течение этого времени, выход Q принимает тот же логический уровень, что и D.

Рис. 5.3.2 Временная диаграмма для триггера типа D, запускаемого по уровню

Сквозная пульсация

На рис. 5.3.2 также показана возможная проблема с триггером типа D, срабатывающим по уровню; если есть изменения в данных в течение периода, когда тактовый импульс находится на высоком уровне, логическое состояние в Q изменяется в соответствии с D, и « запоминает » только последнее входное состояние, которое произошло во время тактового импульса (период RT в Инжир.5.3.2). Этот эффект называется «сквозная пульсация», и хотя он позволяет использовать триггер типа D, запускаемый по уровню, в качестве переключателя данных, разрешая передачу данных только от D к Q до тех пор, пока CK удерживается на логической 1, это не может быть желательным свойством во многих типах схем.

Рис. 5.3.3 Триггер типа D с запуском по фронту с установкой и сбросом

Триггер типа D с кромкой

К счастью, пульсацию можно в значительной степени предотвратить с помощью триггера типа D с запуском по краю, показанного на рис. 3.3.

3.3.

Тактовый импульс, подаваемый на триггер, сокращается до очень узкого положительного тактового импульса длительностью всего около 45 нс за счет использования логического элемента И и подачи тактового импульса непосредственно на вход ‘a’, но с задержкой его поступления на вход ‘b ‘, пропустив его через 3 инвертора. Это инвертирует импульс, а также задерживает его на три задержки распространения (около 15 нс на затвор инвертора для затворов серии 74HC). Таким образом, логический элемент И создает логическую единицу на своем выходе только в течение 45 нс, когда оба ‘a’ и ‘b’ находятся на логической 1 после нарастающего фронта тактового импульса.

Синхронные и асинхронные входы

Дальнейшим усовершенствованием рис. 5.3.3 является добавление двух дополнительных входов SET и RESET, которые фактически являются исходными входами S и R базового триггера SR, активируемого низким уровнем.

Рис. 5.3.4 Триггер типа D с запуском по фронту

Обратите внимание, что теперь есть небольшая разница между активными низкими входами Set (S) и Reset (R) и входом D. Вход D СИНХРОННЫЙ, то есть его действие синхронизировано с часами, но входы S и R являются АСИНХРОННЫМИ i.е. их действие НЕ синхронизировано с часами. Входы SET и RESET на рис. 5.3.4 являются «активными на низком уровне», что показано кружками инверсии на входах S и R, что указывает на то, что они действительно являются S и R.

Вход D СИНХРОННЫЙ, то есть его действие синхронизировано с часами, но входы S и R являются АСИНХРОННЫМИ i.е. их действие НЕ синхронизировано с часами. Входы SET и RESET на рис. 5.3.4 являются «активными на низком уровне», что показано кружками инверсии на входах S и R, что указывает на то, что они действительно являются S и R.

Триггер срабатывает по положительному фронту, что показано на входе CK на рис. 5.3.4 символом клина. Клин, сопровождаемый инверсионным кругом, будет указывать на срабатывание по отрицательному (спадающему) фронту, хотя это обычно не используется на триггерах типа D.

Рис.5.3.5 Типичные условные обозначения для триггеров с торцевым спуском типа D

Временная диаграмма

«Триггер типа D, запускаемый по фронту, с асинхронной предустановкой и возможностью сброса», хотя и был разработан на основе базового триггера SR, становится очень универсальным триггером с множеством применений. Временная диаграмма, иллюстрирующая действие устройства, запускаемого по положительному фронту, показана на рис. 5.3.5.

5.3.5.

На положительных фронтах тактовых импульсов a и b на входе D высокий уровень, поэтому Q также высокий.

Непосредственно перед импульсом c на входе D устанавливается низкий уровень, поэтому на положительном фронте импульса c Q становится низким.

Между импульсами c и d асинхронный вход S переходит в низкий уровень и сразу устанавливает высокий уровень Q.

Затем триггер игнорирует импульс d, пока S имеет низкий уровень, но поскольку S возвращается в высокое состояние, а D также вернулся в свое высокое состояние до импульса e, Q остается высоким во время импульса e.

При положительном фронте импульса h низкий уровень входа D остается, сохраняя Q низким, но между импульсами h и i вход S становится низким, подавляя любое действие D и немедленно делая Q высоким.

D все еще имеет высокий уровень на положительном фронте импульса f, и поскольку триггер запускается по положительному фронту, изменение логического уровня D во время импульса f игнорируется до тех пор, пока не появится положительный фронт импульса g, который сбрасывает Q на свой низкий уровень.

Тактовый импульс i снова игнорируется из-за того, что S находится в активном низком состоянии, а Q остается на высоком уровне под управлением S до момента непосредственно перед импульсом j. На положительном фронте импульса j вход D восстанавливает контроль, но, поскольку D высокий, а Q уже высокий, выход Q не изменяется.

Наконец, непосредственно перед импульсом k, вход асинхронного сброса (R) переходит в низкий уровень и сбрасывает Q на низкий уровень (логический 0), что снова заставляет вход D игнорироваться.

Триггер типа D, запускаемый по фронту Резюме:

• При положительном фронте импульса CK Q примет тот же уровень, что и вход D, если только один из асинхронных входов не имеет управления.

• Логический 0 на асинхронном входе S в любой момент приведет к тому, что Q будет установлен в логическую 1 с момента, когда S перейдет в низкий уровень, до тех пор, пока первый импульс CK после S не вернется в логическую 1.

• Логический 0 на асинхронном входе R приведет к сбросу Q до логического 0 с момента, когда R перейдет в низкий уровень, до тех пор, пока первый импульс CK после R не вернется к логической 1.

• Действие асинхронных входов отменяет любое действие входа D.

• Оба асинхронных входа не должны иметь низкий уровень одновременно, так как Q и Q будут иметь логическую 1. Это недопустимое состояние.

Рис. 5.3.6 Триггер ведущего ведомого типа D

Триггер ведущего ведомого устройства типа D

Еще одна версия триггера типа D показана на рис.5.3.6 где два триггера типа D объединены в одно устройство, это триггер типа «ведущий-ведомый». Обозначения схемы для устройства ведущий-ведомый очень похожи на символы для триггеров с триггером, запускаемым по краю, но теперь разделены на две части пунктирной линией, как также показано на рис. 5.3.6.

FF1 (главный триггер) — это устройство, запускаемое по положительному фронту, и инвертированная версия импульса CK подается с основного входа CK на FF2 (ведомый), также срабатывает по положительному фронту.Обратите внимание, что хотя входы тактовых импульсов на символах схемы предполагают, что это устройство, запускаемое по отрицательному фронту, данные фактически берутся в FF1 на ПОЛОЖИТЕЛЬНОМ фронте импульса CK. Данные, конечно, также появляются в q1 в это время, но поскольку импульс CK инвертируется в ck2, FF2 одновременно видит спадающий фронт, поэтому игнорирует данные на d2.

Данные, конечно, также появляются в q1 в это время, но поскольку импульс CK инвертируется в ck2, FF2 одновременно видит спадающий фронт, поэтому игнорирует данные на d2.

После положительного фронта внешнего импульса CK, FF1 игнорирует любые дальнейшие данные в D, а на отрицательном фронте внешнего импульса CK данные, хранящиеся в q1, принимаются на вход d2 FF2, который теперь видит положительный фронт инвертированного импульса CK.Поэтому данные вводятся в D на положительном переднем (переднем) фронте CK-импульса, а затем появляются в Q на отрицательном переднем (заднем) фронте CK-импульса.

Рис. 5.3.7 Временная диаграмма для триггера ведущий-ведомый типа D

Рассматривая главный ведомый триггер как единое устройство, взаимосвязь между входом тактовой частоты (CK) и выходом Q действительно выглядит как устройство, запускаемое по отрицательному фронту, поскольку любое изменение на выходе происходит на заднем фронте тактовой частоты. пульс.Однако, как показано на рис. 5.3.7, на самом деле это не запуск по отрицательному фронту, потому что данные, появляющиеся в Q, когда тактовый импульс возвращается к логическому 0, на самом деле являются данными, которые присутствовали на входе D на RISING фронте CK. пульс. Любые дальнейшие изменения, которые могут произойти в данных на входе D во время тактового импульса, игнорируются. Триггеры типа «ведущий-ведомый» типа D также доступны с асинхронными входами S и R, что делает их действительно очень универсальным устройством.

5.3.7, на самом деле это не запуск по отрицательному фронту, потому что данные, появляющиеся в Q, когда тактовый импульс возвращается к логическому 0, на самом деле являются данными, которые присутствовали на входе D на RISING фронте CK. пульс. Любые дальнейшие изменения, которые могут произойти в данных на входе D во время тактового импульса, игнорируются. Триггеры типа «ведущий-ведомый» типа D также доступны с асинхронными входами S и R, что делает их действительно очень универсальным устройством.

Переключатель-триггер

Рис.5.3.8 Тип D с запуском по фронту, преобразованный в триггер

Перекидные триггеры являются основными компонентами цифровых счетчиков, и все устройства типа D могут быть адаптированы для такого использования. Когда для подсчета используется электронный счетчик, фактически подсчитываются импульсы, появляющиеся на входе CK, которые могут быть либо регулярными импульсами, полученными от внутренних часов, либо они могут быть нерегулярными импульсами, генерируемыми каким-либо внешним событием.

Когда тумблерный триггер используется в качестве одного из каскадов счетчика, его выход Q переходит в противоположное состояние (переключается) на высокий или низкий уровень на каждом тактовом импульсе.Большинство триггеров, срабатывающих по фронту, можно использовать в качестве триггеров с переключением, включая тип D, который можно преобразовать в триггеры с переключением с простой модификацией. Теоретически все, что необходимо для преобразования типа D, запускаемого фронтом, в тип T, — это подключить выход Q непосредственно к входу D, как показано на рис. 5.3.8. Фактический ввод теперь — СК. Эффект этого режима работы также показан на временной диаграмме на рис. 5.3.8 с использованием триггера D-типа, запускаемого положительным фронтом.

Переключение работы триггера

Предположим, что изначально CK и Q = 0.Тогда Q и D должны быть 1. На переднем фронте импульса CK логическая 1 в D разрешается в триггер, а в конце задержки распространения триггера появляется в Q, а Q меняется на логический 0 одновременно.

Этот логический 0 теперь возвращается обратно в D, но важно, чтобы он не сразу принимался на вход D, иначе могут возникнуть колебания, когда D постоянно изменяется между 1 и 0. Однако из-за задержки распространения триггера, когда логический 0 из Q поступает в D, очень короткий период запуска по фронту завершится, и изменение данных в D будет проигнорировано.

При следующем нарастающем фронте CK тактового сигнала 0 в D теперь переходит в Q, снова создавая Q и D логической 1. Таким образом, выход Q триггера переключается на каждом положительном фронте импульса CK.

Поскольку выход Q меняет состояние при каждом нарастающем фронте тактового импульса, период 0 и период 1 выхода Q всегда будут иметь одинаковую длину, а на выходе будет прямоугольная волна с отношением метки к пространству 1: 1, его частота будет вдвое меньше, чем у CK.

Чтобы использовать триггеры-переключатели в качестве простых двоичных счетчиков, несколько триггеров-переключателей могут быть подключены каскадом, при этом выход Q первого триггера в серии должен быть подключен к входу CK следующего триггера. флоп и так далее.Это тоже принцип частотного деления. Как именно счетчики и делители могут быть построены из триггеров, объясняется в модуле последовательной логики 5.6.

флоп и так далее.Это тоже принцип частотного деления. Как именно счетчики и делители могут быть построены из триггеров, объясняется в модуле последовательной логики 5.6.

Время передачи данных

Однако на практике использование прямой обратной связи от Q к D может вызвать проблемы, поскольку для обеспечения стабильной работы и предотвращения нежелательных колебаний в любой цифровой схеме важно, чтобы любые изменения логического уровня, происходящие в D, были стабильными, ( без перерегулирования, звона и т. д.) и на допустимом логическом уровне в течение короткого периода до и после того, как тактовый сигнал вызывает изменение. Эти периоды называются временем установки и удержания.

Рис. 5.3.9 Синхронизированная логическая установка и время удержания

Хотя легко представить, что тактовый сигнал инициирует изменение в определенное время, например когда возникает его нарастающий фронт, данные фактически синхронизируются на входе D, когда форма сигнала CK достигает определенного уровня напряжения. В затворах серии 74HC этот уровень составляет 50% от V DD , как показано на рисунке 5.3.9. Это показывает в расширенных временных деталях переходы, происходящие на входах D и CK триггера, запускаемого положительным фронтом.

В затворах серии 74HC этот уровень составляет 50% от V DD , как показано на рисунке 5.3.9. Это показывает в расширенных временных деталях переходы, происходящие на входах D и CK триггера, запускаемого положительным фронтом.

Чтобы гарантировать правильный запуск, важно, чтобы данные на входе D установились на допустимый логический уровень до того, как тактовый сигнал инициирует какое-либо изменение. Следовательно, должно пройти некоторое время с момента, когда вход D впервые станет действительным, чтобы дать время для любого медленного нарастающего импульса, любого выброса или звонка до того, как тактовый импульс выполнит выборку логического уровня.

Например, время между точкой (a) на рис. 5.3.9, где D изначально падает ниже 50% от V DD , и временем, когда CK повышается до своего порогового значения срабатывания 50% V DD (точка b ) называется временем настройки (t setup или t su ), а в микросхемах серии 74HC оно обычно составляет от 5 до 15 нс.

После точки запуска должен быть следующий период (от b до c на рис. 5.3.9), в течение которого данные в D должны оставаться на том же допустимом логическом уровне, чтобы гарантировать, что правильный логический уровень был принят.Это время называется временем удержания (t hold или t h ) и обычно составляет около 3 нс в ИС серии 74HC.

В схемах с последовательной логикой точная синхронизация жизненно важна. При проектировании схемы необходимо учитывать не только время установки и удержания, но также время распространения логических элементов или триггеров на каждом пути, по которому цифровой сигнал проходит через схему. Неспособность правильно рассчитать время может привести к таким проблемам, как «сбои», то есть внезапные резкие скачки, поскольку такое устройство, как триггер, мгновенно производит переход с одного логического уровня на другой и обратно.Такие сбои могут быть очень короткими (несколько наносекунд), но достаточными для переключения другого устройства на неверный логический уровень.

В таких устройствах, как триггеры, использующие как запуск, так и обратную связь, неправильная синхронизация также может привести к нестабильности и нежелательным колебаниям. Избежание таких проблем является основной причиной использования устройств запуска по фронту и устройств «ведущие ведомые».

ИС для триггеров типа D

Список микросхем триггеров типа D представлен ниже.

D Триггер в цифровой электронике

В схеме SR NAND Gate Bistable неопределенное входное условие SET = «0» и RESET = «0» запрещено.Это недостаток триггера SR. Это состояние:

- Отменить действие фиксации обратной связи.

- Установить оба выхода на 1.

- Потеря управления входом, который сначала переходит в 1, а на другом входе остается «0», с помощью которого контролируется результирующее состояние защелки.

Нам нужен инвертор , чтобы этого не происходило. Мы подключаем инвертор между входами Set и Reset для создания другого типа триггерной схемы, называемой D триггер , Delay flip flop, D-type Bistable, D-type flip flop.

D-триггер — самый важный триггер из других типов с тактовой частотой. Это гарантирует, что одновременно оба входа, то есть S и R, никогда не будут равны 1. Триггер задержки разработан с использованием стробируемого триггера SR с инвертором, подключенным между входами, что позволяет использовать один вход. D (Данные).

Этот единственный вход данных, который обозначен буквой «D», используется вместо входа «Set», а для дополнительного входа «Reset» используется инвертор. Таким образом, чувствительный к уровню D-тип или D-триггер сконструирован из чувствительного к уровню SR-триггера.

Итак, здесь S = D и R = ~ D (дополнение к D)

Блок-схема

Принципиальная схема Мы знаем, что триггер SR требует двух входов, то есть один для «УСТАНОВКИ» выхода, а другой для «СБРОСА» выхода. Используя инвертор, мы можем устанавливать и сбрасывать выходы только с одним входом, поскольку теперь два входных сигнала дополняют друг друга. В SR-триггере, когда оба входа равны 0, это состояние больше невозможно. Это двусмысленность, которая устраняется дополнением в D-триггере.

Это двусмысленность, которая устраняется дополнением в D-триггере.

В триггере D единственный вход «D» называется входом «Данные». Когда вход данных установлен на 1, триггер будет установлен, а когда он установлен на 0, триггер изменится и станет сброшен. Однако это было бы бессмысленно, поскольку выходной сигнал триггера всегда будет изменяться при каждом импульсе, подаваемом на этот вход данных.

Вход «CLOCK» или «ENABLE» используется, чтобы избежать этого для изоляции входных данных от схемы фиксации триггера. Когда вход часов установлен на истину, условие входа D копируется только на выход Q.Это составляет основу другого последовательного устройства, называемого D Flip Flop .

Когда вход часов установлен на 1, входы «set» и «reset» триггера установлены на 1. Таким образом, он не изменит состояние и не сохранит данные, присутствующие на его выходе до того, как произойдет переход часов. . Проще говоря, выход «фиксируется» на 0 или 1.

Таблица истинности для триггера D-типа

Символы ↓ и ↑ указывают направление тактового импульса. Триггер D-типа принял эти символы в качестве триггеров фронта.

Триггер D-типа принял эти символы в качестве триггеров фронта.

Вьетнамки — обзор | Темы ScienceDirect

2.3.3 Триггеры

Триггеры могут быть сконструированы из двух установленных вплотную прозрачных защелок, как показано на рис. 2.14. Когда часы на низком уровне, первая защелка прозрачна, а вторая — непрозрачна. Следовательно, данные будут продвигаться к внутреннему узлу X. Когда часы возрастут, первая защелка станет непрозрачной, блокируя новые входы, а вторая защелка станет прозрачной. Время установки триггера — это время установки первой защелки.Задержка от часов до Q — это время с момента, когда данные находятся в динамическом узле первой защелки и тактовые импульсы повышаются, до тех пор, пока данные не достигнут выхода триггера. Следовательно, очевидно, что сумма задержек установки и времени до Q триггера равна сумме задержек распространения через защелки, потому что в обоих случаях данные должны проходить через две защелки. Комбинируя это наблюдение с уравнениями 2.2 и 2.3, мы видим, что накладные расходы триггерной системы хуже, чем у прозрачной защелкивающейся системы, из-за перекоса часов.

Комбинируя это наблюдение с уравнениями 2.2 и 2.3, мы видим, что накладные расходы триггерной системы хуже, чем у прозрачной защелкивающейся системы, из-за перекоса часов.

Рисунок 2.14. Триггер из прозрачных защелок

На практике защелки, используемые в триггерах, могут быть немного проще, чем те, которые используются в автономных приложениях, потому что внутренний узел X защищен и не требует полной буферизации двух подключенных защелки. На рисунке 2.15 показаны такие оптимизированные триггеры, построенные из защелок затвора передачи и защелок TSPC.

Рисунок 2.15. Оптимизированные реализации триггера: традиционный (a) и TSPC (b)

Помните, что перекос между задними фиксаторами триггера должен быть небольшим, иначе триггер может иметь внутреннюю проблему минимальной задержки.Эта проблема проиллюстрирована на рисунке 2.16. Предположим, что φ сильно искажен относительно φ, возможно, потому, что локальный инвертор малоразмерен и, следовательно, слишком медленный. Когда часы падают, оба транзистора P 1 и P 2 на рисунке 2.15 будут одновременно включены в течение короткого периода времени. Это позволяет данным проходить от D к Q в течение этого времени, эффективно дискретизируя вход по заднему фронту тактового сигнала. Этой проблемы можно избежать, убедившись, что инвертор ϕ¯ достаточно быстр, чтобы выключить P 2 до поступления новых данных.Защелки TSPC невосприимчивы к этой проблеме, потому что они используют только один тактовый сигнал, но подвержены внутренним скачкам, когда наклон тактового сигнала очень медленный, что приводит к одновременному включению транзисторов с синхронизацией NMOS и pmos во время перехода. Модифицированная традиционная конструкция триггера, основанная на трехсторонних защелках вместо защелок затвора передачи, показанная на рис. 2.17 [24], также позволяет избежать внутренних гонок, поскольку данные будут проходить через транзисторы NMOS одного трехстояния и PMOS-транзисторы другого трехстороннего состояния, а не через транзисторы.

Когда часы падают, оба транзистора P 1 и P 2 на рисунке 2.15 будут одновременно включены в течение короткого периода времени. Это позволяет данным проходить от D к Q в течение этого времени, эффективно дискретизируя вход по заднему фронту тактового сигнала. Этой проблемы можно избежать, убедившись, что инвертор ϕ¯ достаточно быстр, чтобы выключить P 2 до поступления новых данных.Защелки TSPC невосприимчивы к этой проблеме, потому что они используют только один тактовый сигнал, но подвержены внутренним скачкам, когда наклон тактового сигнала очень медленный, что приводит к одновременному включению транзисторов с синхронизацией NMOS и pmos во время перехода. Модифицированная традиционная конструкция триггера, основанная на трехсторонних защелках вместо защелок затвора передачи, показанная на рис. 2.17 [24], также позволяет избежать внутренних гонок, поскольку данные будут проходить через транзисторы NMOS одного трехстояния и PMOS-транзисторы другого трехстороннего состояния, а не через транзисторы. pmos-транзисторы обоих каскадов.Конечно, хотя необходимо избегать внутренних скачков, это не устраняет проблему минимальной задержки между триггерами.

pmos-транзисторы обоих каскадов.Конечно, хотя необходимо избегать внутренних скачков, это не устраняет проблему минимальной задержки между триггерами.

Рисунок 2.16. Смещение часов может вызвать внутреннюю гонку в триггерах.

Рисунок 2.17. Конструкция триггера без гонок

Традиционный триггер можно сделать статическим, добавив обратную связь на динамические узлы после каждого из двух ворот передачи. Это было бы очень дорого в триггере TSPC по трем причинам: (1) наличие трех динамических узлов вместо двух, (2) отсутствие инвертированной версии каждого узла для обратной связи и (3) отсутствие дополнительных часов для работы ворот передачи.

Полудинамический триггер Класса (SDFF) [47, 48] на рис. 2.18 основан на другой идее. Как и импульсная защелка Партови, она работает по принципу пересекающихся импульсов. По сравнению с защелкой Partovi, она может иметь немного меньшую задержку распространения, но запускается по фронту и, таким образом, теряет устойчивость к перекосу и возможности заимствования времени импульсных защелок. Класс SDFF заменяет статический логический элемент nand импульсной защелки Partovi, показанный на рис. 2.13, на динамический nand. Поскольку узел X гарантированно монотонно падает при высоком тактовом сигнале, выходной каскад также можно упростить, удалив N 3 · . Другая модификация состоит в том, что ϕ¯D стробируется X. Если D низкий, ϕ¯D упадет на три задержки затвора после повышения тактовой частоты, обеспечивая очень узкий импульс. Если D высокий, X начнет понижаться, и ϕ¯D не упадет. Это дает больше времени для X , чтобы полностью упасть, и якобы позволяет получить более узкий импульс, чем это было бы возможно, если бы X приходилось тянуть от высокого до минимума во время импульса. Еще одно преимущество состоит в том, что быстрая и относительно сложная логика может быть встроена в первую ступень, которая ведет себя как динамический вентиль.Защелке требуются инверторы с перекрестной связью как на X , так и на Q для полностью статической работы.

Класс SDFF заменяет статический логический элемент nand импульсной защелки Partovi, показанный на рис. 2.13, на динамический nand. Поскольку узел X гарантированно монотонно падает при высоком тактовом сигнале, выходной каскад также можно упростить, удалив N 3 · . Другая модификация состоит в том, что ϕ¯D стробируется X. Если D низкий, ϕ¯D упадет на три задержки затвора после повышения тактовой частоты, обеспечивая очень узкий импульс. Если D высокий, X начнет понижаться, и ϕ¯D не упадет. Это дает больше времени для X , чтобы полностью упасть, и якобы позволяет получить более узкий импульс, чем это было бы возможно, если бы X приходилось тянуть от высокого до минимума во время импульса. Еще одно преимущество состоит в том, что быстрая и относительно сложная логика может быть встроена в первую ступень, которая ведет себя как динамический вентиль.Защелке требуются инверторы с перекрестной связью как на X , так и на Q для полностью статической работы. Недостатком обычных триггеров является то, что, как и у импульсных триггеров, время удержания увеличивается на ширину импульса.

Недостатком обычных триггеров является то, что, как и у импульсных триггеров, время удержания увеличивается на ширину импульса.

Рисунок 2.18. Класс полудинамический триггер

Еще одна конструкция триггера — это триггер с усилителем чувствительности (SAFF) [28, 55, 58] на рис. 2.19, который использовался в Alpha 21264 и в StrongARM. Триггер требует дифференциальных входов и производит дифференциальный выход.Его можно понимать как двойной буфер домино с регенеративной обратной связью, за которым следует SR-защелка на выходе для сохранения состояния выхода во время предварительной зарядки. Примечательно, что единственный транзистор N 4 служит для стабилизации защелки; этот транзистор можно не использовать в динамических реализациях.

Рисунок 2.19. Триггер усилителя чувствительности

При низком тактовом сигнале транзистор оценки N 1 выключен и транзисторы предварительной зарядки P 3 и P 4 вытягивают внутренние узлы X и X¯ высокая. Когда часы повышаются, один из входов будет иметь более высокое напряжение, чем другой. Это вызовет опускание соответствующего узла X или X¯. Транзисторы P 1 , P 2 , N 5 и N 6 вместе образуют пару инверторов с перекрестной связью, которая выполняет регенеративную обратную связь для усиления разницы между X и ИКС. Первоначально оба N 5 и N 6 включены, что позволяет любой из сторон тянуть низко.Когда одна сторона опускается, транзистор NMOS на другой стороне начинает отключаться, а транзистор pmos начинает включаться, удерживая другую сторону на высоком уровне. Как только одна сторона полностью опущена, триггер перестает реагировать на входные изменения, поэтому время удержания довольно короткое. Если входной сигнал изменяется, внутренние узлы можно оставить плавающими, если только слабый статификатор N 4 не доступен для обеспечения тонкой струйки тока. Когда часы падают, внутренние узлы предварительно заряжают, но перекрестно связанные вентили nand на выходе служат в качестве защелки SR для сохранения значения.

Когда часы повышаются, один из входов будет иметь более высокое напряжение, чем другой. Это вызовет опускание соответствующего узла X или X¯. Транзисторы P 1 , P 2 , N 5 и N 6 вместе образуют пару инверторов с перекрестной связью, которая выполняет регенеративную обратную связь для усиления разницы между X и ИКС. Первоначально оба N 5 и N 6 включены, что позволяет любой из сторон тянуть низко.Когда одна сторона опускается, транзистор NMOS на другой стороне начинает отключаться, а транзистор pmos начинает включаться, удерживая другую сторону на высоком уровне. Как только одна сторона полностью опущена, триггер перестает реагировать на входные изменения, поэтому время удержания довольно короткое. Если входной сигнал изменяется, внутренние узлы можно оставить плавающими, если только слабый статификатор N 4 не доступен для обеспечения тонкой струйки тока. Когда часы падают, внутренние узлы предварительно заряжают, но перекрестно связанные вентили nand на выходе служат в качестве защелки SR для сохранения значения.

SAFF не очень быстрый триггер общего назначения. Один из внутренних узлов должен сначала опуститься, в результате чего один из выходов повысится, а затем другой выход упадет, что приведет к трем задержкам гейта на флопе. Однако у SAFF есть и другие преимущества. Он используется в Alpha 21264 для усиления размаха сигнала 200 мВ [22] из файла регистров и на других сильно загруженных внутренних шинах, что значительно сокращает задержку размаха входного сигнала. Поскольку ядро флопа — это просто ворота домино с двумя направляющими, в гейт легко встроить логику для большей скорости.Однако следует проявлять осторожность при включении логики, чтобы избежать шума разделения заряда, который неправильно отключает усилитель считывания. Наконец, когда триггер взаимодействует с логикой домино, защелка SR может быть удалена, потому что логике домино не нужны входы, чтобы оставаться стабильной в течение всего цикла. Таким образом, SAFF — хороший выбор для определенных приложений, в которых его уникальные особенности полезны.

Стоянович и Оклобджия тщательно изучили варианты триггеров [81]. Исследование было сосредоточено на произведении задержки мощности, а не на задержке при фиксированных характеристиках входной и выходной емкости.Было установлено, что Klass SDFF является самым быстрым, в то время как традиционный триггер, состоящий из двух прозрачных защелок, обеспечивает самую низкую задержку мощности.

D Flip Flop — Учебники по цифровой электронике

Триггер — это базовый строительный блок последовательных логических схем. Это схема, которая имеет два стабильных состояния и может хранить один бит информации о состоянии. Выход изменяет состояние сигналами, подаваемыми на один или несколько управляющих входов.

Базовый D-триггер имеет вход D (данные), вход синхронизации и выходы Q и Q (обратные Q).При желании он также может включать PR (Preset) и CLR. (Очистить) контрольные входы.

Таблица истинности и диаграмма

СимулироватьВход часов обычно имеет треугольный вход. Этот триггер представляет собой триггер с положительным фронтом. Этот означает, что триггер изменяет выходное значение только тогда, когда тактовый сигнал находится на положительном фронте (или нарастающем фронте тактового сигнала). Существует также триггер, запускаемый по отрицательному фронту, который изменяется при отрицательном фронте тактового сигнала (или спадающем фронте тактового сигнала).

- Зеленый переключатель — это переключатель включения / выключения (похож на переключатель освещения в помещении).Красный переключатель — это переключатель мгновенного действия. (аналогично выключателю дверного звонка — обычно выключен).

- Q 0 — предыдущее состояние Q, а Q 0 — предыдущее состояние Q.

- PR и CLR

асинхронные входы — то есть выход немедленно реагирует на эти входные данные. Это активные низкие входы. Нажмите

на соответствующих зеленых переключателях и наблюдайте.

- PR предварительно устанавливает вывод на 1, а CLR сбрасывает вывод на 0.

- И PR, и CLR не может быть низким одновременно — выход не определен.

- с PR и CLR

установите высокий уровень, нажмите D (зеленый), CLK (красный) и наблюдайте.

- Q следует за D на переднем фронте CLK, только когда оба PR и CLR высоки.

- Когда CLK остается низким (или высоким, т. Е. Без тактового перехода), изменение входа D не влияет на выход Q (или Q равно Q 0 , предыдущее состояние).

- D является синхронным входом, т.е. выход изменяется только при наличии фронта тактового сигнала (в этом примере нарастающий фронт часов).

- Установив как PR, так и CLR до высокого, он идентичен базовому D-триггеру без этих двух управляющих сигналов.

- Посмотрите видео, чтобы узнать, как редактировать ввод (толстый) формы волны.

Примечания

- Выход Q теперь равен 0. Какими двумя способами можно изменить выход Q на 1?

- PR = 0. D = 0. CLK имеет нарастающий фронт синхросигнала. Почему Q выводит не следовать D и поменять на 0?

FAQ

Приложения

Счетчик пульсации деления на 4 — Соединяя D с Q, мы получаем счетчик деления на 2.Частота на выходе Q по сравнению с тактовой частотой входного сигнала частота CLK делится на два. Используя 2 триггера, можно рассчитать счетчик пульсаций деления на 4. полученный. Путем каскадирования n триггеров мы получаем деление на 2 n счетчик .

Счетчик звонков — Счетчик звонков — это сдвиговый регистр (каскадное соединение триггеры) с выходом последнего триггера, соединенным со входом первого.

Счетчик Джонсона — Счетчик Джонсона представляет собой модифицированный кольцевой счетчик, где инвертированный выход последнего триггера соединен со входом первого.

Поскольку доходы от рекламы падают, несмотря на рост числа посетителей, нам нужна ваша помощь в поддержании и улучшении этого сайта, что требует времени, денег и тяжелого труда. Благодаря щедрости наших посетителей, которые давали ранее, вы можете использовать этот сайт бесплатно.

Если вы получили пользу от этого сайта и можете, пожалуйста, отдать 10 долларов через Paypal . Это позволит нам продолжаем в будущее. Это займет всего минуту. Спасибо!

Я хочу дать!

Вьетнамки

Вьетнамки выдержки из:http: // www.elec.uq.edu.au/~3e211/pracs/prac2/prac2.htm Кафедра компьютерных наук и электротехники Университет Квинсленда Сент-Люсия Qld 4072 Австралия

Элементы памяти в последовательной схеме называются триггерами . Шлепки схема имеет два выхода, один для нормального значения и один для дополнительного значения сохраненный бит. Двоичная информация может входить в триггер разными способами и вызывать к разным типам шлепанцев.