НОУ ИНТУИТ | Лекция | Последовательностные функциональные узлы. Триггеры

Аннотация: Рассматривается принцип действия триггеров как простейших элементов электронной памяти.

Цифровое устройство называется последовательностным [1, с.91], если его выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. Поэтому говорят, что такие функциональные узлы «обладают памятью».

Триггер — это логическая схема с положительной обратной связью, которая может находиться только в одном из двух устойчивых состояний, принимаемых за состояние логического нуля и логической единицы.

В отличие от всех рассмотренных ранее комбинационных схем, работа которых определяется только входными сигналами, состояние триггера в текущий момент зависит и от его состояния в предыдущий момент времени. Иными словами, триггер — это схема с запоминанием [2].

RS-триггеры

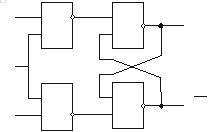

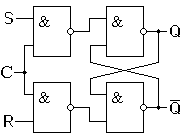

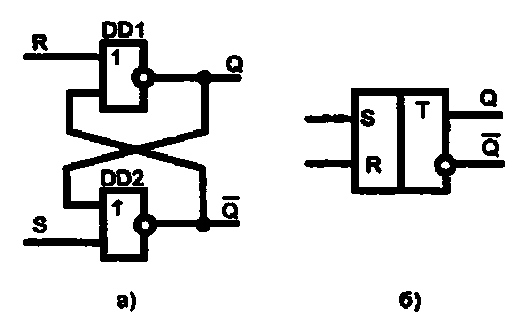

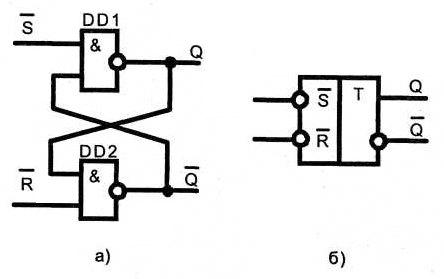

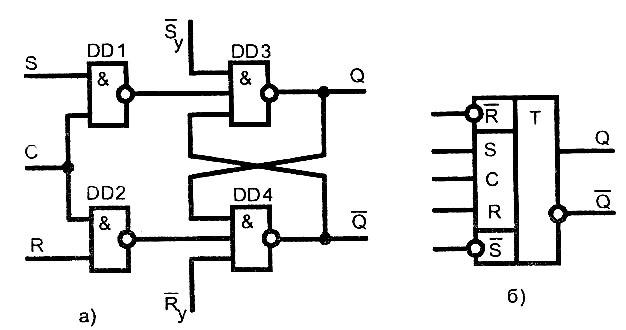

Простейшая функциональная схема RS — триггера в базисе ИЛИ-НЕ приведена на рис. 7.1,а. Здесь (от англ. Reset — сброс) — вход сброса триггера в состояние логического нуля, S (от англ. Set — устанавливать) — вход установки триггера в логическую единицу, — прямой выход триггера (состояние считается для триггера единичным, а противоположное, при , — нулевым), — инверсный выход триггера.

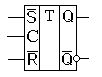

Рис. 7.1. RS-триггер в базисе ИЛИ-НЕ: а — функциональная схема; б — УГО

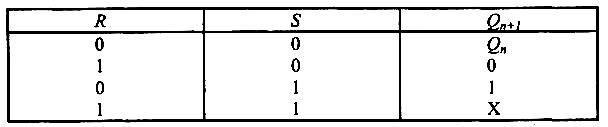

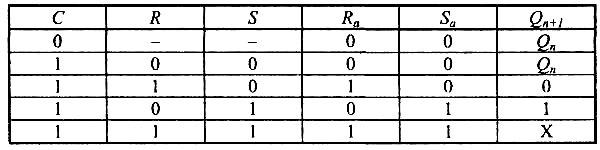

Очевидно, при наличии двух входных сигналов, возможны 4 варианта работы схемы (табл. 7.1). Начнем анализ с состояний, когда на один из входов подается решающий для элемента ИЛИ-НЕ сигнал логической 1.

Первая такая комбинация: , . является для логического элемента ИЛИ-НЕ решающим сигналом, который переключит нижний элемент схемы на рис. 7.1,а в логический , поэтому . Комбинация и переключит верхний элемент ИЛИ-НЕ в 1: . Таким образом происходит

Вторая комбинация: , . Решающий для ИЛИ-НЕ сигнал переключит выход в нулевое состояние, а сочетание и обеспечит переключение инверсного выхода в состояние . Триггер сброшен — то есть пришел в устойчивое нулевое состояние.

Если на оба входа подать , то состояние триггера будет определяться значениями и , поскольку логический 0 не является решающим для элемента ИЛИ-НЕ. Допустим, ранее

Для рассматриваемой схемы характерно также и то, что оба элемента

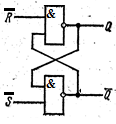

Функциональная схема простейшего триггера в базисе И-НЕ показана на рис. 7.2.а. Поскольку для функции И-НЕ решающим является сигнал логического нуля, активный уровень входных сигналов будет нулевым (табл. 7.2), что отражается на УГО триггера (рис. 7.2,б) в виде инверсного изображения входов и .

Рис. 7.2. RS-триггер в базисе И-НЕ: а — функциональная схема; б — УГО

Синхронный RS-триггер

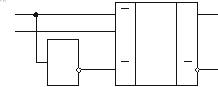

Основное назначение триггера в цифровых схемах — хранить выработанные логическими схемами результаты. Для отсечения еще не установившихся, искаженных переходными процессами результатов между выходом какой-либо логической схемы и входами триггера ставят ключи в виде элементов И-НЕ. Действие этого сигнала аналогично разрешающему сигналу в схеме дешифратора (рис. 4.2 в «Функциональные узлы комбинаторной логики. Дешифраторы» ). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал (рис. 7.3,а). При неактивном уровне на выходах первого и второго логических элементов И-НЕ будет логическая . Она не является решающей для функции И-НЕ, поэтому триггер на третьем и четвертом элементах будет хранить записанную ранее информацию. Таким образом, триггер не реагирует на изменения входных сигналов при . Если же синхросигнал становится активным ( ), то схема пропускает все переключения входных сигналов и (табл. 7.3). Поскольку входные ключи производят инверсию входных сигналов и , активным их уровнем будет логическая (рис. 7.3,б).

Рис. 7.3. Синхронный RS-триггер: а — функциональная схема; б — УГО

Недостатком схемы остается наличие недопустимой комбинации на входе, при которой получается неустойчивое состояние схемы.

Синхронный rs-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Теперь научимся записывать в триггеры входные логические сигналы только при наличии разрешающего сигнала.

Для этого нам потребуется схема, пропускающая входные сигналы только при наличии синхронизирующего сигнала.

Схема синхронного RS-триггера, построенного на элементах «И».

Таблица истинности синхронного RS-триггера. В этой таблице символ x означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

С | R | S | Q(t) | Q(t+1) | Пояснения |

0 | X | X | 0 | 0 | Режим хранения информации |

0 | X | X | 1 | 1 | |

1 | 0 | 0 | 0 | Режим хранения информации | |

1 | 0 | 0 | 1 | 1 | |

1 | 0 | 1 | 0 | 1 | Режим установки единицы S=1 |

1 | 0 | 1 | 1 | 1 | |

1 | 1 | 0 | 0 | 0 | Режим установки нуля R=1 |

1 | 1 | 0 | 1 | 0 | |

1 | 1 | 1 | 0 | * | R=S=1 запрещенная комбинация |

1 | 1 | 1 | 1 | * |

RS-триггеры могут быть реализованы на различных элементах. При этом логика их работы не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри БИС в виде готовых модулей), поэтому на принципиальных схемах синхронные триггеры обычно изображаются в виде условно-графических обозначений.

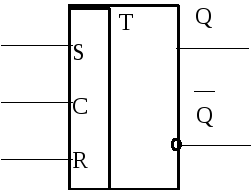

Условно-графическое обозначение синхронного RS-триггера

Статический d-триггер

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке.

Схема

D триггера (защелки)

Схема

D триггера (защелки)

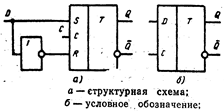

Такой триггер получил название D триггер. Название D триггера происходит от английского слова delay — задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D триггера на принципиальных схемах приведено на рисунке.

Условно-графическое

обозначение D триггера (защелки)

Условно-графическое

обозначение D триггера (защелки)

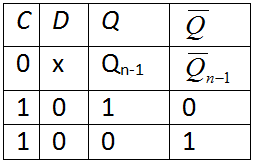

Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

С | D | Q(t) | Q(t+1) | Пояснения |

0 | x | 0 | 0 | Режим хранения информации |

0 | x | 1 | 1 | |

1 | 0 | x | 0 | Режим записи информации |

1 | 1 | x | 1 |

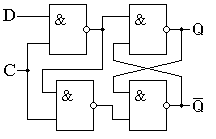

Нужно отметить, что в ТТЛ микросхемах самый распространённый элемент — это «2И-НЕ». Принципиальная схема D триггера на элементах «2И-НЕ» приведена на рисунке.

Принципиальная

схема D триггера на элементах «2И-НЕ»

Принципиальная

схема D триггера на элементах «2И-НЕ»

Расширить функциональные возможности синхронных триггеров можно добавлением асинхронных потенциальных входов. На практике чаще всего добавляют асинхронные потенциальные входы S и R записи в триггер логического нуля и единицы. Для этого в схеме статического триггера добавим еще один вход в логических элементах «2И-НЕ».

Схема

статического D-триггера с дополнительными

входами R и S

Схема

статического D-триггера с дополнительными

входами R и S

Условно-графическое

статического D-триггера с дополнительными

входами R и S

Условно-графическое

статического D-триггера с дополнительными

входами R и S

определение, виды триггеров, асинхронный rs-триггер,

синхронный RS-триггер, двухтактный RS-триггер — эл. схемы, обозначения,

таблицы истинности.

Триггеры –

это логическое устройство, способное

хранить 1 бит (0 или 1) информации и имеющую

2 устойчивых состояния.

Виды:

Асинхронные (не тактируемые)

Синхронные (тактируемые). Тактовые импульсы играют роль – разрешающего сигнала, которые разрешает изменение состояния триггера, или переход из 1 состояния в другое.

Асинхронный RS-триггер

R-вход сброса (reset), сброс в ноль

S-вход установки (set), уровень логической единицы устанавливается в единицу.

Обозначение:

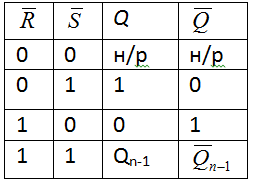

Таблица истинности:

-инверсный

вход, на него подаем «0», на Q

«1»

-инверсный

вход, на него подаем «0», на Q

«1»

-на

«0», то на Q

«0»

-на

«0», то на Q

«0»

Обозначение:

Таблица истинности:

Синхронный RS-триггер «2И-НЕ»

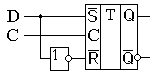

Обозначение:

Таблица истинности:

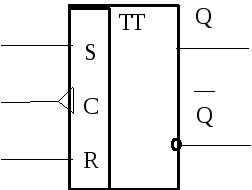

2Х тактный rs-триггер

Обозначение:

Зачастую требуется чтоб на выходе триггера информация появлялась уже после того, как закончится тактовый импульс и входа триггера будут заперты в таком случае используют 2хтактовый триггер.

«-»: наличие запрещенного состояния входов(непредсказуемость).

IK— триггер, D-триггер — схема, принцип действия, таблицы истинности,

регистры сдвига.

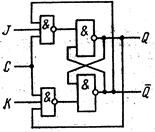

IK— триггер.

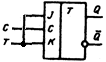

Обозначение:

Таблица истинности:

JK-триггер в отличие от RS-триггера не имеет запрещенного состояния входов и при комбинации всех «1» изменяет состояние выходов на противоположное.

D-триггер(триггер задержки)

Таблица истинности:

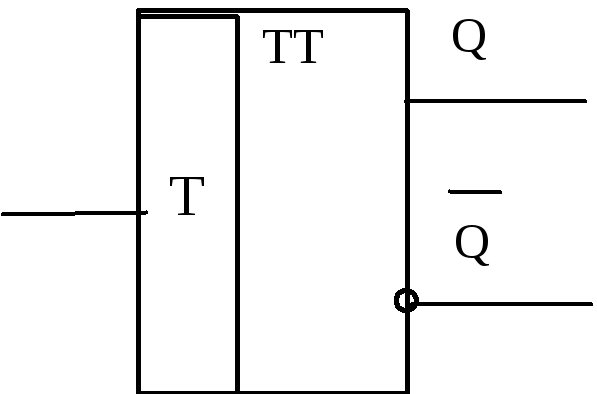

Т-триггер

После прохождения каждого импульса на входе Т изменяет состояние выхода Q на противоположный.

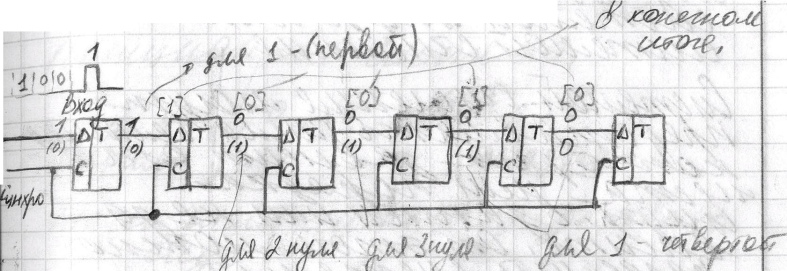

Сдвигающий регистр — это группа триггеров, соединенных таким образом, что информация из каждого триггера может передаваться в следующий триггер, сдвигая код, записанный в регистре. В зависимости от направления сдвига различают регистры:

— со сдвигом вправо (в сторону младших разрядов), — со сдвигом влево (в сторону старших разрядов), — реверсивные (сдвигающие и вправо и влево).

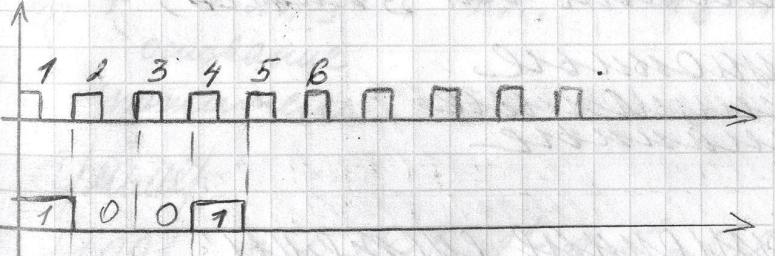

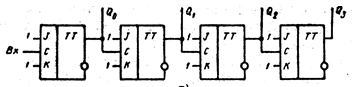

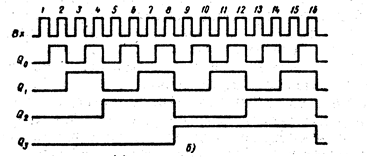

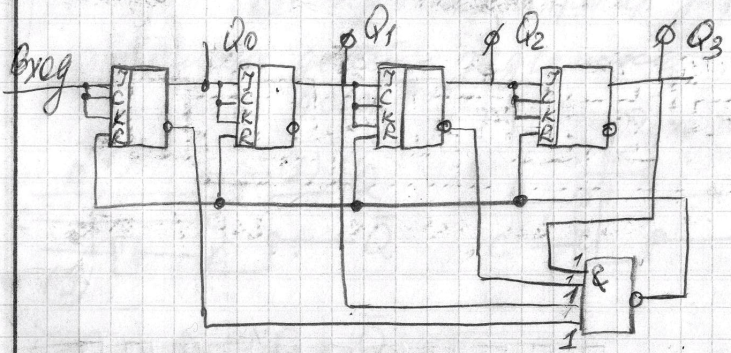

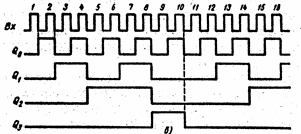

Двоичные счетчики: схема, принцип действия, временные диаграммы.

Двоичный счетчик

Временная диаграмма:

Q0=20=1, Q1=21=2, Q2=22=4, Q3=23=8.

Для 6-(0110)=2+4=6

Для 9-(1001)=8+1=9

Для 12-(0011)=8+4=12

Двоично-десятичный счетчик

Векторная диаграмма:

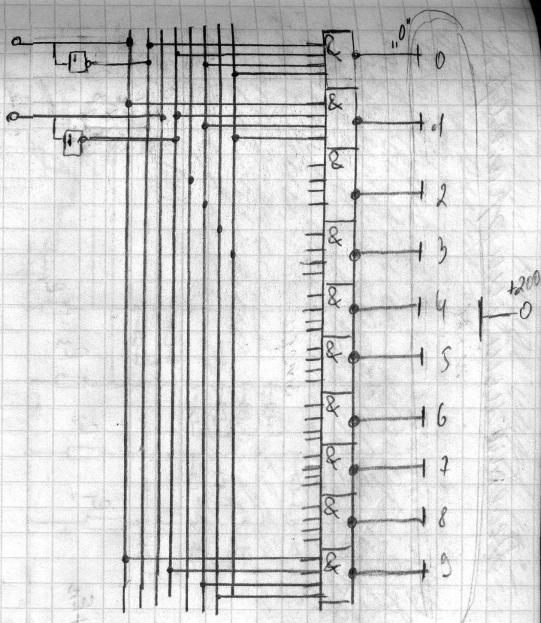

Двоично-десятичные шифратор и дешифратор: схема, принцип действия.

Система счисления – символический метод записи чисел, т.е. представление чисел с помощью численных знаков. Число абстрактная мера количества, цифра – знак для записи чисел, для небольшого количества достаточно 1 цифры, но в большинстве цифр или системы счисления

Системой счисления могут представлять числа величина которых зависит от места или порядка цифр в записи или не зависеть. От этого можно разделить системы на 3 класса:

Позиционные – значение цифры на прямую зависят от положения в числе.

Непозиционные – не зависят от положения в числе.

Смешанные

В машинах для записи машинных кодов используют двоичную систему счисления.

Общий вид позиционной

системы:

Такие числа можно

представить в виде  , a – множитель, f – основание.

, a – множитель, f – основание.

Дешифратор

Дешифраторы являются преобразователями дискретных сигналов, т. е. позволяют получать на выходе нужную комбинацию сигналов при подаче определенной комбинации сигналов на входе. В цифровых вольтметрах дешифраторы преобразуют двоично-десятичный код в соответствующие напряжения, управляющие цифровыми индикаторами, обеспечивающими визуальную индикацию в десятичном коде (например, код 2—4—2—1, 8—4—2—1 в десятичный код от 0 до 9). Для выполнения этой задачи обычно используют диодные схемы И, как наиболее простые и достаточно быстродействующие.

Помимо позиционного кода существует унитарный код или «1 из N».

«4И-НЕ».

Десятичный шифратор

Десятичный шифратор

Цифровые измерительные приборы

Синхронные rs-триггеры

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется «опасные гонки»), то запоминать состояния логической схемы в триггерах нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными триггерами. Для того чтобы отличать от них рассмотренные ранее варианты триггеров (RS-триггер и триггер Шмитта) эти триггеры получили название асинхронных.

Формировать синхронизирующие сигналы с различной частотой и скважностью при помощи генераторов и одновибраторов мы уже научились в предыдущих главах. Теперь научимся записывать в триггеры входные логические сигналы только при наличии разрешающего сигнала.

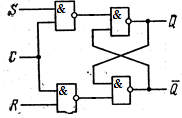

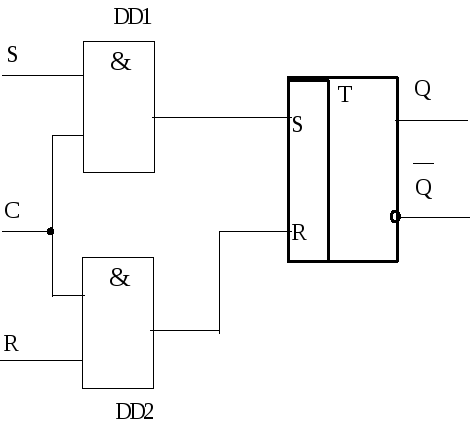

Для этого нам потребуется схема, пропускающая входные сигналы только при наличии синхронизирующего сигнала. Такую схему мы уже использовали при построении схем мультиплексоров и демультиплексоров. Это логический элемент «И». Принципиальная схема синхронного RS-триггера приведена на рисунке 5.

Рисунок 5.

Схема синхронного RS-триггера, построенного

на элементах «И»

Рисунок 5.

Схема синхронного RS-триггера, построенного

на элементах «И»

В таблице 2 приведена таблица истинности синхронного RS-триггера. В этой таблице символ x означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

Таблица 2. Таблица истинности синхронного RS-триггера.

С | R | S | Q(t) | Q(t+1) | Пояснения |

0 | x | x | 0 | 0 | Режим хранения информации |

0 | x | x | 1 | 1 | |

1 | 0 | 0 | 0 | 0 | Режим хранения информации |

1 | 0 | 0 | 1 | 1 | |

1 | 0 | 1 | 0 | 1 | Режим установки единицы S=1 |

1 | 0 | 1 | 1 | 1 | |

1 | 1 | 0 | 0 | 0 | Режим записи нуля R=1 |

1 | 1 | 0 | 1 | 0 | |

1 | 1 | 1 | 0 | * | R=S=1 запрещенная комбинация |

1 | 1 | 1 | 1 | * |

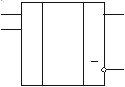

Как мы уже показали выше, RS-триггеры могут быть реализованы на различных логических элементах. При этом принцип их работы не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри БИС в виде готовых модулей), поэтому на принципиальных схемах синхронные триггеры обычно изображаются в виде условно-графических обозначений. Условно-графическое обозначение синхронного RS-триггера приведено на рисунке 6.

Рисунок 6.

Условно-графическое обозначение

синхронного RS-триггера

Рисунок 6.

Условно-графическое обозначение

синхронного RS-триггера

D-триггеры

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 7.

Рисунок 7.

Принципиальная схема D триггера

(защелки)

Рисунок 7.

Принципиальная схема D триггера

(защелки)

Такой триггер получил название D триггер. Название происходит от английского слова delay — задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D триггера на принципиальных схемах приведено на рисунке 8.

Рисунок 8.

Условно-графическое обозначение

D триггера (защелки)

Рисунок 8.

Условно-графическое обозначение

D триггера (защелки)

Таблица истинности D триггера достаточно проста, она приведена в таблице 3. Как видно из этой таблицы, данный триггер способен запоминать по синхросигналу и хранить один бит двоичной информации.

Таблица 3. Таблица истинности D триггера

С | D | Q(t) | Q(t+1) | Пояснения |

0 | x | 0 | 0 | Режим хранения информации |

0 | x | 1 | 1 | |

1 | 0 | x | 0 | Режим записи информации |

1 | 1 | x | 1 |

Нужно отметить, что отдельный инвертор при реализации триггера на ТТЛ элементах не нужен, так как самый распространённый элемент ТТЛ логики — это “2И-НЕ”. Принципиальная схема D триггера на элементах 2И-НЕ” приведена на рисунке 9.

Рисунок 9.

Схема D триггера, реализованная на

ТТЛ элементах

Рисунок 9.

Схема D триггера, реализованная на

ТТЛ элементах

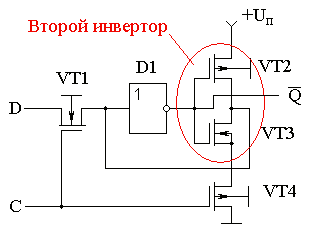

Ещё проще реализуется D триггер на КМОП логических элементах. В КМОП микросхемах вместо логических элементов «И» используются обычные транзисторные ключи. Схема D триггера приведена на рисунке 10.

Рисунок

10. Схема D триггера, реализованная на

КМОП элементах

Рисунок

10. Схема D триггера, реализованная на

КМОП элементах

При подаче высокого уровня синхросигнала C транзистор VT1 открывается и обеспечивает передачу сигнала с входа D на инверсный выход Q через инвертор D1. Транзистор VT2 при этом закрыт и отключает второй инвертор, собранный на транзисторах VT2 и VT3. При подаче низкого потенциала на вход C включается второй инвертор, который вместе с инвертором D1 и образует триггер.

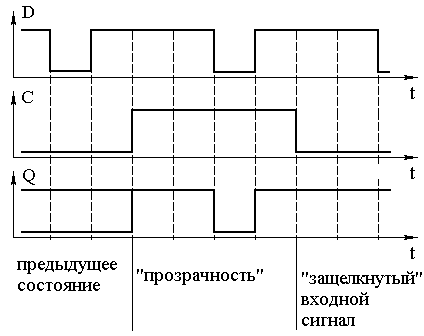

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню. Ещё одно название таких триггеров, пришедшее из иностранной литературы — триггеры-защёлки. Легче всего объяснить происхождение этого названия по временной диаграмме сигналов, приведенной на рисунке 11.

Рисунок 11.

Временная диаграмма D триггера

(защелки)

Рисунок 11.

Временная диаграмма D триггера

(защелки)

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на его вход.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы «защелкиваются» в этот момент, отсюда и название — триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

Синхронный rs — триггер.

Назначение синхронного RS-триггера.

Синхронный RS-триггер предназначен для предотвращения срабатывания RS — триггера от комбинаций с задержанными сигналами поступающими на вход.

Условное обозначения синхронного RS-триггера.

Рис. 6

На рисунке “С” обозначает время (clock).

Синхронный RS-триггер — RS — триггер, имеющий два информационных и 1 синхронный (тактовый) входы.

Схема синхронного RS-триггера.

Рис. 7

Как видно из рисунка, схема состоит из асинхронного RS-триггера и 2-х элементов И.

Работа синхронного RS-триггера.

При подаче на вход С “0” информация с S и R-входов на триггер не передается и состояние его не меняется

При С=1 сигналы с S и R- входов проходят на триггер и переключают его.

Если использовать RS-триггер с инверсными входами, то элементы И заменяются на элементы И-НЕ.

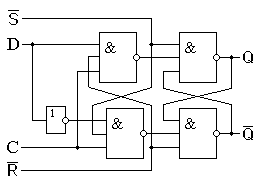

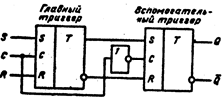

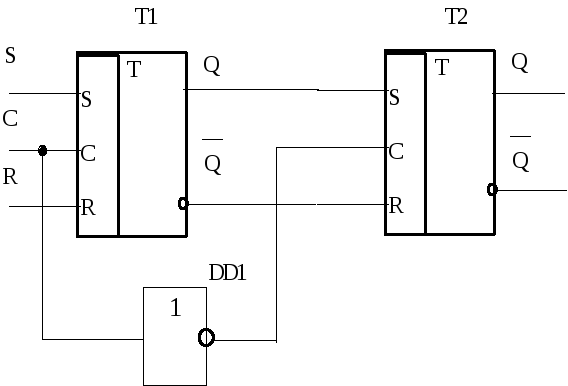

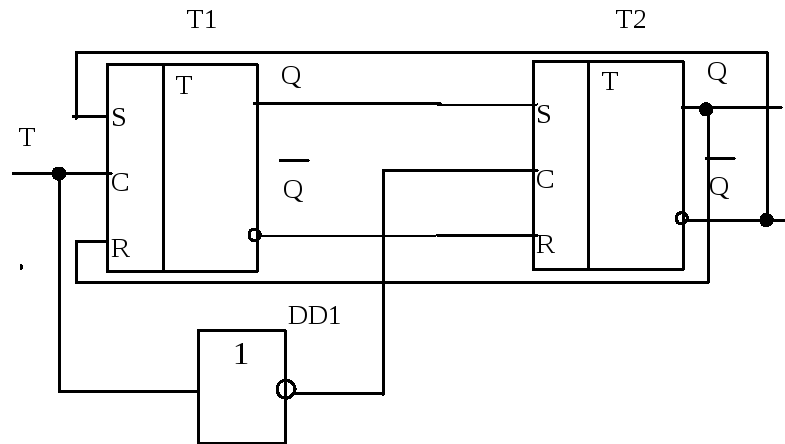

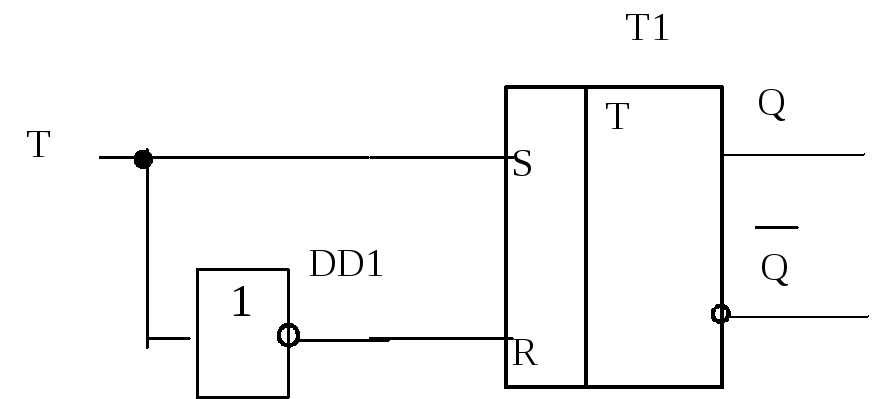

Двухступенчатый синхронный RS-триггер

Двухступенчатый синхронный RS-триггер — триггер, в состав которого входят 2 одноступенчатых синхронных RS-триггера и элемент ИЛИ-НЕ.

Назначение двухступенчатого синхронного RS-триггера.

Двухступенчатый синхронный RS-триггер предназначен для тактирования триггера фронтом импульса или перепадом потенциала.

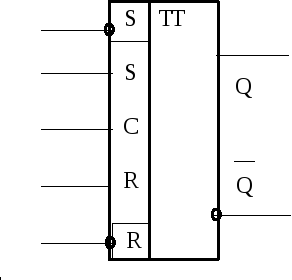

Условное обозначение двухступенчатого синхронного RS-триггера.

Рис. 8

Схема двухступенчатого синхронного RS-триггера.

Рис. 9

Работа двухступенчатого синхронного RS-триггера.

Каждая ступень представляет собой синхронный RS — триггер. При наличии на шине C логической 1 триггер Т1 воспринимает информацию, поступившую по шинам S и R которая и определяет его состояние. В это время за счет инвертора на входе С триггера Т2 действует 0 и его состояние не меняется.

В момент, когда С=0 на выходе инвертора DD1 появляется логическая единица U1, которая разрешает перезапись в триггер Т2 информации из триггера Т1.

Таким образом, информация в триггере Т1 записывается по фронту синхроимпульса, а в триггере Т2 — по его срезу.

Для расширения возможности триггеров возможно объединение синхронных и асинхронных триггеров.

Рис. 10

На

представленной схеме входы  ,

,  -входы асинхронного триггера, входы S,

R, C -входы синхронного триггера.

-входы асинхронного триггера, входы S,

R, C -входы синхронного триггера.

Обозначение представленного триггера — ТР.

Например: 555 ТР-2.

3. УНиверсальные триггеры

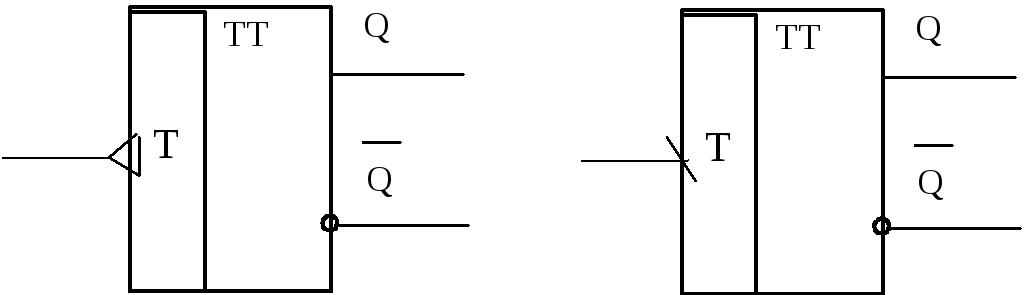

Т-триггеры

Т-триггер -триггер, имеющий один информационный вход и изменяющий свое состояние всякий раз, когда на вход поступает управляемый сигнал.

Т-триггер по другому называют триггером со счетным входом.

Т — триггер предназначен для выполнения следующих основных функций:

Получается Т — триггер путем введения соответствующей обратной связи в тактируемые (синхронные) RSC-триггеры.

На схемах Т — триггер обозначается следующим образом

Рис. 0.11

Принцип действия Т – триггера основан на следующем: число его переключений равно числу поступающих на его вход импульсов.

Схема Т – триггера имеет следующий вид:

Рис. 0.12

Рассмотрим работу Т — триггера.

Пусть Т — триггер находится в нулевом состоянии. Тогда на S входе действует логическая единица “1”, а на R входе — 0. При подаче синхронного импульса (т.е. при подаче “1” на вход С Т — триггера) триггер Т1 перейдет в единичное состояние, а триггер Т2 состояние не меняет. По окончании импульса на входе С триггера Т1 на входе С триггера Т2 появляется 1 и триггер Т2 переходит в единичное состояние. Теперь на S входе действует 0, а на R входе — 1.

Следовательно, под действием очередного импульса триггер Т1 и по срезу триггер Т2 перейдут в нулевое состояние.

Таким образом, под действием каждого импульса состояние триггера изменяется, т.е. Т-триггер должен переключаться каждым импульсом, поступающим на счетный вход триггера.

Рис. 0.13

Рассмотренные Т — триггеры нашли широкое применение в счетчиках.

Кроме описанных схем применяются так же и асинхронные Т триггеры. Условно-графическое обозначение такого триггера имеет вид:

Рис. 0.14

Асинхронные триггеры получают за счёт инвертирования одной последовательности импульсов поступающих на два разных входа. Сигнал инвертируется с помощью элемента ИЛИ-НЕ (НЕ), подключенного ко входу R.

Рис. 0.15

Таким образом, RS триггеры это триггеры с раздельным запуском. Их недостаток наличие запрещённых комбинаций сигналов подаваемых на входы этих устройств. Этого недостатка лишены Т-, D-, JK- триггеры.

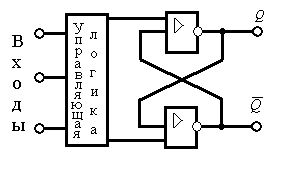

Триггеры

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер

имеет два выхода: прямой Q и

инверсный  . Состояние

триггера определяют по значению сигнала

на прямом выходе Q. Значения

сигналов на прямом и инверсном

выходах всегда противоположны.

. Состояние

триггера определяют по значению сигнала

на прямом выходе Q. Значения

сигналов на прямом и инверсном

выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

1. Rs-триггеры ‘

Асинхронные RS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. Асинхронные RS-триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS-триггер

— это триггер с раздельной установкой

состояний

логического нуля и логической единицы.

Он имеет два информационных входа S и R.. По

входу S триггер

устанавливается в состояние Q=1 ( =0), по

входу R — в

состояние Q=0 (

=0), по

входу R — в

состояние Q=0 ( =1). В зависимости от логической структуры

асинхронные RS-триггеры

бывают с прямыми либо инверсными входами

и могут строиться

на двух логических элементах:

2ИЛИ-НЕ — триггер с прямыми входами; или

на элементах 2И-НЕ

— триггер с инверсными входами.

=1). В зависимости от логической структуры

асинхронные RS-триггеры

бывают с прямыми либо инверсными входами

и могут строиться

на двух логических элементах:

2ИЛИ-НЕ — триггер с прямыми входами; или

на элементах 2И-НЕ

— триггер с инверсными входами.

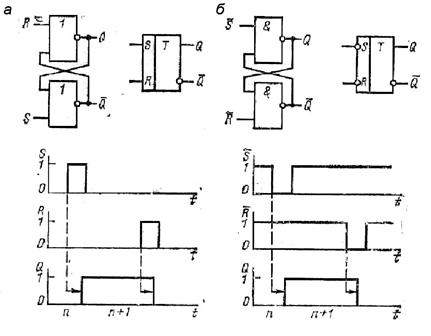

Асинхронный RS-триггер с прямыми входами на логических элементах 2ИЛИ-НЕ представлен на рис. 2.

Рис.2.

Логические

элементы ИЛИ-НЕ с инвертированием

сигнала образуют петлю положительной

обратной связи.

При таком соединении логическая единица

на выходе

одного логического элемента (ЛЭ) поступает

на вход другого

ЛЭ и обеспечивает логический ноль

(инвертирование)

на его выходе. Логический ноль на выходе

ЛЭ, поступая

на вход другого, при инвертировании

дает логическую

1. Таким образом, выходы Q и  всегда

находятся в противоположных состояниях.

Соединение элементов

по данной схеме позволяет получить цепь

с двумя устойчивыми

состояниями.

всегда

находятся в противоположных состояниях.

Соединение элементов

по данной схеме позволяет получить цепь

с двумя устойчивыми

состояниями.

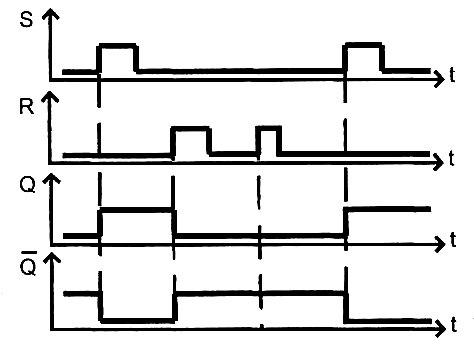

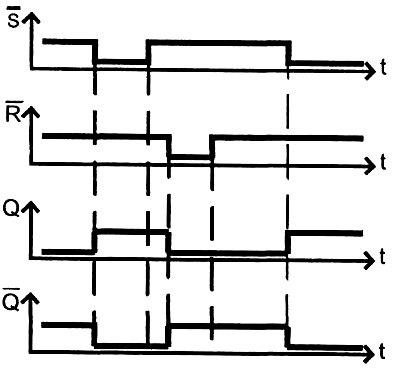

Временные диаграммы, характеризующие работу асинхронного RS-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для

элементов ИЛИ-НЕ активным является

высокий

уровень — логическая 1, поэтому в

режиме хранения данных на входы этого

триггера подаются нулевые значения R=S=0.

Установка триггера в нужное состояние

производится подачей на соответствующий

вход активного уровня единицы.

Одновременная подача единицы на оба

входа (R

и S)

приводит к неопределенности. На обоих

выходах Q и появляются

единицы, а после отключения входов

(S=R=0)

может установиться любое состояние.

Такая ситуация неопределенности не

допустима, поэтому комбинация S=R=1

считается запрещенной.

появляются

единицы, а после отключения входов

(S=R=0)

может установиться любое состояние.

Такая ситуация неопределенности не

допустима, поэтому комбинация S=R=1

считается запрещенной.

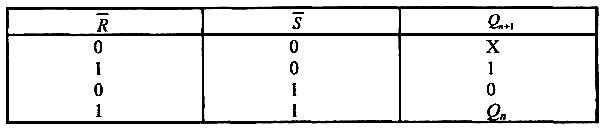

Функционирования триггера с прямыми входами на элементах 2ИЛИ-НЕ может быть отражено таблицей истинности

Асинхронный RS-триггер с инверсными входами на логических элементах 2И-НЕ представлен на рисунке 4.

Рис.4

Для этих ЛЭ логическая 1 является пассивным уровнем, поэтому сигнал R = S = 1 не влияет на состояние триггера и обеспечивает хранение предыдущего значения на выходах Qn+1= Qп. Для элементов И-НЕ активным является низкий уровень, т.е. логический 0.

Временные диаграммы работы асинхронного RS—триггера на элементах И-НЕ показаны на рис.5

Рис.5

В таблице показано функционирование асинхронного RS-триггера в инверсными входами на элементах 2И-НЕ.

Таблица переходов RS-триггера на элементах 2И-НЕ

Знак

«X»

при  =

= =0 означает,

что такая комбинация

является запрещенной.

=0 означает,

что такая комбинация

является запрещенной.

Синхронный RS-триггер имеет дополнительный вход синхронизации, который также называют тактирующим входом. Синхронизирующий вход разрешает прием сигналов с информационных входов. При наличии синхросигнала происходит переключение триггера. При отсутствии сигнала на синхровходе информационные сигналы не влияют на состояние триггера.

Достоинство синхронных триггеров: они позволяют устранить влияние задержки распространения сигнала в различных частях схемы. Таким образом, достигается одновременный прием сигналов в заданные интервалы времени в разных точках схемы.

В синхронных триггерах с динамическим управлением прием сигналов с информационных входов происходит в течение короткого фронта сигнала синхронизации. В остальное время информационные входы логически отключены и изменения сигналов на информационных входах не вызывают срабатываний синхронного триггера.

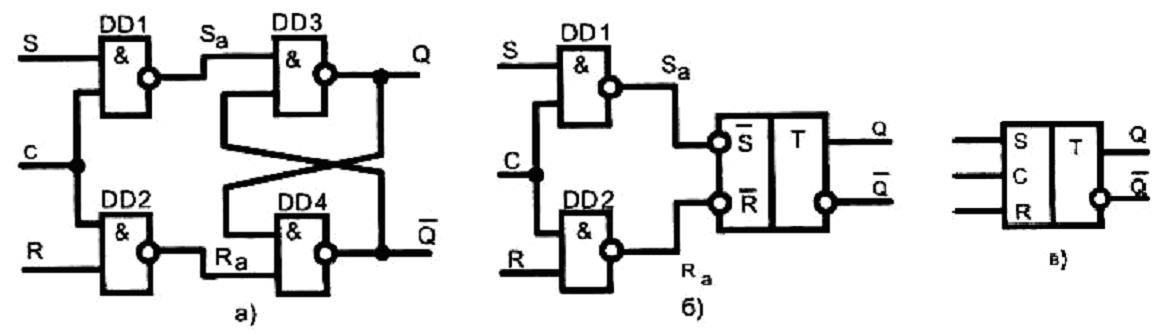

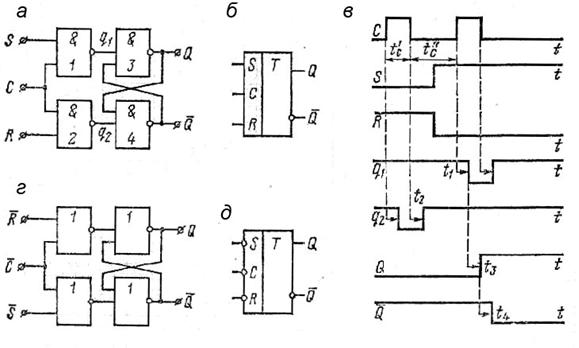

Логическая структура синхронного RS-триггера содержит асинхронный RS-триггер и дополнительную входную логическую схему, которая управляет его работой. На рис. 6 изображены схемы и обозначение синхронного RS-триггера с прямыми информационными и синхронизирующим входами. Такой триггер также называют RSТ-триггером, полагая вход С тактовым входом Т.

Рис.6

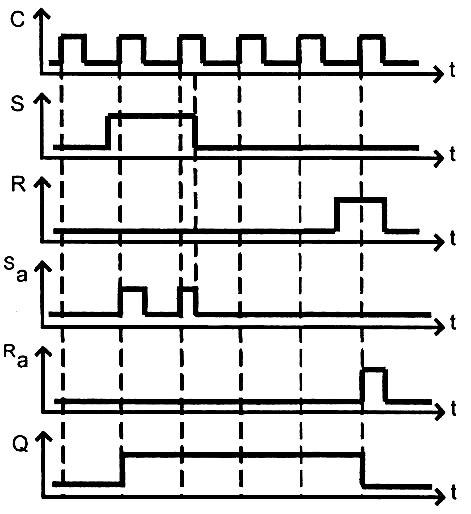

На входах кроме информационных сигналов R, S действует сигнал синхронизации С. Буквами Ra, Sa обозначены сигналы на входах асинхронного триггера. С помощью логических элементов DD1, DD2 обеспечивается передача входных сигналов на асинхронные триггеры. На рис. 7 изображены временные диаграммы работы синхронного RS-триггера с прямыми входами.

Рис.7

Таблица истинности синхронного RS-триггера

с прямыми входами (рис. 6, в)

При отсутствии синхронизирующего сигнала С=0 триггер не переключается независимо от входной информации R, S (прочерки в таблице). В этом режиме RST-триггер сохраняет ранее записанную в него информацию.

При С=1 триггер изменяет свое состояние в соответствии с поступившей на входы R и S информацией.

Триггеры могут дополнительно иметь установочные входы Ry, Sy,, сигналы которых непосредственно устанавливают триггер в заданное состояние независимо от синхросигналов (рис. 8).

Рис.8

При использовании для построения синхронного RS—триггера однотипных логических элементов (И-НЕ либо ИЛИ-НЕ) его синхронные либо асинхронные входы управляются различными активными логическими уровнями. В случае элементов И-НЕ для синхронных входов активным является сигнал логической единицы, а для асинхронных входов активным является сигнал логического 0. Условное графическое обозначение RS-триггера с прямыми информационными и инверсными установочными входами показано на рис. 8, б.

Асинхронные rs-триггеры

Асинхронные RS-триггеры имеют два информационных входа: вход S для установки 1, вход R для установки 0 и два выхода: прямой и инверсный .

Состояние триггера характеризуется сигналом на прямом выходе и определяется комбинацией входных сигналов. Например, для установки триггера в состояние 1, т. е. для записи в него 1, необходимо на его входы подать такую комбинацию сигналов, при которой на прямом выходе сигнал будет иметь уровень логической 1.

Асинхронный RS-триггер обычно строится на двух логических элементах И–НЕ либо ИЛИ–НЕ, охваченных перекрестными обратными связями

(рис. 2.1). На временных диаграммах отражена задержка срабатывания триггера, величина которой зависит от быстродействия логических элементов.

Рис. 1.1. Асинхронный RS-триггер: а – на логических элементах ИЛИ-НЕ; б – на логических элементах И–НЕ

Логика элементов И-НЕ, на которых построены триггеры, приведена в табл. 1.1 и имеет простое словесное выражение: любой ноль на входе дает единицу на выходе.

Аргументы Функция

x1 x2 И-НЕ

0 0 1

0 1 1

1 0 1

1 1 0

Для асинхронного RS-триггера (рис. 2.2,а) при подаче нуля на вход S и единицы на вход R (S=0, R=1) на прямом выходе будет уровень логической 1. Эта единица по цепи обратной связи поступает на один из входов нижнего по схеме элемента и вместе с единицей на входе R дает логический 0 на инверсном выходе. Это режим установки триггера в единичное состояние. Из этого анализа следует, что управляющими сигналами для этого триггера будут сигналы логического 0.

При входных сигналах S=1 и R=0 триггер будет установлен в нулевое состояние: на прямом выходе уровень логического 0, на инверсном – 1.

При подаче на оба входа нулевых сигналов на обоих выходах триггера появится уровень логической 1. Это запрещенный режим. Нельзя одновременно подавать сигналы на установку триггера в нулевое и единичное состояние.

В случае S=1 и R=1 триггер не изменяет своего состояния. В этом можно убедиться, предполагая последовательно, что триггер находился в нулевом или единичном состоянии. Полная таблица истинности RS-триггера приведена в табл. 1.2.

S R Q i Qi-1 Q t+1

0 0 0 1 1

0 1 0 1 0

1 0 0 0 1

1 1 0 0 1

0 0 1 1 1

0 1 1 1 0

1 0 1 0 1

1 1 1 1 0

Для триггера на элементах И–НЕ управляющим действием обладают нулевые уровни информационных сигналов, а не единичные. Если для триггера на элементах ИЛИ–НЕ единичные сигналы на обоих информационных входах запрещены, то для триггера на элементах И–НЕ они разрешены и образуют нейтральную комбинацию. Нулевые сигналы на обоих входах триггера на элементах ИЛИ–НЕ составляют нейтральную комбинацию, а для триггера на элементах И–НЕ они запрещены.

Синхронный одноступенчатый RS-триггер отличается от асинхронного наличием С-входа для синхронизирующих (тактовых) импульсов. Синхронный триггер состоит из асинхронного RS-триггера и двух логических элементов на его входе. Рассмотрим работу триггера, построенного на элементах И–НЕ (рис. 2.2, a).

При С = 0 входные логические элементы 1 и 2 блокированы: их состояния не зависят от сигналов на S- и R-входах и соответствуют логической 1, т. е. q1 = q2 = 1. Для асинхронного RS-триггера на элементах И–НЕ такая комбинация входных сигналов является нейтральной, поэтому триггер находится в режиме хранения записанной информации.

При С = 1 входные логические элементы открыты для восприятия информационных сигналов и передачи их на входы асинхронного RS-триггера. Таким образом, синхронный триггер при наличии разрешающего сигнала на S-входе работает по правилам для асинхронного триггера.

Временные процессы в триггере при его переключении из нулевого состояния в единичное иллюстрируются диаграммами на рис. 4.13, в, на которых обозначено: t1, t2, t3, t4 – задержки переключения соответствующих логических элементов; t’ с, t» с – длительности тактовых импульсов и пауз между ними.

Из

диаграмм следует, что минимальный  пер иод повторения тактовых импульсов

равен 4tзд.р,ср, а наибольшая частотаF

= 1/4tзд.р,ср.Синхронные

RS-триггеры строятся и на логических

элементах ИЛИ–НЕ (рис. 2.2), И–ИЛИ–НЕ и

их сочетаниях.

пер иод повторения тактовых импульсов

равен 4tзд.р,ср, а наибольшая частотаF

= 1/4tзд.р,ср.Синхронные

RS-триггеры строятся и на логических

элементах ИЛИ–НЕ (рис. 2.2), И–ИЛИ–НЕ и

их сочетаниях.