Принцип работы и таблица истинности D-триггеров

Триггеры представляют собой электронные устройства, которые могут находиться в одном из двух состояний длительное время. При внешнем воздействии (подаче сигнала извне) они изменяют своё состояние. Благодаря этому свойству их называют логическими элементами с памятью.

Микросхема 4х д-триггер SO16

Выходные сигналы зависят не только от того, какие импульсы подаются на вход, но и от того, что в триггере хранилось перед этим.

Данные устройства используются в основном в микропроцессорной технике. Микросхемы, как правило, имеют в своём составе триггер или бистабильный элемент и управляющую систему.

Триггеры бывают двух типов: асинхронные, или нетактируемые, и синхронные, или тактируемые.

В асинхронном – переход из одного положения в другое выполняется фронтом или перепадом напряжения. То есть для того, чтобы осуществился переход, на управляющем входе должна быть смена 1 на 0 или 0 на 1.

Синхронный тип переключается в новое положение в том случае, когда на управляющий вход подаётся импульс.

Выпускаются нескольких типов:

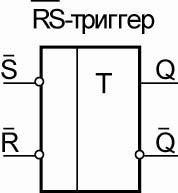

- RS-триггер;

- D-триггер;

- Т-триггер;

- JS-триггер.

Устройство д триггера

В цифровой и вычислительной технике наиболее распространённым является d-триггер. Иначе его называют триггером задержки (от английского слова delay).

Для производства d-триггера обычно используются полевые или биполярные транзисторы, а также интегральные микросхемы.

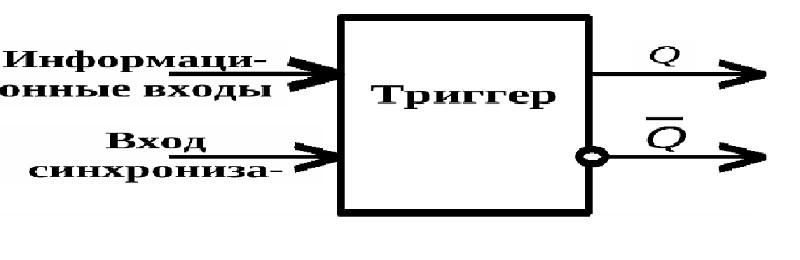

Для управления логическими элементами используются входы, которые делятся на информационные и вспомогательные. Информационные – воспринимают управляющие импульсы. В зависимости от его значения, в д-триггер записывается то или иное значение. Вспомогательные – предназначены для синхронизации работы.

Слово «задержка» в названии характеризует то, что поступивший информационный сигнал задерживается в нём ровно на один такт. Время задержки зависит от частоты импульсов синхронизации.

Схематическое изображение d-триггера

На картинке выше символом D обозначен информационный или вход данных, а С – тактовый или синхронизирующий. На информационный – подаётся информационный сигнал, который необходимо сохранить в д-триггере, а на тактовый вход подаётся тактовый импульс, в зависимости от значения которого определяется режим д-триггера: режим записи или режим хранения.

Принцип работы

Логическое устройство будет находиться в устойчивом положении в том случае, если на С=0. В этом случае импульсы, подающиеся на информационный D-вход, никак не влияют на прибор, и выходной импульс определяется записанным ранее значением. Если С=1, то выходной сигнал будет зависеть от того, какой т подан на информационный D-вход. Если D=1, то на выходе будет 1, если D=0, то на выходе будет 0.

Таблица истинности будет иметь вид

| Входной сигнал | Выходной сигнал | Режим работы | |

|---|---|---|---|

| С | D | Q | |

| 0 | 0 | определяется предыдущим состоянием | Хранение информации |

| 0 | 1 | определяется предыдущим состоянием | |

| 1 | 0 | 0 | Запись информации |

| 1 | 1 | 1 | |

Внимание! Логический компонент хранит информацию только при подаче нулевого значения на C-вход.

Д-триггер выполняется двух типов: с управлением по уровню и с управлением по фронту.

Элементы с управлением по уровню

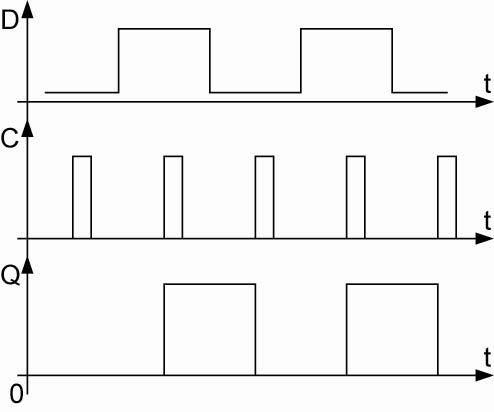

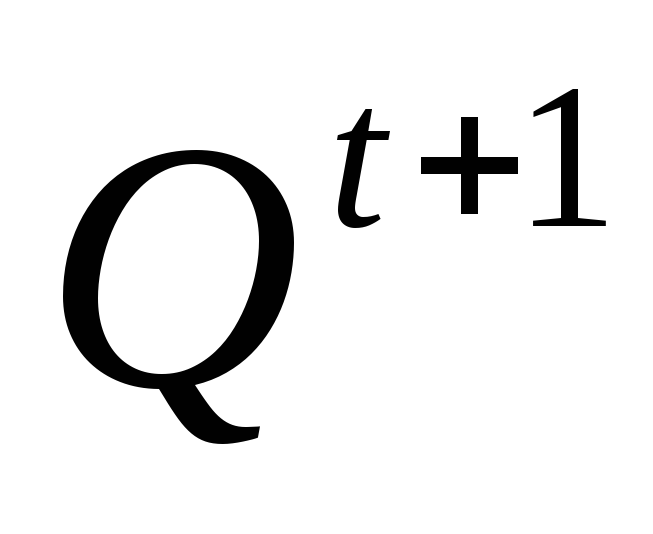

Временная диаграмма работы прибора со статическим управлением (по уровню сигнала) изображена на рисунке ниже.

Временная диаграмма работы d-триггера со статическим управлением

При статическом управлении переход из одного состояния в другое выполняется по уровню. Сигнал с D-входа будет записываться только при высоком уровне на тактовом C-входе.

Элементы с управлением по фронту

Данный тип логического устройства срабатывает при переходе с одного уровня на другой. Срабатывание может выполняться в двух случаях: по переднему и заднему фронту. По переднему, если переход выполняется от 0 к 1, и по заднему, если от 1 к 0.

Чтобы переключить d-триггер в нужное нам положение, сначала подаётся 0 или 1 на информационный D-вход. Если необходимо на выходе получить единицу, то D=1, если нужно, чтобы был на выходе ноль, то на D=0.

Затем на С-вход подаётся тактовый импульс. По его изменению элемент переключится в нужное нам состояние. При этом сигнал, который подаётся на D-вход, будет сохранён.

Такая логика работы делает электронный компонент очень удобным для хранения одного разряда двоичного числа (0 или 1). Причём, это состояние д-триггер будет сохранять до тех пор, пока не поступит следующий бит информации.

Временная диаграмма работы d-триггера с динамическим управлением

Для сброса д-триггера нужно, чтобы на входах D=0, а С=1. Однако таким образом не всегда можно управлять состоянием, поэтому в схемах используют компоненты с тремя входами.

Схематичное изображение d-триггера с тремя входами

В этом случае добавляется третий R-вход, который отвечает за сброс информации.

Схема реализации d-триггера

Реализация д-тригера может выполняться на основе ТТЛ (транзисторно-транзисторная логика) элементов, а также логических элементах КМОП.

Большинство микросхем относятся к компонентам с комплиментарной структурой – металл-оксид-полупроводник (КМОП). Данная технология основывается на использовании полевых транзисторов с изолированными затворами.

Реализация д-триггера на ТТЛ элементах приведена на рисунке ниже.

Схема устройства на ТТЛ-элементах

Если в логическом элементе D-вход соединить с инверсным выходом, то в этом случае прибор можно использовать в качестве счётного или Т-триггера. В этом случае при подаче импульса на С-вход логический компонент переходит в противоположное положение.

В сети интернет имеются сайты с сервисами, на которых можно просмотреть результат работы разного вида триггеров. Тип устройства выбирается из соответствующего списка.

Демонстрация работы устройств

Триггеры являются важной компонентой для создания различных микросхем. Их использование позволяет выполнять устройства с цифровой памятью. В микропроцессорной технике они являются основой для реализации электронных компонентов оперативной памяти. Их используют в регистрах сдвига и регистрах хранения.

Видео

Оцените статью:D – триггеры

D– триггеры имеет один информационный вход (D- вход) для установки в “1” или “0” и вход синхронизации С (происходит от словаdelay — задержка)

ОсобенностьD– триггеров:

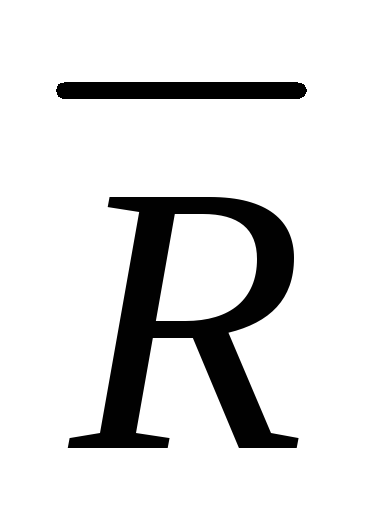

Сигнал на входе Qв тактеt+ 1 повторяет входной

сигнал в предыдущем такте

в предыдущем такте и сохраняет (запоминает) это состояние

до следующего тактового импульса, т.

е.D– триггер задерживает

на один такт информацию, существовавшую

на входеD.

и сохраняет (запоминает) это состояние

до следующего тактового импульса, т.

е.D– триггер задерживает

на один такт информацию, существовавшую

на входеD.

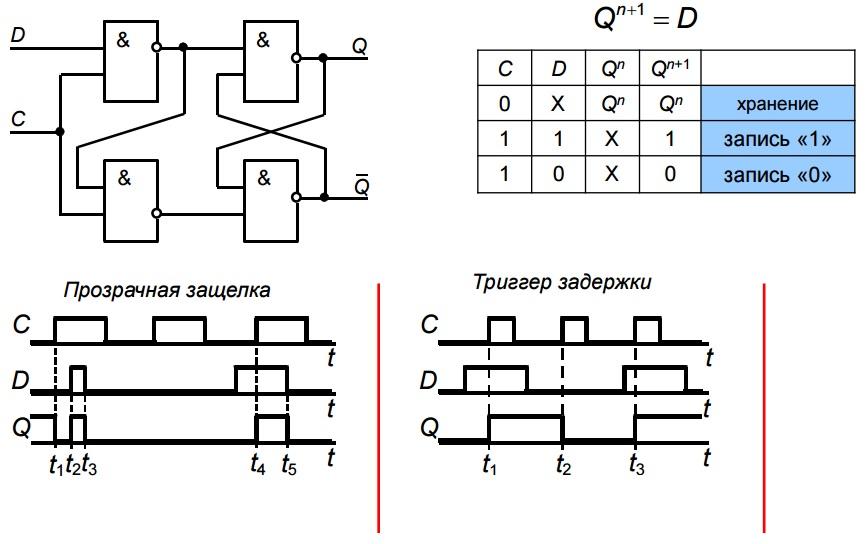

Закон функционирования D– триггера:

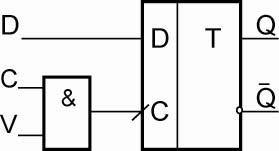

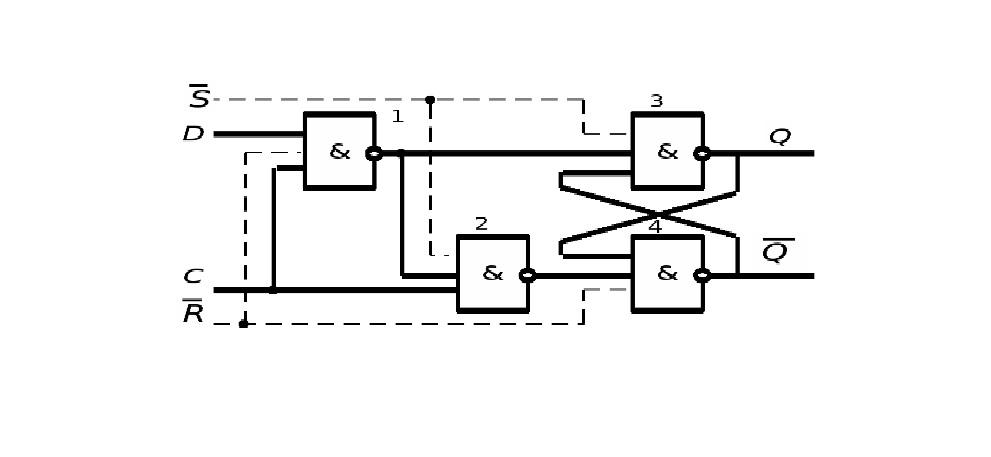

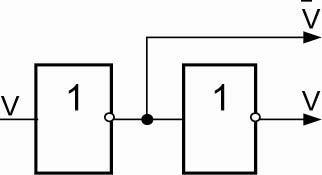

Структурная схема D– триггера и условные значения

а) – со статическим управлением

б) – с динамическим управлением

Таблица истинности.

Такт t | Такт t+ 1 | ||

C |

|  |

|

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 1 | |

1 | 1 | 1 | 1 |

При С = 0 состояние Тг устойчиво и не зависит от уровня сигнала на информационном входе D.

Сокращенная таблица

Такт t | Такт t+ 1 |

|

|

0 | 0 |

1 | 1 |

D– триггер можно образовать

из любого синхронногоRS- илиJK– триггера, если

на их информационные входы одновременно

подавать взаимно инверсные сигналыDи .

.

Хранение информации D– триггерами обеспечиваются за счет цепей синхронизации, поэтому все реальныеD– триггеры –тактируемые.

Управление может быть статическим, динамическим и двухступенчатым.

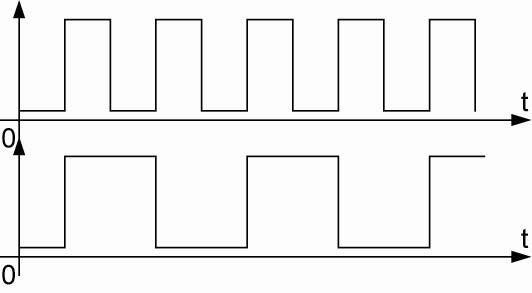

Временная диаграмма

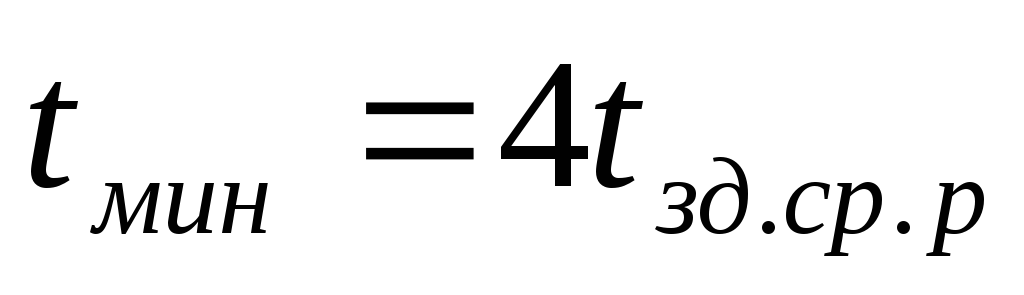

Минимальный интервал времени между

двумя тактовыми импульсами, при котором

Тг работает без сбоев

Соответственно максимальная частота

переключателей

Dv – триггеры

DV– триггер представляет собой модификациюD– триггера. Их логические функции определяются наличием дополнительного разрешающего входаV, играющего роль разрешающего по отношению ко входуD.

П риV= 1 триггер работает какD– триггер

риV= 1 триггер работает какD– триггер

При V= 0 — переходит в режим хранения информации независимо от состояния входаD.

Управление функционированием DV– триггера имеет следующий вид:

Наличие V– входа расширяет функциональные возможностиD– триггера, позволяя в нужный момент времени сохранять информацию на выходах в течение нужного числа тактов.

Поскольку вход V– подготавливающий, сигналV= 1должен перекрывать по длительности оба фронта тактового импульса.

Наиболее удобны эти триггеры в

быстродействующих схемах, поскольку

передача информации происходит по

одному входу, т. е.

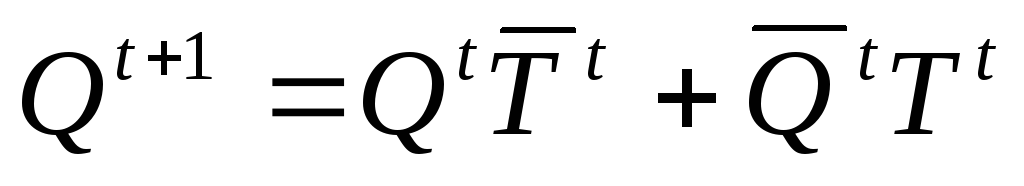

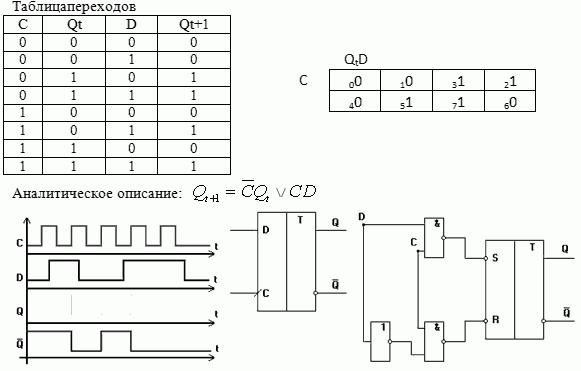

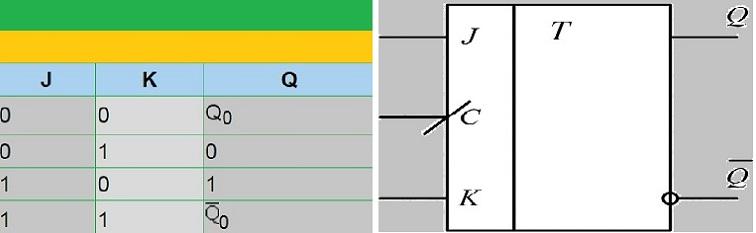

T – триггер (счетный триггер)

T– триггер имеет один информационныйT– вход (toggle- чека) и отличается простотой действия.

Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или отрицательном) перепаде напряжения на входе.

В сериях выпускаемых микросхем таких триггеров, как правило, нет. Но они могут быть созданы на базе других триггеров.

На основе D– триггера Временная диаграмма

T– триггер – единственный вид триггера, текущее состояние которого определяется не информацией на входах, а состояние в предыдущем такте.

Уравнение T– триггер имеет вид:

Как видно из временной диаграммы частота на выходе T– триггер в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

Состояние счетных триггеров Сокращенная таблица состояний

динамическим управлением.

Принцип работы и таблица истинности D-триггеров: синхронных и двухступенчатых

В цифровых схемах d триггер выполняет функции единичного запоминающего устройства. Такие решения применяют для оперативного и длительного хранения информации. Их используют в блоках фильтрации сигналов. Представленные ниже сведения помогут ознакомиться не только с теорией, но и с методикой решения отдельных практических задач.

Рабочая схема триггера

Что такое Д триггер

Триггерами называют устройства, способные длительное время поддерживать определенное состояние на выходе. Как правило, они контролируют соответствующие уровни напряжения. Изменения происходят при определенной комбинации входных сигналов.

Простейшие устройства этой категории создают по схеме RS. Они запоминают состояние сигнала, поданного на один из входов. Чтобы устранить процесс сбоев, который вызывают паразитные колебания при переходе сигнала из ноля в единицу и обратно, применяют синхронизацию. Этим дополнительным сигналом устанавливают точное время (интервал) для возможных изменений.

В обозначении Д триггера отмечена главная особенность. Буквой «Д» (D лат.) маркируют вход, на который подают информационный сигнал. Другой («С») используют для синхронизации записи. Отсутствие активности на нем исключает изменение базового состояния. Такое решение, в отличие от RS, позволяет изменять состояние с применением только одного источника данных.

Устройство Д триггера

Проще всего представить функциональность на основе элементарных логических элементов. Второе название триггеров данной категории – «защелка», наглядно поясняет основные принципы работы.

Схема Д триггера

На рисунке, кроме основных, отмечены входы. Вне зависимости от сигналов синхронизации, с их помощью переводят изделие в нулевое или единичное состояние. Таким образом реализован принцип приоритетности, так как активация S и R блокирует входные вентили C.

Виды D триггера

Типовые решения с применением представленных логических элементов рассмотрены ниже. Допустимы другие комбинации для удвоения частоты и решения других задач.

D-триггер синхронный

Рассмотрим на упрощенном примере основы функционирования. Для этого уберем сервисные входы. Диаграммы демонстрируют изменение сигналов при разных комбинациях управления. В таблице показаны состояния для записи единиц и нулей, а также в режиме хранения.

D триггер: таблица истинности, схема, временные графики

Если подать на С единицу (ноль), изменение на D сопровождается появлением аналогичного сигнала на выходе Q. Следует обратить внимание на временные задержки. Пока синхронизация отсутствует, изделие не срабатывает, вне зависимости от состояния информационного входа.

В соответствующих режимах:

- Запоминается предыдущее состояние на выходе;

- Обеспечивается «прозрачность» – практически мгновенное повторение входных значений;

- Фиксируется выходной сигнал («защелкивается»), когда сигнала С нет.

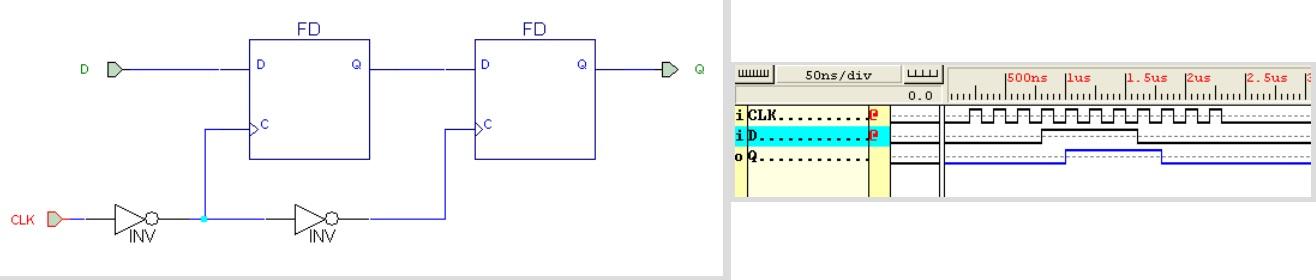

D-триггер двухступенчатый

В таких схемах объединяют последовательно два триггера. Первый – настраивают по увеличению входного сигнала. Второй – по спаду. Как видно на рисунке, состояние изменяется не одновременно с появлением новой информации, а с определенной временной задержкой, длительность которой равна одному полному рабочему циклу сигнала синхронизации.

Схема и временная диаграмма двухступенчатого триггера

Принцип работы

Во всех схемах имеет значение длительность рабочих реакций, которая определяет время записи (стирания). Определенное значение имеет помехоустойчивость. В следующих разделах рабочие процессы рассмотрены подробно.

Элементы с управлением по уровню

В этом варианте изменение состояния происходит только при высоком уровне синхронизирующего сигнала. При соответствующем положении устройство копирует изменения на входе с небольшой технологической задержкой. Если на С – ноль, реакция на выходе отсутствует.

Временная диаграмма для управления триггером по уровню

Элементы с управлением по фронту

В соответствии с названием, здесь реализована схема управления по фронту (переднему и заднему). С помощью временной диаграммы можно рассмотреть рабочие циклы внимательно.

Изменение состояния при разных информационных (управляющих) сигналах

Допустим, что для управления выбран передний фронт. При С=0 состояние триггера не изменяется, вне зависимости от информационных сигналов, – одновременно с прохождением переднего фронта записывается аналогичное уровню D. В данном примере – единица. Следующие изменения происходят по такому же алгоритму.

Чтобы расширить базовую функциональность, устройство дополняют представленными выше сервисными входами (R и S). С их помощью состояние устанавливают произвольным образом (1 или 0) в любой нужный момент. Разумеется, для выполнения таких действий понадобятся дополнительные элементы управления.

К сведению. В этом варианте не имеет значения длительность управляющего сигнала. Для функционирования схемы его можно подать с применением инвертора в противофазе на два триггера Д типа, соединенные последовательно. Такое решение будет сопровождаться изменением состояния по заднему фронту (спаду).

Схема реализации d-триггера

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

Схема реализации триггера на транзисторах

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.

Условные обозначения Д триггеров на схеме

Стандарты:

- Т – триггер;

- D – информационный вход;

- C (треугольник) – синхронизация;

- S и R – входы для принудительного перевода состояния в ноль или единицу.

Условно графическое обозначение (УГО) двух последовательно подключенных триггеров

При работе с цифровыми схемами, кроме основных логических функций, надо учитывать базовые принципы радиотехники. Для поддержания хорошей работоспособности необходимо качественное электропитание. Особое внимание уделяют минимизации паразитных переходных процессов, защите от внешних неблагоприятных воздействий. Уменьшает количество сбоев эффективная защита от электромагнитных помех.

Видео

D-триггер: принцип работы, таблица истинности

Триггер – элементарное устройство, представляющее собой цифровой автомат с двумя состояниями устойчивости, одному из которых присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды устройств: T-триггер, D-триггер, JK-триггер, RS-триггеры. Естественно, здесь перечислены наиболее распространенные варианты, но кроме них существуют автоматические устройства и других типов.

В этой статье мы более подробно рассмотрим D-триггер. Упомянутый автомат имеет один-единственный информационный (D) вход, таким образом, он предназначен для реализации функции временной задержки.

Принцип работы

Характеристическое уравнение Q(t+1)=Dt описывает функционирование такого типа устройства, как D-триггер. Таблица истинности (таблица переходов) для данного цифрового автомата приведена ниже.

Как видим, в первой и четвертой строке значения сигналов Q в моменты времени t и t+1 совпадают. То есть D-триггер является элементом задержки сигнала. В результате рассматриваемые приборы асинхронного типа не нашли своего применения, так как на выходе будет повторяться входной сигнал с небольшой временной задержкой.

D-триггер синхронного типа строится из одноуровневых (одноступенчатых) и двухуровневых (двухступенчатых) RS-устройств такого же типа. Упомянутые автоматы функционируют согласно таблице переходов.

Одноступенчатый D-триггер может быть выполнен из одноуровневого синхронного RS-устройства и одного элемента И-НЕ1, который соединяет в единый информационный (D) вход оба инверсных входа D-триггера.

При поступлении логического нуля на синхронизирующий вход автомат типа RS заблокирован уровнем логической единицы с выходов элементов И-НЕ2 и И-НЕ3. При смене сигнала синхронизации уровень, поданный на информационный вход, создаст логический нуль либо на входе S (при D=1), либо на входе R (при D=0) асинхронного триггера Т. Он переключится в состояние, соответствующее логическому уровню D. Одноступенчатый триггер D-типа задерживает распространение входного на время паузы между синхронизирующими сигналами.

D-триггер с динамическим управлением. Описание работы, функциональная схема

Автоматическое устройство такого вида конструируется из трех RS-триггеров асинхронного типа. Они построены на элементах И-НЕ, при этом два из них выполняют коммутирующую функцию, а третий является выходным. Выходные сигналы коммутирующих триггеров предназначены для управления выходным триггером.

При уровне сигнала С, равного логическому нулю, на входы выходного триггера поступает нейтральная для него комбинация сигналов, и он переключается в режим хранения. При изменении информационного сигнала коммутирующие триггеры переходят в режим ожидания, и как только поступает сигнал логической единице на разрешающий вход триггера С, выходной автомат устанавливается в новое состояние, которое соответствует информационному сигналу на D-входе в предыдущем такте.

В случае если изменение уровня информационного сигнала пройдет в период установки выходного триггера, тогда коммутирующие устройства сигнал не пропустят. Получается, что цель коммутирующих триггеров заключается в приеме информационных сигналов, передаче их на вход выходного прибора в момент перемены сигнала на управляющем входе С от логического нуля к логической единице и самоблокировки от воздействия сигнала на информационном входе.

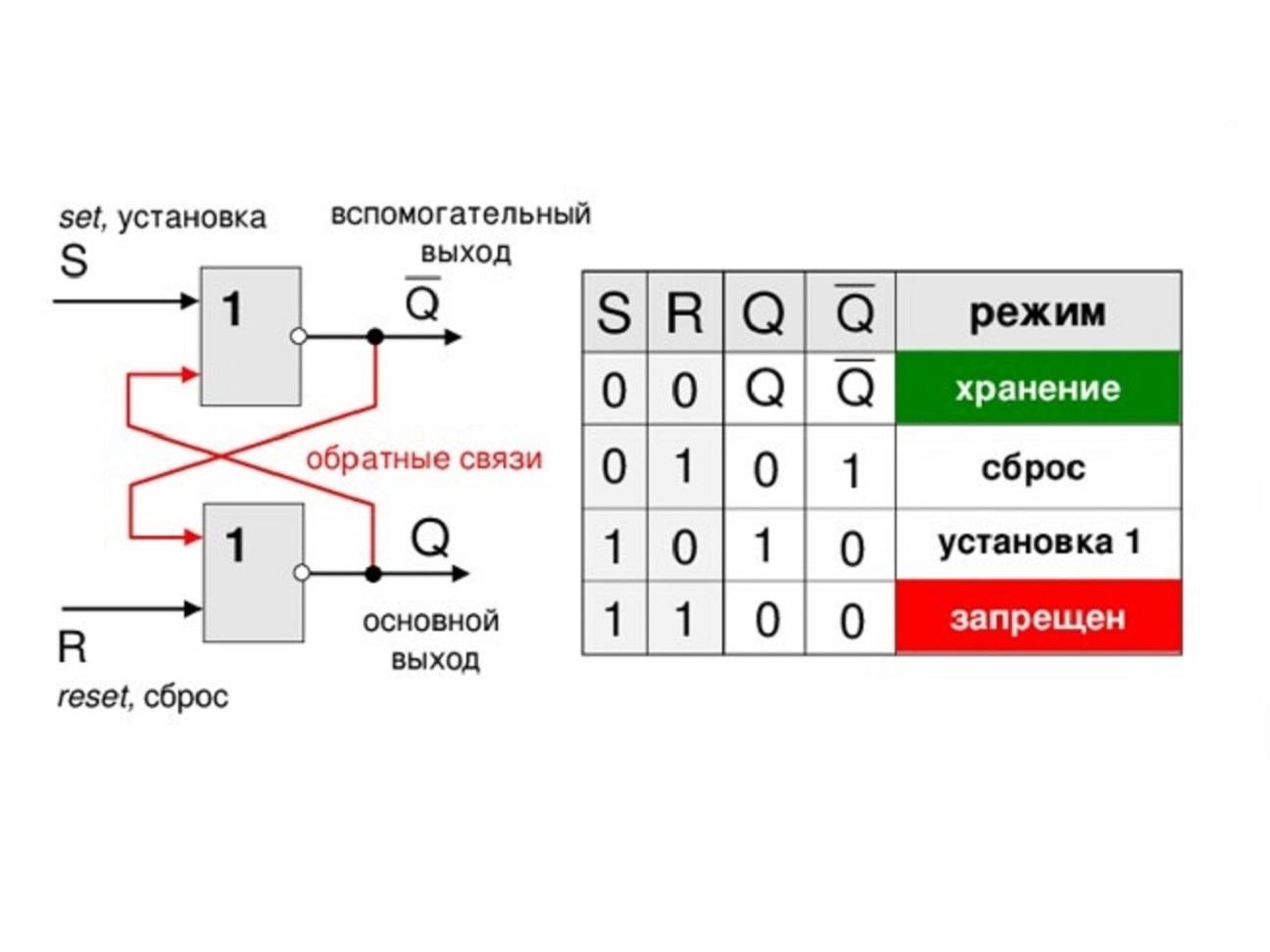

Логическая схема и принцип работы RS триггера: таблица истинности

Триггер в переводе с английского – защёлка. Это электронный модуль, способный длительно находиться в одном устойчивом состоянии и менять его под действием внешнего сигнала. Это цифровая автоматическая ячейка, которая умеет запоминать и хранить двоичный код данных, размером в 1 бит. То, как работает триггер, зависит от его структуры и назначения. В основе всякой подобной ячейки располагается восстанавливающее кольцо из пары инверторов. Устройство содержит прямой и инверсный выходы.

Общая структурная схема защёлки

Место триггеров в цифровой схемотехнике

Сам рс триггер, как один из структурных элементов в схемотехнике, не содержит в своём составе какого-то отдельного блока или устройства памяти. Он является простейшей логической ячейкой, которая запоминает своё предыдущее и настоящее состояния на входах и выходах. Память является результатом алгоритма работы переключателя. Выходы устройства находятся в состоянии либо логического нуля, либо единицы. При их изменении схема «защёлкивает» это положение и запоминает до тех пор, пока устройство управления вводом, выполненное из логических элементов, не даст команду об изменении состояния.

Классификация

Прежде, чем рассматривать работу триггеров, необходимо разобраться в обозначениях входов и выходов подобных устройств.

Входа (порты) у триггера бывают:

- R (reset) – устанавливает положение 0, раздельный порт;

- S (set) – устанавливает положение 1, раздельный порт;

- J – порт универсальных защёлок, устанавливает статус 1;

- K – порт универсальных защёлок, устанавливает статус 0;

- T – счётный порт, меняет положение защёлки.

Информация. Высокий уровень потенциала на входе или выходе равняется логической единице, низкий – логическому нулю. У микросхем марки ТТЛ логической единицей считается потенциал от 2,4…5В, логическим нулём – 0…0,4 В при напряжении питания 5 В. Для логических сборок других серий диапазоны потенциалов могут отличаться.

У защёлки в наличии два выходных порта:

- Q – прямой;

- Q¯ – инверсный.

При единице на прямом (Q = 0) «защёлка» находится в состоянии «1». В случае низкого потенциала на выходе (Q = 1) статус защёлки – «0».

У инверсного выхода все наоборот. При нуле у выхода Q¯ переключатель находится в состоянии единицы. Инверсия положения нужна для внедрения различных схематических решений.

Внимание! Типы портов определяют названия электронных переключателей, так, имея порта R и S, он носит имя RS-триггер.

Последовательностное логическое устройство (ПЛУ), которым является «защёлка», – это своеобразный блок для постройки различных комбинаций в схемах логических цепей. Бистабильное состояние RS-защёлки помогает компоновать такие логические схемы, как счётчики, регистры хранения, устройства памяти или регистры сдвига. Независимо от метода устройства логических связей, основные виды электронных переключателей можно разделить по способу ввода данных:

- синхронный тип;

- асинхронный тип;

- комбинированный.

Всё зависит от того, как посылается команда управления на изменение состояния «защёлки».

Синхронные устройства

Для того чтобы rs триггер не менял своего положения от сочетания задержанных командных импульсов на его портах, применяют синхронизирующую команду. Это тактовый импульс, который подаётся на синхронизирующий порт. Сменившиеся сигналы на входах такой «защёлки» не смогут изменить состояния на выходе, пока не придёт тактовый (синхронизирующий) импульс. Эти импульсы вырабатывают тактовые генераторы. Длина тактовых сигналов намного меньше их периода. Импульсы определяют частоту замены информации, привязав её к дискретным временным периодам – tl, t2,…,tn-1,tn, tn+l. Это позволяет синхронизировать процессы работы отдельных узлов оборудования в едином ритме.

Действие схемы следующее:

- если на порту С присутствует ноль, статус триггера не меняется, поскольку информация с портов S и R не передаётся на защёлку;

- если на порту С появляется логическая единица, то переключатель принимает команды с S и R входов и меняет своё положение.

У таких схем повышенная помехоустойчивость, что выгодно отличает их от асинхронных устройств, последние могут перевернуться не только от сигнала, но и от помехи. Синхронная структура применяется в технике, связанной с преобразованием или обработкой цифровых данных.

Синхронный RS – триггер, схема и графическое обозначение

Важно! При применении RS-защёлки с инверсными входами необходимо заменить элементы схемы «И» на элементы «И – НЕ».

Асинхронные модели

Устройство, меняющее своё состояние немедленно при изменении команды на логических портах, называют асинхронным триггером. Он имеет в своём составе только порты: R (сброс) и S (установка). Ограничения для пользования подобными схемами связано с соперничеством между сигналами, которые при попадании на разные входы RS-триггера движутся разными путями, как бы состязаясь между собой. При этом возникают временные задержки и сдвиги, вызванные разными причинами: изменения температуры, долгий срок службы и прочее. Такая «гонка» вызывает частые ошибочные переворачивания ячейки.

Тактовая синхронизация в данном случае не эффективна, потому асинхронные ячейки применяются в качестве асинхронных счётчиков, различных ключей, делителей частоты и им подобных схемных решений.

Асинхронный RS-триггер, структурная схема

Комбинированные схемы

Модуль, состоящий из комбинации нескольких ячеек, называется комбинированным триггером. Возможны комбинации от двух и более функциональных ячеек.

Таблица комбинаций двух типов ячеек памяти

| Тип устройства | RS | R | S | E | JK | T | D | DV |

|---|---|---|---|---|---|---|---|---|

| RS | Х | Х | Х | Х | Х | Х | Х | |

| R | Х | Х | Х | Х | Х | Х | ||

| S | Х | Х | Х | Х | Х | |||

| E | Х | Х | Х | Х | ||||

| JK | Х | Х | Х | |||||

| T | Х | Х | ||||||

| D | Х | |||||||

| DV |

Типы триггеровЗдесь Х – объединение двух типов возможно.

Подразделение этих устройств по типам можно рассмотреть по таблицам переходов состояния.

Выделяются следующие типы ячеек памяти состояния:

- rs-защёлка – асинхронная и синхронная;

- jk-защёлка;

- d-защёлка;

- t-защёлка.

Последний элемент списка – устройство составное, выполняется из синхронной rs-ячейки памяти.

RS-триггеры

Рассматривают два вида подобных ячеек: асинхронная и синхронная защёлка. При подробном изучении видна значительная разница в работе и сфере применения.

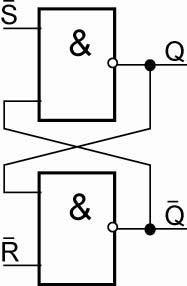

RS-триггер асинхронный

Самый простой вид защёлки, редко применяется как самостоятельное устройство, является ячейкой для построения более сложных блоков. Построены асинхронные соты на элементах:

- 2 ИЛИ – НЕ, триггерная сота с прямыми портами;

- 2 И-НЕ, триггерная сота с инверсными портами.

Фиксированные положения триггеру обеспечивают обратные связи. Это подключение выхода одного к любому входному порту другого логического элемента.

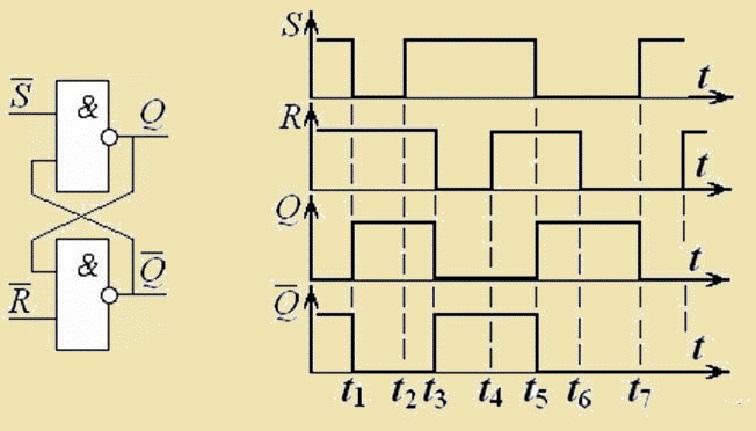

RS-триггер синхронный

Основа регистров, делителей частоты и различных счётчиков – триггерная сота памяти. В подобных устройствах зафиксированную раньше информацию нужно передать на выход и записать в следующую ячейку по сигналу тактового импульса. Импульс подаётся на С-порт (статический или динамический).

К сведению. Статический С-вход выполняет синхронизацию по изменению уровня потенциала сигнала, динамический С-вход синхронизирует изменение состояния не по уровню, а моменту его изменения. Переключение на динамическом С-входе может осуществляться по фронту импульса (прямой) или по его срезу (инверсный).

Состоящие из пары синхронных rs-триггеров и инвертора двухступенчатые RS-триггеры управляются полным (задействованы и фронт, и срез) динамическим тактовым импульсом. Такие ячейки памяти называются master-slave (мастер-помощник).

JK-триггер

Отличительной чертой этого типа «защёлки» является отсутствие запрещённого сочетания сигналов на портах. При J = K = 1 положение защёлки переворачивается на обратное, по сравнению к текущим Q0.

JK-переключатель отличается от RS-ячейки памяти только одним: если на J и K подаётся «1», то он меняет своё пребывание на противоположное положение. Происходит инверсия, причём у этой ячейки памяти отсутствуют запрещённые состояния главных портов.

Внимание! Если провести аналогию обозначения входов, то J и K, соответственно, аналогичны входам S и R у RS-триггера. Практическое применение нашли только синхронные jk-триггеры с динамической синхронизацией.

Таблица истинности и обозначение jk-триггера

Что такое RS триггер

Это сота памяти, способная находиться в одном из стабильных положений: «0» или «1». Переворачиваться, т.е. менять их, она может под воздействием тактовых сигнальных импульсов. Ни записать, ни стереть хранимый бит элементарный элемент, собранный на двух инверторах, не может. Принцип работы rs триггеров, выполненных на двух компонентах 2И-НЕ, позволяет это сделать.

Таблица истинности

Таблица переходов состояний (таблица истинности) поясняет работу RS-триггера на элементах «И-НЕ». На ней Q 0 – текущий статус ячейки до попадания активного сигнала на порт. Когда логическая единица отсутствует на входах R и S, «защёлка» сохраняет положение Q 0. Активный импульс R = 1 перекидывает защёлку в положение 0, импульс S = 1 – в положение 1. Звездочка в таблице указывает на положение при запрещенном сочетании приходящих сигналов.

Таблица истинности RS-триггера

Такой тип имеет раздельное назначение логических состояний нуля и единицы по информационным портам.

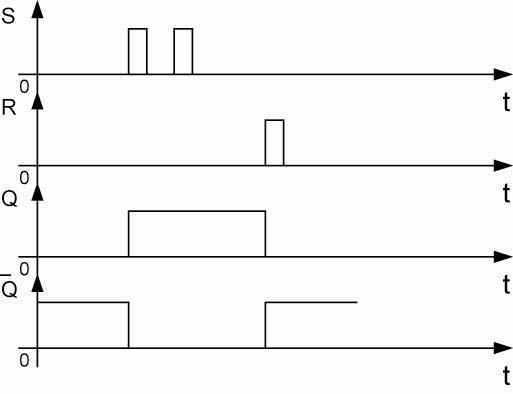

Временные диаграммы

Кроме таблиц истинности, помогает разобраться в работе ячейки битовой памяти временная диаграмма. При этом на графике при изучении импульсов рассматривают следующие параметры:

- длительность импульса – временной интервал от фронта до спада;

- период – интервал от фронта предыдущего импульса до фронта последующего;

- скважность – отношение периода импульса к его длительности.

Диаграмма графически отображает сигнальные импульсы на входах и выходах в одних и тех же временных точках.

Временная диаграмма RS-триггера

Классификация последовательных схем

Последовательные схемы допускается классифицировать по следующим показателям:

- одноступенчатые защёлки, в которых содержатся элемент памяти и устройство управления, их маркируют буквой Т;

- двухступенчатые ячейки: статического и динамического управления, используются для защиты от гонок сигналов, обозначаются буквами ТТ;

- переключатели, имеющие сложную логику: одно,- и двухступенчатые соты.

Одноступенчатые ячейки применяются в качестве первых ступеней в переключателях ТТ с динамической схемой управления, имеют такое же управление. При самостоятельном использовании управление в большинстве своём статическое.

Двухступенчатые устройства имеют как статическое, так и динамическое управление.

Состояние «Установлен»

RS-переключатель в этом состоянии имеет установленную цепь с Q, равным нулю, и Q¯, равным единице, и независим от управляемого сигнала. При этом на R присутствует ноль, на S – логическая единица.

Состояние «Сброшен»

Это тоже неизменная ситуация. Для её организации необходимо выставить исходные условия. На R подаётся «1», на S – «0». При этом выход Q должен иметь «1», Q¯ – значение «0». Обратные связи обеспечивают и фиксируют независимое от последующих значений на входах значение.

Диаграмма переключения RS-триггера

Состояния переключения, установки и сброса можно просмотреть на временной диаграмме. На ней отмечено, что переключатель переходит в положение установки при появлении нуля на его S-входе и единице на входе R, фиксированный сброс при подаче нуля на порт R и единицы на S.

Диаграмма переключения защёлки

Внимание! Если ноль подать на два входа (R и S) синхронно, то переключатель из-за неопределённого состояния на вводах может перевернуться в любое непредсказуемое положение, при этом произойдёт повреждение данных.

Модификация схемы триггера

Чтобы смена состояний происходила на подъёме уровня сигнала у rs-триггера, необходимо на его выходах иметь:

- при установке – Q = 1, а Q¯ = 0;

- при сбросе – Q = 0, а Q¯ = 1.

Чтобы это организовать, поступающие сигналы защёлки инвертируют. В результате этого изменение состояния выполняется при поступлении положительных сигналов. При модификации добавляются в качестве инверторов 2 элемента И-НЕ.

Модификация схемы триггера

Как синхронизировать работу триггера

Подключение двухпортового элемента «И» в последовательную цепь схемы триггера с каждым из входов позволит менять его статус, независимо от состояний на R,- или S-входах. Новый порт С получится при объединении двух портов ячеек «И». В результате доработки статус на выходах Q и Q¯ будет меняться только тогда, когда на С будет приходить высокий потенциал. Предусмотрено подключение генераторов тактовых импульсов на этот новый вход.

Синхронизация триггера

Регистры на триггерах

Так как один переключатель является однобитовой ячейкой памяти, то, чтобы сохранить несколько бит, нужно увеличить количество единичных хранилищ. Цепочка из таких ячеек носит названия регистра. Регистр позволяет временно хранить цифровые данные двоичных разрядов. Количество разрядов зависит от количества однобитовых ячеек.

Схема 4-х разрядного регистра сдвига на триггерах

Использование элементарных электронных цифровых устройств – триггеров, позволяет составлять сложные схемы управления логическими устройствами. Одна элементарная защёлка памяти своим бистабильным состоянием помогает осуществлять самые сложные схемные решения.

Видео

D-триггер. Принцип работы и обозначение на схемах.

Принцип работы и обозначение D-триггера

Возможно, вы уже познакомились с RS-триггером и JK-триггером на страницах сайта Go-radio.ru, но разговор о триггерах был бы неполным без упоминания D-триггера. D-триггер (англ. Delay-задержка) имеет свойственные всем триггерам входы: S (установка), R (сброс), С — вход синхронизации и D-вход. Ещё D-триггер называют – триггер с динамическим управлением. Работа D-триггера аналогична работе JK-триггера с небольшими отличиями.

Особенностью триггера является то, что при подаче на вход D низкого уровня (логического 0) и по спаду импульса на входе С, триггер сбрасывается в нулевое состояние. Если на входе D высокий уровень (логическая 1), то по спаду импульса на входе С триггер устанавливается в единицу.

Что такое спад импульса? Объяснить это лучше наглядно, например, с помощью рисунка. Вот взгляните.

Напомним, что вход C является входом синхронизации или, по-другому, входом тактирования. Он нужен для того, чтобы упорядочить работу множества отдельных микросхем в одной общей схеме.

На принципиальных схемах D-триггер обозначается следующим образом.

Бывает, что изображение на схеме несколько отличается. Но, несмотря на это, на условном обозначении D-триггера всегда присутствует указание входа «D«.

В cерии логических микросхем К561, выполненных по технологии КМОП, есть наборы D-триггеров. Например, микросхема К561ТМ2 содержит два D-триггера в одном корпусе. А в составе микросхемы К561ТМ3 уже четыре D-триггера. Для построения несложных счётчиков и делителей частоты эти микросхемы гораздо удобнее.

Вот так обозначается на схемах микросхема К561ТМ2 (К176ТМ2, К564ТМ2). Импортный аналог микросхемы К561ТМ2 — CD4013, HEF4013.

Как видим, в составе этой микросхемы два D-триггера. Для подключения питания к этой микросхеме используются вывод 14 (это плюс «+», VDD) и вывод 7 (это минус «-«, GND).

Для того чтобы получить из D-триггера делитель частоты на два достаточно соединить инверсный выход со входом D. То есть соединяются выводы 2 и 5 (12 и 9), а импульсы подаются на вход С.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Триггеры

Триггер– это устройство последовательностного типа с двумя устойчивыми состояниями равновесия, предназначенного для записи и хранения информации.

Основные свойства триггеров:

Способность длительно оставаться в одном из двух возможный устойчивых состояний и скачком чередовать их под воздействием выходных сигналов.

способность запоминать информацию – т.е. оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Если принять одно из состояний Тг за “1”, а другой за “0” можно считать, что Тг хранит (помнит) один разряд числа, записанного в двоичном коде.

По способу записи информации триггеры делят на:

асинхронные;

синхронизируемые (тактируемые).

В асинхронныхтриггерах информация может записываться непрерывно и определяться информационными сигналами, действующими на входах в данный момент времени.

В синхронныхтриггерах информация записывается в триггер только в момент действия, так называемого синхронизующего сигнала. По мимо информационных входов синхронизуемые триггеры имеют тактовый вход (вход синхронизации). Как травило Тг имеет два выхода: прямойQг и инверсныйQi.

В цифровой технике приняты следующие обозначения триггера:

S(set) – раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом выходеQ).

R(reset) – раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом выходеQ).

D(data) – информационный вход (на него подается информация, предназначенная для занесения в Тг).

C– вход синхронизации.

T– счетный вход.

V– вход, разрешающий прием информации.

J– вход установкиJKтриггера в состояние “1”.

K– вход установкиJKтриггера в состояние “0”.

Входы VиCотносятся к управляющим входам, остальные к информационным.

К триггерам относятся различные виды устройств, различающиеся между собой по выполняемым функциям схемному исполнению, способам управления, электрическим и конструктивным параметрам.

Асинхронный rs – триггер

В зависимости от логической структуры различают RS– триггеры с прямыми и инверсными входами.

Триггеры такого типа построены на 2 логических элементах: ИЛИ – НЕ — триггер с прямыми входами (рис. 1).

И – НЕ — триггер с инверсными входами (рис. 2).

Выход каждого из элементов подключен к одному из входов другого элемента, т. е. Элементы охвачены перекрестной положительной обратной связью.

RS– триггер обладает двумя устойчивыми состояниями за счет связи выхода каждого элемента с одним из входов другого.

Рассмотрим таблицы истинности каждого из триггеров.

Обозначим  – уровни, которые были на входах Тг до

подачи на его входы так называемых

активных уровней.

– уровни, которые были на входах Тг до

подачи на его входы так называемых

активных уровней.

Активными называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независимо от логических уровней, действующих на основных входах).

Для элементов ИЛИ – НЕ – активный уровень “1”.

Для элементов И – НЕ – активный уровень “0”.

Уровни , подача которых на один из входов не приводит к изменению логического уровня на выходе элемента называютпассивными.

Уровни  и

и обозначают логические уровни на выходах

триггера после подачи информации на их

входы.

обозначают логические уровни на выходах

триггера после подачи информации на их

входы.

RS – триггер

S | R |

|

|

|

|

0 | 1 | 0 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 1 | 0 |

0 | 0 | 0 | 1 | 0 | 1 |

1 | 1 | 0 | 1 | н/о | н/о |

0 | 1 | 1 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 1 | 0 |

0 | 0 | 1 | 0 | 1 | 0 |

1 | 1 | 1 | 0 | н/о | н/о |

–

триггер

–

триггер

|

|

|

|

|

|

0 | 1 | 0 | 1 | 1 | 0 |

1 | 0 | 0 | 1 | 0 | 1 |

0 | 0 | 0 | 1 | н/о | н/о |

1 | 1 | 0 | 1 | 0 | 1 |

0 | 1 | 1 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 | 1 |

0 | 0 | 1 | 0 | н/о | н/о |

1 | 1 | 1 | 0 | 1 | 0 |

Для RS– триггера

Режим S= 1;R= 0 – режим записи 1.

Режим S= 0;R= 0 – режим хранения.

Режим S= 0;R= 1 – запрещающий режим.

Для  – триггера

– триггера

Режим  = 0;

= 0; = 1 – режим записи.

= 1 – режим записи.

Режим  = 1;

= 1; = 1 – режим хранения.

= 1 – режим хранения.

Режим  = 0;

= 0; = 0 – запрещающий режим.

= 0 – запрещающий режим.

При R=S=

1 ( =

= =

0) состояние триггера будет неопределенным,

так как во время действия информационных

сигналов логические уровни на выходах

триггера одинаковы (

=

0) состояние триггера будет неопределенным,

так как во время действия информационных

сигналов логические уровни на выходах

триггера одинаковы ( =

= =

0), а после окончания их действия триггер

может равномерно принять любое из

устойчивых состояний. Поэтому такая

комбинация является запрещенной.RS– триггеры самостоятельно практически

не используются в следствие низкой

помехоустойчивости.

=

0), а после окончания их действия триггер

может равномерно принять любое из

устойчивых состояний. Поэтому такая

комбинация является запрещенной.RS– триггеры самостоятельно практически

не используются в следствие низкой

помехоустойчивости.

Временная диаграмма действия RS– триггера

Таблица истинности RS– триггера (минимизированная форма)

Такт t | Такт t+ 1 | |

|

|

|

0 | 0 |

|

0 | 1 | 1 |

1 | 0 | 0 |

1 | 1 | н/о |

Как самостоятельные изделия асинхронные RS– триггеры находят применение в роли ключей, компилятора, распределителей и т. п., формирователей импульсов от механических контактов.

Примером RS– триггера промышленного производства является ИС 561ТР2.

В одном корпусе ИС содержатся четыре независимых одинаковых триггера.

Х арактерная

особенность— наличие третьего

состояния при котором выходы триггеров

отключаются от выходов в микросхему.

арактерная

особенность— наличие третьего

состояния при котором выходы триггеров

отключаются от выходов в микросхему.

Логическая структура Условное изображение

одного триггера микросхемы

Выходной инвертор служит буфером между T2 и последовательным каскадом.

V– общий разрешающий вход (управляет всеми четырьмя ключами). ПриV= “1” ключи проводят информацию, а приV= “0” информация на выходах отсутствует.

Таблица истинности

|

| V | |

0 | 0 | 1 |

|

0 | 1 | 1 | 0 |

1 | x | 1 | 1 |

x | x | 0 | z |

В некоторых сериях RS– триггеры как самостоятельные изделия отсутствуют.

Такие триггеры легко собрат из обычных логических элементов. Кроме того в более сложных триггерах имеются побочные входы SaиRa, обладающие приоритетом, позволяющие в любой момент времени установить Тг в “1” или “0” независимо от состояния других входов.