НОУ ИНТУИТ | Лекция | Триггеры

Аннотация: В лекции рассказывается о триггерах различных типов, об алгоритмах их работы, параметрах, типовых схемах включения, а также о реализации на их основе некоторых часто встречающихся функций.

Триггеры и регистры являются простейшими представителями цифровых микросхем, имеющих внутреннюю память. Если выходные сигналы логических элементов и комбинационных микросхем однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Именно поэтому их применение позволяет строить гораздо более сложные и интеллектуальные цифровые устройства, чем в случае простейших микросхем без памяти. Микросхемы с внутренней памятью называются еще последовательными или последовательностными, в отличие от комбинационных микросхем.

Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания. Иначе говоря, их память относится к типу оперативной (в отличие от постоянной памяти и перепрограммируемой постоянной памяти, которым отключение питания не мешает сохранять информацию). После выключения питания и его последующего включения триггеры и регистры переходят в случайное состояние, то есть их выходные сигналы могут устанавливаться как в уровень логической единицы, так и в уровень логического нуля. Это необходимо учитывать при проектировании схем.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Именно поэтому триггеры и регистры иногда называют также

Триггер можно рассматривать как одноразрядную, а регистр — как многоразрядную ячейку памяти, которая состоит из нескольких триггеров, соединенных параллельно (обычный, параллельный регистр) или последовательно (сдвиговый регистр или, что то же самое, регистр сдвига).

Триггеры

Принцип работы и разновидности триггеров

В основе любого триггера (англ. — «тrigger» или «flip-flop») лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

Рис. 7.1. Схема триггерной ячейки

Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

| Входы | Выходы | ||

|---|---|---|---|

| -R | -S | Q | -Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | |

| 1 | 1 | Без изменения | |

| 0 | 0 | Не определено | |

В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

- RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый (а).

- JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко (б).

- D-триггер (обозначается ТМ) — наиболее распространенный тип триггера (в).

Примером RS-триггера является микросхема ТР2, в одном корпусе которой находятся четыре RS-триггера. Два триггера имеют по одному входу –R и –S, а два других триггера — по одному входу –R и по два входа –S1 и –S2, объединенных по функции И. Все триггеры имеют только по одному прямому выходу. RS-триггер практически ничем не отличается по своим функциям от триггерной ячейки, рассмотренной ранее (см. рис. 7.1). Отрицательный импульс на входе –R перебрасывает выход в нуль, а отрицательный импульс на входе –S (или на любом из входов –S1 и –S2) перебрасывает выход в единицу. Одновременные сигналы на входах –R и –S переводят выход в единицу, а после окончания импульсов триггер попадает случайным образом в одно из своих устойчивых состояний. Таблица истинности триггера ТР2 с двумя входами установки –S1 и –S2 представлена в табл. 7.2.

| Входы | Выходы | ||

|---|---|---|---|

| -R | -S | Q | -Q |

| 1 | 1 | 1 | Без изменения |

| 0 | 1 | 1 | |

| 0 | X | 1 | 1 |

| 1 | 1 | 0 | 0 |

| X | 0 | 0 | Не определен |

| X | 0 | Не определен | |

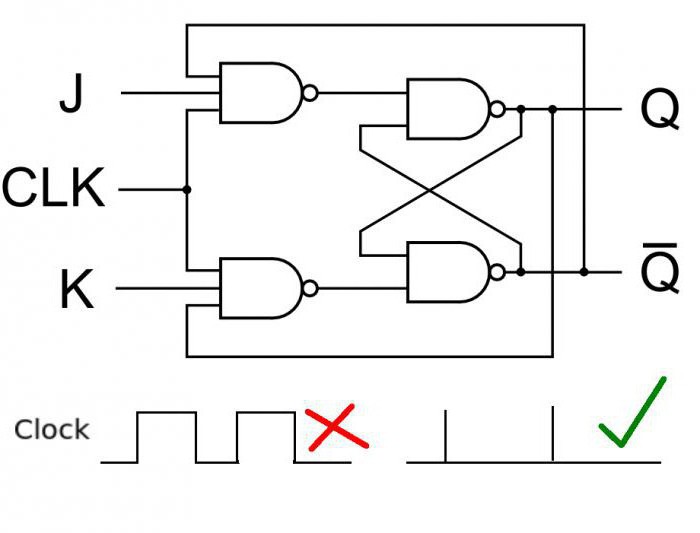

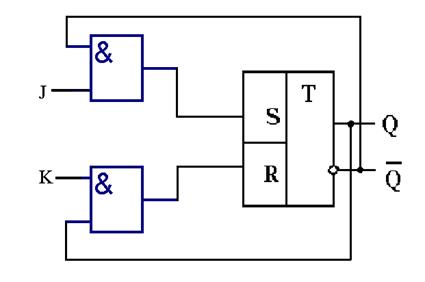

JK-триггер значительно сложнее по своей структуре, чем RS-триггер. Он относится к так называемым тактируемым триггерам, то есть он срабатывает по фронту тактового сигнала. Примером может служить показанная на рис. 7.2 микросхема ТВ9, имеющая в одном корпусе два JK-триггера со входами сброса и установки -R и -S. Входы -R и -S работают точно так же, как и в RS-триггере, то есть отрицательный импульс на входе -R устанавливает прямой выход в нуль, а инверсный — в единицу, а отрицательный импульс на входе -S устанавливает прямой выход в единицу, а инверсный — в нуль.

Однако состояние триггера может быть изменено не только этими сигналами, но и сигналами на двух информационных входах J и K и синхросигналом С. Переключение триггера в этом случае происходит по отрицательному фронту сигнала С (по переходу из единицы в нуль) в зависимости от состояний сигналов J и K. При единице на входе J и нуле на входе К по фронту сигнала С прямой выход устанавливается в единицу (обратный — в нуль). При нуле на входе J и единице на входе К по фронту сигнала С прямой выход устанавливается в нуль (обратный — в единицу). При единичных уровнях на обоих входах J и K по фронту сигнала С триггер меняет состояние своих выходов на противоположные (это называется счетным режимом).

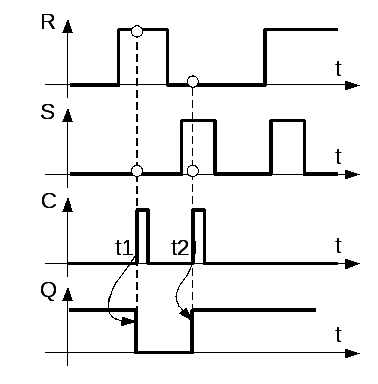

Рис. 7.3. Временная диаграмма работы JK-триггера ТВ9

Таблица истинности триггера ТВ9 представлена в табл. 7.3, а временная диаграмма работы — на рис. 7.3.

Триггеры. Основные теоретические положения. Классификация триггеров. Разработка триггеров, страница 2

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности RS-триггера Таблица 3

№ | R’ | S’ | Q n+1 | Q’ n+1 |

1 | 1 | 1 | Q n | Q’ n |

2 | 1 | 0 | 1 | 0 |

3 | 0 | 1 | 0 | 1 |

4 | 0 | 0 | – | – |

Анализ работы триггера (рисунки 4, а; 5, а) выполняется по следующему алгоритму:

— задать исходные значения выходов, например, Q n =0, Q’ n =1;

— выбирать значения входных сигналов R, S в соответствии с таблицей истинности;

— выполнить логические операции c заданными Q nи выбранными значениями R, S;

— новые (полученные) значения выходов Q n+1подать на входы и еще раз выполнить логические операции из-за возможности появления неустойчивых состояний.

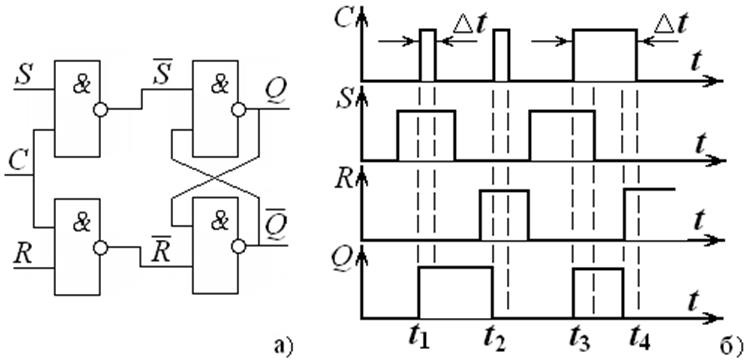

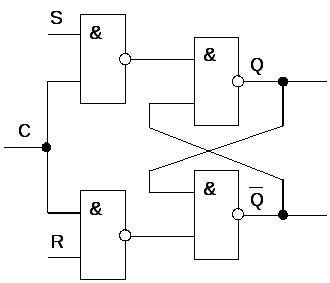

На основе RS-триггера получен ряд триггеров с различными функциональными возможностями. Например, синхронный RS-триггер (рис. 6), его таблица истинности табл. 4.

Рис. 6 Синхронный RS-триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности синхронного RS-триггера Таблица 4

№ | C | R | S | Q n+1 | Q’ n+1 |

1 | 1 | 0 | 0 | Q n | Q’ n |

2 | 1 | 0 | 1 | 1 | 0 |

3 | 1 | 1 | 0 | 0 | 1 |

4 | 1 | 1 | 1 | – | – |

5 | 0 | X | X | Q n | Q’ n |

X – любое значение переменной, которая не оказывает влияния на результат.

Считывание сигналов с информационных входов R, S происходит при наличии тактового сигнала C на интервале времени Dt, когда триггер работает как статическое устройство. Если в течение этого интервала по какой-либо причине происходит изменение входных сигналов R, S, то оно оказывает влияние на состояние выходов (интервал времени t3 – t4).

Чтобы сократить время считывания (приблизительно до пяти наносекунд) и таким образом повысить помехозащищенность триггера, тактовый вход C делают динамическим.

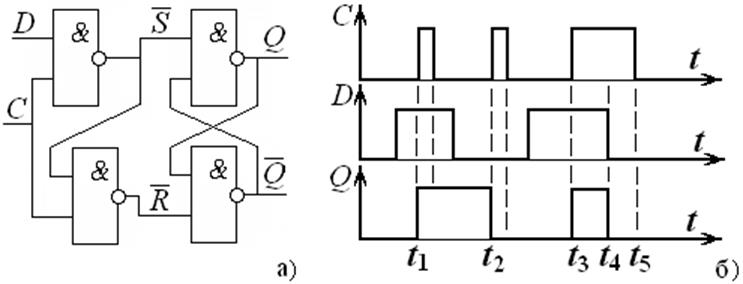

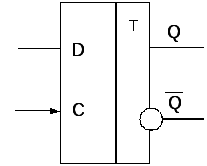

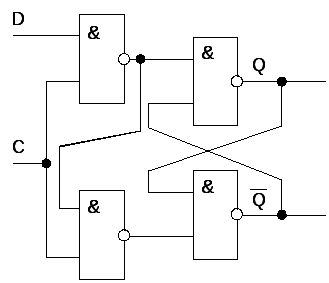

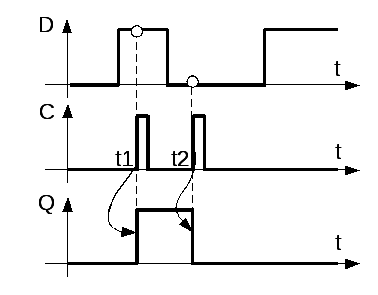

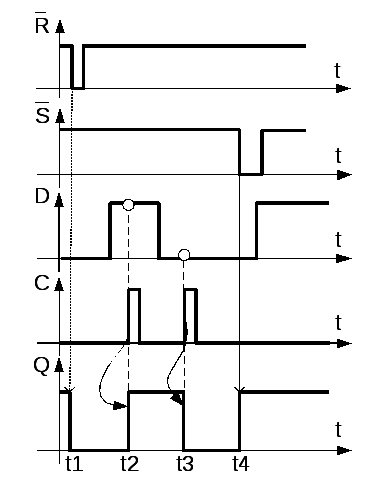

3 D-триггер

Схема D-триггера (рис. 7) имеет один информационный вход D и тактовый вход C, его таблица истинности табл. 5.

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

Рис. 7 D-триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности D-триггера Таблица 5

№ | C | D | Q n+1 |

1 | 1 | 0 | 0 |

2 | 1 | 1 | 1 |

3 | 0 | X | Q n |

На рисунке 7 представлен синхронный потенциальный D-триггер. Если при наличии тактового сигнала C (интервал t3 – t5), происходит изменение входного сигнала D (в момент времени t4), то это оказывает влияние на состояние выходов.

Чтобы повысить помехозащищенность триггера, тактовый вход C делают динамическим.

Если в схему D-триггера добавить разрешающий вход V, то такое устройство называется DV-триггером (рис. 8), таблица истинности табл. 6.

Таблица истинности DV-триггера Таблица 6 |

| ||||

№ | V | C | D | Q n+1 | |

1 | 1 | 1 | 0 | 0 | |

2 | 1 | 1 | 1 | 1 | |

3 | 0 | 0 | X | Q n | |

4 | 0 | 1 | X | Q n | |

5 | 1 | 0 | X | Q n | |

Рис. 8 DV-триггер

Данные триггеры применяются:

— для задержки прохождения сигнала до появления тактового импульса;

— в регистрах и счетчиках;

— в запоминающих устройствах, требующих большого числа простых ячеек памяти.

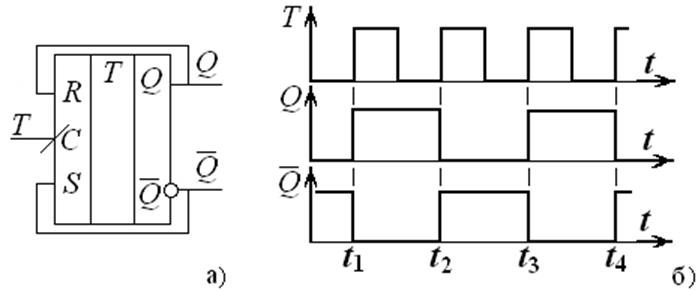

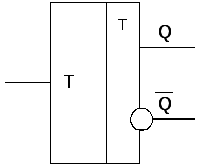

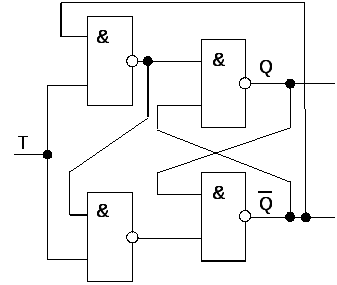

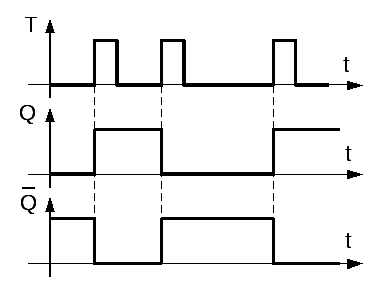

4 T-триггер

Схема T-триггера (рис. 9) имеет один информационный динамический вход T, его таблица истинности табл. 7. Если в схему T-триггера добавить разрешающий вход V, то такое устройство называется TV-триггером (по аналогии с DV-триггером).

Таблица истинности T-триггера Таблица 7

№ | T | Q n | Q n+1 |

1 | 1 | 0 | 1 |

2 | 1 | 1 | 0 |

Рис. 9 T-триггер

на основе RS-триггера:

а – принципиальная схема; б – временные диаграммы работы

Согласно временной диаграмме, в исходном состоянии Q =0, Q’ =1, на входе R =0, S=1. По переднему фронту тактового импульса T=1 сигналы с выходов запишутся в триггер и установятся новые значения Q =1, Q’ =0 (в момент времени t1). Очередной тактовый импульс запишет их в триггер и в момент времени t2 установятся значения Q =0, Q’ =1.

Данный триггер применяется:

— для изменения знака двоичного числа в арифметико-логическом устройстве;

— в счетчиках, делителях частоты;

— в регистрах.

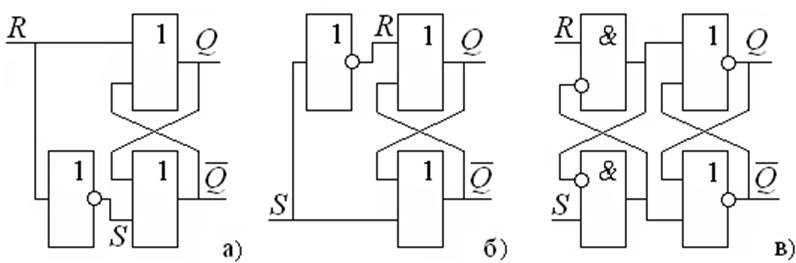

5 Приоритетные триггеры

Триггеры, у которых одни входы имеют преимущество над другими в установлении сигналов на выходе, называются приоритетными.

К таким устройствам относятся разновидности RS–триггера, а именно: R, S, E-триггеры (рис. 10, таблица истинности табл. 8). Последняя строка этой таблицы определяет приоритет соответствующего входа.

Таблица истинности RS -триггеров Таблица 8

R -триггер | S -триггер | E -триггер | ||||||||

R | S | Qn+1 | R | S | Qn+1 | R | S | Qn+1 | ||

0 | 0 | Q n | 0 | 0 | Q n | 0 | 0 | Q n | ||

0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | ||

1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | ||

1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | Q n | ||

Схема E-триггера устанавливает преимущество входного сигнала R или S, который появился на входе первым с помощью логической операции Импликация. Пришедший первым сигнал (логическая единица) инвертируется и устанавливает запрет на поступление сигнала на второй вход.

Рис. 10 Приоритетные триггеры на основе RS-триггера:

а – R-триггер; б – S-триггер; в – E-триггер

Пример E-триггер исключает зажигание сигналов светофора одинакового цвета для различных направлений движения транспорта.

ТРИГГЕРЫ НА МИКРОСХЕМАХ

Если мультивибратор это прибор с двумя неустойчивыми состояниями, который самопроизвольно переходит из одного состояния в другое, то триггер ему полностью противоположен. Это прибор с двумя устойчивыми состояниями и эти состояния он меняет только под внешнем воздействии. Благодаря этому свойству триггеры используются в запоминающих устройствах [1]. В данной работе предлагаются к повторению широко распространенные схемы триггеров, которые можно реализовать на одной логической микросхеме К155ЛА3. Питание подается на 14 выход микросхемы, общий провод 7. Питание осуществляется от стабилизированного источника питания напряжением 5 В.

Асинхронный RS-триггер

Самый простой тип триггера, который является основой для сборки остальных триггеров в данной лабораторной работе. Он собирается на паре логических элементов И-НЕ, хотя аналогично можно использовать ИЛИ-НЕ [2]

Как видно на электрической принципиальной схеме данное электронное устройство обладает симметрией. Если поменять местами входы S и R, одновременно с выходами Q и Q1, то по сути мы получим туже самую схему. Таким образом то где у триггера прямой выход, а где инверсный это по сути вопрос договора.

Для практической реализации схемы используются самодельные модули для изучения микросхем. При подаче питания триггер устанавливается в случайное состояние.

Используя данное устройство можно проследить за выполнением таблицы истинности асинхронного RS-триггер.

Таблица истинности асинхронного RS-триггера

В частности, можно увидеть, что данный триггер переключается просто от прикосновения к проводам и пронаблюдать запрещенное состояние.

Синхронный RS-триггер

Схема асинхронного RS-триггера проста, но за это приходится заплатить целым рядом недостатков: наличие запрещенного состояния, установка 0 и 1 по отдельным линиям отсутствие синхронизации, низкая помехоустойчивость. Эти недостатки частично устраняются в синхронном RS-триггере, который представляет собой асинхронный RS-триггер к которому добавлена схема синхронизации.

В целом работа данного триггера аналогична, с той поправкой, что при наличии на входе синхронизации низкого логического уровня триггер хранит предыдущее состояние, не реагируя на сигналы по входным линиям, т.е. в этот момент он как минимум гораздо более помехоустойчив.

Синхронный статический D-триггер

В основе данного устройства также лежит асинхронный RS-триггер, к которому присоединена схема синхронизации.

Статический D-триггер имеет один информационный вход и один вход синхронизации. Таким образом, устраняется недостаток RS-триггер – установка 0 и 1 по отдельным линиям. При наличии низкого логического уровня на входе синхронизации данное устройство хранит информацию. При подаче на вход синхронизации высокого логического уровня возможна запись информации в устройство.

Таблица истинности синхронного статического D-триггера [2]

Литература

- Отряшенков Ю.М. Юный кибернетик – М.: Детская литература, 1978

- Ямпольский В.С. Основы автоматики и электронно-вычислительной техники – М. Просвещение, 1991

Специально для сайта Радиосхемы — Denev

Форум

Обсудить статью ТРИГГЕРЫ НА МИКРОСХЕМАХ

схема, таблица истинности :: SYL.ru

В радиоэлектронике существует множество механизмов и деталей, которые с помощью простейших операций позволяют создавать сложные машины. Правда, для такой цели их нужно очень много. И одним из важнейших механизмов подобного предназначения являются JK-триггеры. Они позволяют обеспечить машинную логику для выполнения простейших логических операций. Как это осуществляется? Как необходимо подключать JK-триггер? Как выглядит таблица истинности? На эти и другие вопросы можно будет найти ответы в рамках статьи.

Что такое триггер?

Триггерами называют целый класс электронных устройств, которые имеют такое свойство, как длительное нахождение в одном из двух устойчивых состояний. Чередование осуществляется под воздействием внешних сигналов. Текущее состояние триггера с легкостью распознаётся благодаря наличию выходного напряжения. Отличительной способностью всего класса является свойство запоминать двоичную информацию. Тут возникает вопрос: есть ли у триггеров память? В обычном понимании нет. Но, тем не менее, они остаются в одном из 2 состояний, причем и после прекращения подачи сигнала. Благодаря этой особенности и считается, что они могут запоминать двоичную информацию.

При изготовлении триггеров на данный момент применяют полупроводниковые приборы (обычно полевые и биполярные транзисторы). Раньше использовали электронные лампы и электромагнитные реле. Своё применение триггеры нашли в интеграционных средах разработки, которые создаются для различных программируемых логических интегральных схем. Если говорить конкретнее, то их используют, чтобы организовать компоненты вычислительных систем: счетчики, регистры, процессоры и ОЗУ.

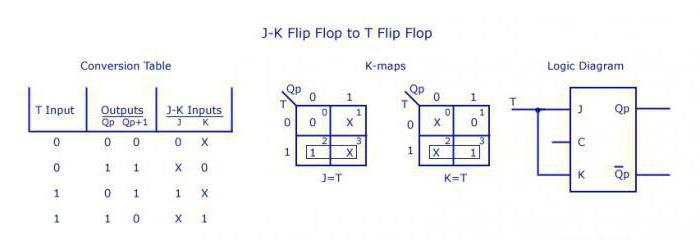

Что такое JK-триггер?

Это триггер, который в случае получения на свои оба входа логической единицы меняет состояние своего выхода на противоположное значение. Одно из отличий от других подобных приборов – отсутствие запрещенных состояний, которые могут быть на основных входах. Как выглядит JK-триггер? Схема изображения может быть представлена с разной детализацией, а также зависимо от дополнений, которые были добавлены человеком. Как видите, в статье присутствуют различные изображения устройства. Также, используя базу JK-триггера, можно создать D- или Т-модель. Как вы сможете убедиться, просмотрев таблицу истинности, данный механизм в инверсное состояние переходит всегда, когда на оба входа осуществляется подача логической единицы. Различают два вида JK-триггеров:

- Универсальные.

- Комбинированные.

Возможности

Также важным отличием данных моделей является то, что в них устранена неопределенность, которая может возникнуть в случае, если входные сигналы будут поданы в определённой комбинации. Также существенным преимуществом является тот факт, что они могут выполнять функционал T-, D- и RS-триггеров. Комбинированный тип имеет дополнительные асинхронные входы, которые используются для предварительной установки приборов в определённое состояние. Примитивный JK можно получить из RS, у которого есть динамическое управление. Для этого необходимо его дополнить обратными связями с выходов на входы. Для получения Т-триггера необходимо на входы подать уровень напряжения, который установит логическую единицу.

В каких состояниях может быть главный герой статьи? Существует два принципа действий: асинхронный и синхронный. Во время первого происходит обмен данных независимо от входов. Синхронный JK-триггер действует одновременно, и из-за требований он является основным используемым элементом.

Чтобы своими глазами увидеть, что и как работает, необходимо JK-триггер включить на макетной плате и собственноручно подавать различные входные сигналы. Это сродни обучению на гитаре – можно изучить десятки самоучителей, но пока не возьмете в руки гитару, вы никогда не научитесь. Так же и со схемами: без опыта разобраться во всём сложно. Для наблюдения можно подсоединить светодиодные индикаторы к инверсному и прямому выходу. При желании положение дел можно наблюдать и благодаря обычному вольтметру, но в связи с размерами данный вариант не очень удобный, если говорить о такой вещи, как JK-триггер.

Чтобы своими глазами увидеть, что и как работает, необходимо JK-триггер включить на макетной плате и собственноручно подавать различные входные сигналы. Это сродни обучению на гитаре – можно изучить десятки самоучителей, но пока не возьмете в руки гитару, вы никогда не научитесь. Так же и со схемами: без опыта разобраться во всём сложно. Для наблюдения можно подсоединить светодиодные индикаторы к инверсному и прямому выходу. При желании положение дел можно наблюдать и благодаря обычному вольтметру, но в связи с размерами данный вариант не очень удобный, если говорить о такой вещи, как JK-триггер.Таблица истинности

Что такое таблица истинности? Это специальный набор данных, который описывает логическую функцию. Что под ней понимают? В данном случае имеют в виду функцию, в которой значения параметров и её самой выражают логическую истинность. В качестве примера очень к месту будет вспомнить двузначную логику, где можно дать только два определения: ложь или истина. В качестве заменителей, когда говорят о компьютерных технологиях, часто вводят понятие 0 или 1. Причем использование данного инструментария оказалось удобным не только с позиции логики, но и при изображении в табличном варианте. Особенно часто их можно встретить в булевой алгебре или аналогичных системах логики. Но хватит информации, давайте посмотрим, как выглядит таблица JK-триггера.

J | K | C | Q(t) | Q(t+1) | Пояснения |

ноль | х | ноль | ноль | ноль | Хранится информация |

ноль | х | ноль | единица | единица | |

ноль | ноль | единица | ноль | ноль | Хранится информация |

ноль | ноль | единица | единица | единица | |

единица | ноль | единица | ноль | единица | Установлена логическая единица, вход J равен единице |

единица | ноль | единица | единица | единица | |

ноль | единица | единица | ноль | ноль | Устанавливается логический нуль, при этом K равно единице |

ноль | единица | единица | единица | ноль | |

единица | единица | единица | ноль | единица | счетный режим триггера K=J=1 |

Реализация счетного режима

Как же сделан счетный режим? Для достижения цели используется перекрестная обратная связь. Благодаря такому механизму никогда не может создаться запрещённая комбинация. При этом особенность, что она перекрестная, вводит дополнительный режим работы – счетный. Так, когда на входы k и j подаются логические единицы одновременно, то JK-триггер переключается в счетный режим, подобно как и Т-модель.

Заключение

Сейчас можно сказать, что вам известны основы работы JK-триггеров. И их можно закрепить на практике. При работе всегда соблюдайте осторожность. Несмотря на то что на триггеры осуществляется подача низкого напряжения, которое обычно не превышает 14 Вольт, могут быть причинены дискомфортные ощущения и/или выйти из строя другая техника. Да и прочность самих приборов лучше не проверять, роняя их вследствие неаккуратности обращения. В целом, если понять смысл работы JK-триггеров, то можно также будет запросто разобраться и с другими представителями этого семейства.

Сейчас можно сказать, что вам известны основы работы JK-триггеров. И их можно закрепить на практике. При работе всегда соблюдайте осторожность. Несмотря на то что на триггеры осуществляется подача низкого напряжения, которое обычно не превышает 14 Вольт, могут быть причинены дискомфортные ощущения и/или выйти из строя другая техника. Да и прочность самих приборов лучше не проверять, роняя их вследствие неаккуратности обращения. В целом, если понять смысл работы JK-триггеров, то можно также будет запросто разобраться и с другими представителями этого семейства.Микросхемы.

Микросхемы ТТЛ (74…).

На рисунке показана схема самого распространенного логического элемента — основы микросхем серии К155 и ее зарубежного аналога — серии 74. Эти серии принято называть стандартными (СТТЛ). Логический элемент микросхем серии К155 имеет среднее быстродействие tзд,р,ср.= 13 нс. и среднее значение тока потребления Iпот = 1,5…2 мА. Таким образом, энергия, затрачиваемая этим элементом на перенос одного бита информации, примерно 100 пДж.

Для обеспечения выходного напряжения высокого уровня U1вых. 2,5 В в схему на рисунке потребовалось добавить диод сдвига уровня VD4, падение напряжения на котором равно 0,7 В. Таким способом была реализована совместимость различных серий ТТЛ по логическим уровням. Микросхемы на основе инвертора, показанного на рисунке (серии К155, К555, К1533, К1531, К134, К131, К531), имеют очень большую номенклатуру и широко применяются.

| ТТЛ серия | Параметр | Нагрузка | ||||

|---|---|---|---|---|---|---|

| Российские | Зарубежные | Pпот. мВт. | tзд.р. нс | Эпот. пДж. | Cн. пФ. | Rн. кОм. |

| К155 КМ155 | 74 | 10 | 9 | 90 | 15 | 0,4 |

| К134 | 74L | 1 | 33 | 33 | 50 | 4 |

| К131 | 74H | 22 | 6 | 132 | 25 | 0,28 |

| К555 | 74LS | 2 | 9,5 | 19 | 15 | 2 |

| К531 | 74S | 19 | 3 | 57 | 15 | 0,28 |

| К1533 | 74ALS | 1,2 | 4 | 4,8 | 15 | 2 |

| К1531 | 74F | 4 | 3 | 12 | 15 | 0,28 |

При совместном использовании микросхем ТТЛ высокоскоростных, стандартных и микромощных следует учитывать, что микросхемы серии К531 дают увеличенный уровень помех по шинам питания из-за больших по силе и коротких по времени импульсов сквозного тока короткого замыкания выходных транзисторов логических элементов. При совместном применении микросхем серий К155 и К555 помехи невелики.

| Нагружаемый выход |

Число входов-нагрузок из серий | ||

|---|---|---|---|

| К555 (74LS) | К155 (74) | К531 (74S) | |

| К155, КM155, (74) | 40 | 10 | 8 |

| К155, КM155, (74), буферная | 60 | 30 | 24 |

| К555 (74LS) | 20 | 5 | 4 |

| К555 (74LS), буферная | 60 | 15 | 12 |

| К531 (74S) | 50 | 12 | 10 |

| К531 (74S), буферная | 150 | 37 | 30 |

Выходы однокристальных, т. е. расположенных в одном корпусе, логических элементов ТТЛ, можно соединять вместе. При этом надо учитывать, что импульсная помеха от сквозного тока по проводу питания пропорционально возрастет. Реально на печатной плате остаются неиспользованные входы и даже микросхемы (часто их специально «закладывают про запас») Такие входы логического элемента можно соединять вместе, при этом ток Ioвх. не увеличивается. Как правило, микросхемы ТТЛ с логическими функциями И, ИЛИ потребляют от источников питании меньшие токи, если на всех входах присутствуют напряжения низкого уровня. Из-за этого входы таких неиспользуемых элементов ТТЛ следует заземлять.

| Параметр | Условия измерения | К155 | К555 | К531 | К1531 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Мин. | Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Макс. | ||

| U1вх, В схема |

U1вх или U0вх Присутствуют на всех входах | 2 | 2 | 2 | 2 | |||||||

| U0вх, В схема |

0,8 | 0,8 | 0,8 | |||||||||

| U0вых, В схема | Uи.п.= 4,5 В | 0,4 | 0,35 | 0,5 | 0,5 | 0,5 | ||||||

| I0вых= 16 мА | I0вых= 8 мА | I0вых= 20 мА | ||||||||||

| U1вых, В схема |

Uи.п.= 4,5 В | 2,4 | 3,5 | 2,7 | 3,4 | 2,7 | 3,4 | 2,7 | ||||

| I1вых= -0,8 мА | I1вых= -0,4 мА | I1вых= -1 мА | ||||||||||

| I1вых, мкА с ОК схема | U1и.п.= 4,5 В, U1вых=5,5 В | 250 | 100 | 250 | ||||||||

| I1вых, мкА Состояние Z схема |

U1и.п.= 5,5 В, U1вых= 2,4 В на входе разрешения Е1 Uвх= 2 В | 40 | 20 | 50 | ||||||||

| I0вых, мкА Состояние Z схема |

U1и.п.= 5,5 В, Uвых= 0,4 В, Uвх= 2 В | -40 | -20 | -50 | ||||||||

| I1вх, мкА схема | U1и.п.= 5,5 В, U1вх= 2,7 В | 40 | 20 | 50 | 20 | |||||||

| I1вх, max, мА | U1и.п.= 5,5 В, U1вх= 10 В | 1 | 0,1 | 1 | 0,1 | |||||||

| I0вх, мА схема |

U1и.п.= 5,5 В, U0вх= 0,4 В | -1,6 | -0,4 | -2,0 | -0,6 | |||||||

| Iк.з., мА | U1и.п.= 5,5 В, U0вых= 0 В | -18 | -55 | -100 | -100 | -60 | -150 | |||||

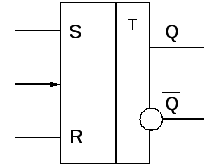

1.2.3. Асинхронный т-триггер

Асинхронный Т-триггер имеет только один счетный вход Т. УГО асинхронного Т-триггера, его схема и диаграмма работы представлены на рисунке 1.9.

|

|

|

а) | б) | в) |

Рис. 1.9 – УГО Т-триггера (а), схема (б), диаграмма работы (в) | ||

Т-триггер изменяет свое состояние на противоположное всякий раз, когда на вход Т поступает сигнал «1».

Работу асинхронного Т-триггера можно описать таблицей истинности, таблица 1.3.

Таблица 1.3 – Таблица истинности асинхронного Т-триггера

Тt

Qt

Qt+1

0

0

0

1

0

1

0

1

1

1

1

0

1.3. Синхронные триггеры

1.3.1. Синхронный rs-триггер

УГО синхронного RS-триггера, его схема и диаграмма работы представлены на рисунке 1.10.

|

|

|

а) | б) | в) |

Рис.1.10 – УГО синхронного RS-триггера (а), схема (б), диаграмма работы (в) | ||

Работу синхронного RS-триггера можно описать таблицей истинности, таблица 1.4.

Таблица 1.4 – Таблица истинности синхронного RS-триггера

St

Rt

Ct

Qt

Qt+1

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

0

0

0

0

0

1

1

0

1

0

1

1

1

0

0

1

1

1

1

0

1

1

0

0

1

0

0

0

1

1

0

0

1

0

1

0

1

1

1

1

0

—

0

0

1

1

1

0

1

1

1

0

1

0

1

1

1

1

1

1

1

—

1.3.2. D-триггер

УГО D-триггера, его схема и диаграмма работы представлены на рисунке 1.11.

|

|

|

а) | б) | в) |

Рис. 1.11 – УГО D-триггера (а), схема (б), диаграмма работы (в) | ||

D-триггер (триггер задержки) является самым распространенным триггером. Он имеет один информационный вход D (вход данных) и один тактовый вход C.

Тактируется триггер (то есть меняет свое состояние) по положительному фронту сигнала С (по его переходу из нуля в единицу) в зависимости от состояния входа данных D. Если на входе D единичный сигнал, то по положительному фронту сигнала С прямой выход триггера устанавливается в единицу (инверсный – в ноль). Если же на входе D – нулевой сигнал, то по фронту сигнала С прямой выход триггера устанавливается в ноль (инверсный – в единицу).

Работу D-триггера можно описать таблицей истинности, таблица 1.5.

Таблица 1.5 – Таблица истинности синхронного D-триггера

Ct

Dt

Qt

Qt+1

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

1

1

1

1

1

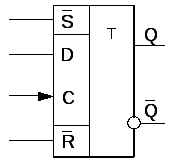

1.3.3. D-триггер с установочными входами

УГО D-триггера с установочными входами, его схема и диаграмма работы представлены на рисунке 1.12.

|

|

а) | б) |

Рис. 1.12 – УГО

D-триггера с установочными входами диаграмма работы (б) | |

В момент t1

работа триггера определяется установочным

сигналом на входе  (логический «0») – триггер переключается

в состояние «0».

(логический «0») – триггер переключается

в состояние «0».

В момент t2, сигналы на установочных входах неактивны, на входе D присутствует сигнал «1», на входе С – положительный фронт, триггер переключается из состояния «0» в состояние «1».

В момент t3 сигналы на установочных входах неактивны, на входе D присутствует сигнал «0», на входе С – положительный фронт, триггер переключается из состояния «1» в состояние «0».

В момент t4

работа триггера определяется установочным

сигналом на входе  ,

(логический «0») – триггер переключается

в состояние «1».

,

(логический «0») – триггер переключается

в состояние «1».

Следует помнить, что согласно схемотехнической организации триггера с установочными входами при одновременном действии сигналов на один из установочных входов, информационный вход и вход синхронизации С состояние триггера определяет установочный вход.

На установочные

входы  ,

, активные сигналы (

активные сигналы ( =

= = 0) одновременно поданы быть не могут

(согласно схеме

= 0) одновременно поданы быть не могут

(согласно схеме -триггера

это запрещенная комбинация).

-триггера

это запрещенная комбинация).

Методическое пособие по курсу «Цифровая техника и микропроцессоры», страница 3

R = 0 R = 1

Значит, состояние входа R для рассматриваемого перехода безразлично. Отразим это в первой строчке таблицы возбуждения прочерком в столбце R:

Q(t) | S | R | Q(t+1) |

0 | 0 | — | 0 |

Переходам 0 -> 1 и 1 -> 0 соответствуют однозначные комбинации, а переходу 1 -> 1 — опять две, из которых вытекает безразличность состояния входа S. Заполнив все строки таблицы, получим окончательно таблицу возбуждения RS – триггера:

Q(t) | S | R | Q(t+1) |

0 | 0 | — | 0 |

0 | 1 | 0 | 1 |

1 | 0 | 1 | 0 |

1 | — | 0 | 1 |

Эта таблица пригодится при синтезе триггеров других типов, а также цифровых автоматов.

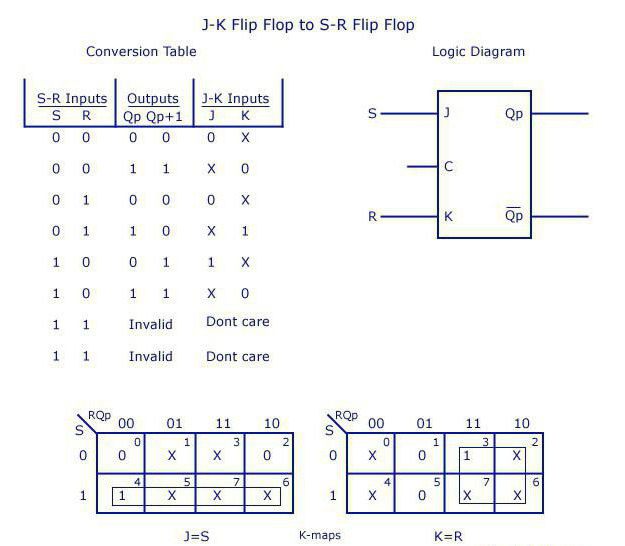

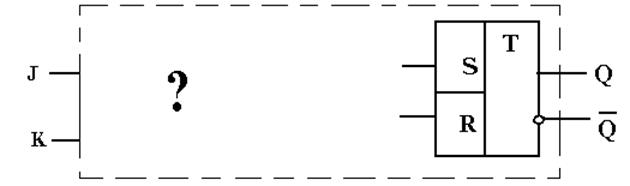

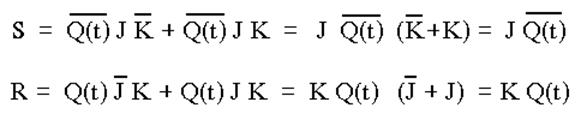

1.2. Асинхронный JK – триггер

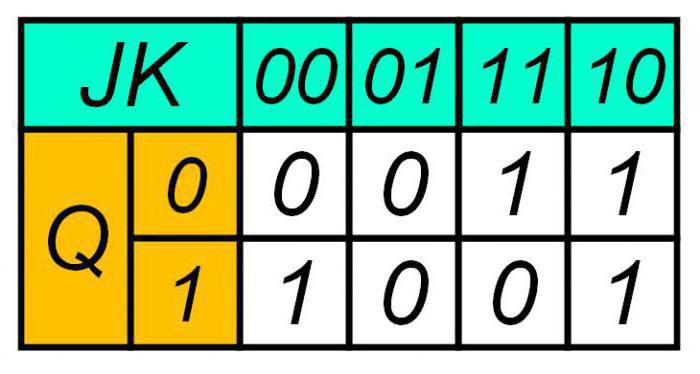

Нарушим общепринятую последовательность рассмотрения триггеров различных типов и рассмотрим синтез асинхронного JK-триггера, поскольку он является “старшим братом” RS-триггера ввиду большого сходства их таблиц истинности. Таблица истинности JK-триггера почти полностью совпадает с таблицей истинности RS-триггера и отличается лишь тем, что при подаче на входы комбинации «11» JK-триггер обязан переключиться в противоположное состояние.

Вот его таблица истинности (сравните с таблицей истинности RS-триггера):

Табл. 2. Таблица истинности JK-триггера

Q(t) | J | K | Q(t+1) | Действие |

0 | 0 | 0 | 0 | хранение |

0 | 0 | 1 | 0 | сброс в 0 |

0 | 1 | 0 | 1 | установка в 1 |

0 | 1 | 1 | 1 | инверсия выхода |

1 | 0 | 0 | 1 | хранение |

1 | 0 | 1 | 0 | сброс в 0 |

1 | 1 | 0 | 1 | установка в 1 |

1 | 1 | 1 | 0 | инверсия выхода |

Разумно предположить, что JK-триггер может успешно заменять RS-триггер в любой цифровой схеме, причем вход J будет выполнять роль входа S, а вход K – роль входа R.

Пояснение. Символы J и K не несут

никакой мнемоники и являются просто

последовательными буквами алфавита.

Получим логическое уравнение JK-триггера. Для этого заполним карту Карно и найдем МДНФ.

|

Это и есть логическое уравнение JK-триггера. Его полезно запомнить.

Синтезируем базовую схему JK-триггера на основе уже имеющегося RS-триггера, поскольку RS-триггер является простейшей ячейкой хранения одного бита информации. Рассмотрим «черный ящик», на выходе которого стоит RS-триггер:

|

Вся будущая структура должна функционировать как JK-триггер. Поскольку на выходе стоит RS-триггер, то именно он определяет выходной сигнал, и, следовательно, обязан переключаться в соответствии с таблицей истинности JK-триггера. Для этого необходимо и достаточно сформировать на его входах S и R нужные сигналы для каждой строки таблицы.

Дополним таблицу истинности JK-триггера двумя столбцами для сигналов S и R и впишем в них нужные комбинации из таблицы возбуждения RS-триггера, чтобы обеспечить каждый переход вида Q(t) -> Q(t+1):

Q(t) | J | K | Q(t+1) | Нужно подать | ||

S | R | |||||

0 | 0 | 0 | 0 | 0 | — | |

0 | 0 | 1 | 0 | 0 | — | |

0 | 1 | 0 | 1 | 1 | 0 | |

0 | 1 | 1 | 1 | 1 | 0 | |

1 | 0 | 0 | 1 | — | 0 | |

1 | 0 | 1 | 0 | 0 | 1 | |

1 | 1 | 0 | 1 | — | 0 | |

1 | 1 | 1 | 0 | 0 | 1 | |

переходы

переходы

Эта расширенная таблица позволяет записать СДНФ для сигналов S и R, считая аргументами столбцы Q(t),J,K:

|

Теперь очевидна

реализация JK-триггера:

Теперь очевидна

реализация JK-триггера:

Рис.2. Принцип

построения

JK-триггера

Следует заметить, что эта структура поясняет лишь принцип построения JK-триггера, в действительности она неработоспособна! Нетрудно догадаться, что при подаче сигналов J = K = 1 такой триггер превратится в автогенератор меандра, поскольку будет непрерывно изменять свое состояние на противоположное.

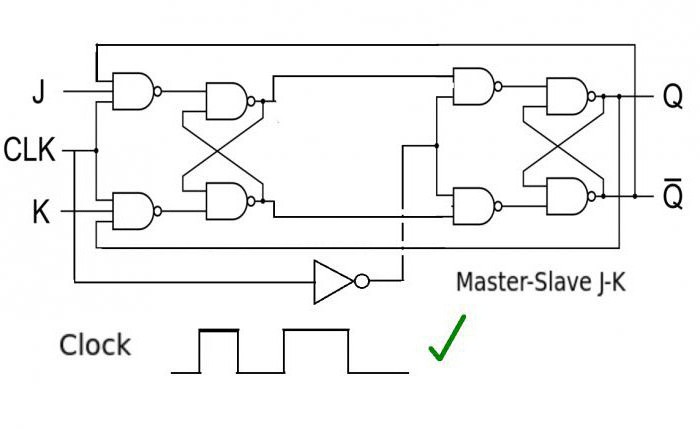

Поэтому на практике эту схему обычно выполняют двухтактной или вводят дополнительные элементы, превращающие выходную ступень в непрозрачный триггер, устраняя тем самым возможность паразитной автогенерации.

По таблице истинности легко составить таблицу возбуждения JK-триггера:

Q(t) | J | K | Q(t+1) |

0 | 0 | — | 0 |

0 | 1 | — | 1 |

1 | — | 1 | 0 |

1 | — | 0 | 1 |

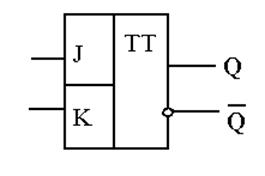

JK-триггер принято называть универсальным триггером. Это

название отражает тот факт, что на его основе легко построить триггер любого

другого типа. Признаком выполнения триггера по двухтактной схеме является

наличие двух букв TT в правой части символа

изображения триггера. Заметим, что принципиально выполнима задача взаимной

трансформации триггеров любых типов.

JK-триггер принято называть универсальным триггером. Это

название отражает тот факт, что на его основе легко построить триггер любого

другого типа. Признаком выполнения триггера по двухтактной схеме является

наличие двух букв TT в правой части символа

изображения триггера. Заметим, что принципиально выполнима задача взаимной

трансформации триггеров любых типов.

1.3. Асинхронный Т-триггер (счетный триггер)

Поставим задачу синтезировать схему триггера, который инвертирует свое состояние каждый раз, когда на его единственном управляющем входе T появляется уровень логической единицы. Наглядно это можно изобразить временной диаграммой, полагая в частном случае, что

Динамические параметры микросхем ТТЛ серии

Динамические параметры микросхем ТТЛ серии

(а),

(а),