Асинхронный R-S триггер на элементах «И-НЕ» и «ИЛИ-НЕ»

Триггеры – это устройства для хранения информации. Они являются костяком более сложных устройств, таких как счетчики, шифраторы, дешифраторы, регистры и прочие устройства.

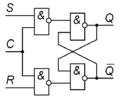

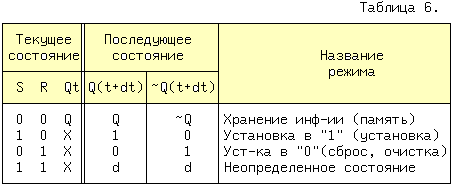

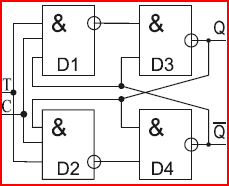

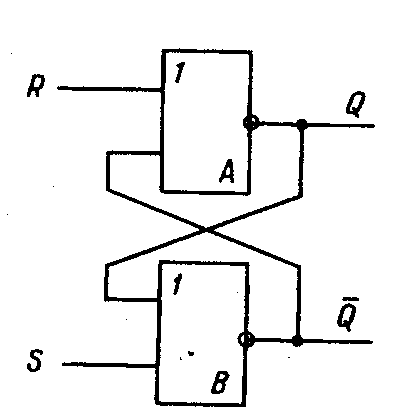

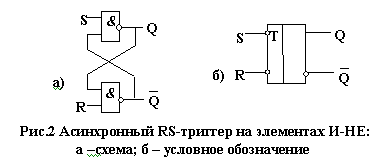

Мы рассмотрим асинхронный R–S триггер на примере двух элементов «И — НЕ». Схема и таблица истинности этого устройства показана ниже:

Как мы можем видеть из схемы, триггер имеет два входа  и

и  . На каждый вход подается различная комбинация сигналов (смотри таблицу истинности). Также у триггера есть два выхода – один прямой Q, а один инверсный

. На каждый вход подается различная комбинация сигналов (смотри таблицу истинности). Также у триггера есть два выхода – один прямой Q, а один инверсный  . Если

. Если

=1, то Q = 0.

=1, то Q = 0.Схема построена таким образом, что при подаче сигнала S=1 (что равнозначно  =0), на выходе получаем Q = 1. S от английского слова set – устанавливать. Когда S=0 (

=0), на выходе получаем Q = 1. S от английского слова set – устанавливать. Когда S=0 ( =1),то выход Q = 0. Если мы на вход R подадим сигнал, который будет инверсный по отношению к сигналу S, то при R=1, S=0, единица на выходе Q поменяет свое значение на ноль. Отсюда происходит и название входа, от английского слова reset – сброс, то есть вход R сбрасывает значение, установленное со входа S.

=1),то выход Q = 0. Если мы на вход R подадим сигнал, который будет инверсный по отношению к сигналу S, то при R=1, S=0, единица на выходе Q поменяет свое значение на ноль. Отсюда происходит и название входа, от английского слова reset – сброс, то есть вход R сбрасывает значение, установленное со входа S.

Давайте рассмотрим принцип работы этой схемы. Пускай выходы триггера имели следующие значения Q=0, а  = 1.

= 1.

На вход мы подадим следующие сигналы  =0,

=0,  =1. Поскольку элемент Е1 является инверсным, то на выходе Q будет равным единицы. Элемент Е2 тоже является инверсным и при установлении

=1. Поскольку элемент Е1 является инверсным, то на выходе Q будет равным единицы. Элемент Е2 тоже является инверсным и при установлении  =1, а также при приходе от выхода Q единицы, на вход элемента «И-НЕ» поступит две единицы, где в итоге получим

=1, а также при приходе от выхода Q единицы, на вход элемента «И-НЕ» поступит две единицы, где в итоге получим

=0 и

=0 и  =0 на выходе Q будет установлен сигнал равен единице.

=0 на выходе Q будет установлен сигнал равен единице.Если мы зеркально изменим сигнал на входе триггера ( =1,

=1,  =0), то на входе Е2 мы получим единицу и ноль, и сигнал на

=0), то на входе Е2 мы получим единицу и ноль, и сигнал на

Также если подать на оба входа  и

и  подать единицы, то сигналы на выходе не изменятся вообще. Эта комбинация оставляет триггер в предыдущем состоянии (Qn+1=Q).

подать единицы, то сигналы на выходе не изменятся вообще. Эта комбинация оставляет триггер в предыдущем состоянии (Qn+1=Q).

Рассмотрим случай когда на вход будут поданы следующие сигналы:

=0. Если до этого на выходе Q=0,

=0. Если до этого на выходе Q=0,  =1, то на входе Е1 будет единица и ноль, то есть Q изменится на единицу. Тогда на Е2 будет нуль и единица и

=1, то на входе Е1 будет единица и ноль, то есть Q изменится на единицу. Тогда на Е2 будет нуль и единица и  останется единицей. Соответственно на выходе будет два абсолютно одинаковых сигнала. Такое положение не нормальное для работы триггера, поэтому при его работе комбинации

останется единицей. Соответственно на выходе будет два абсолютно одинаковых сигнала. Такое положение не нормальное для работы триггера, поэтому при его работе комбинации  =0 и

=0 и

=0, то подача

=0, то подача  =0 и

=0 и  =0 приведет к такому же результату, что и в предыдущем случае.

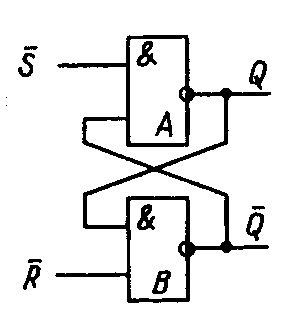

=0 приведет к такому же результату, что и в предыдущем случае.Ниже показан асинхронный R –S триггер на базе элементов «ИЛИ-НЕ», а также его таблица истинности.

Синхронные и асинхронные одноступенчатые триггеры типов rs,dv,t.

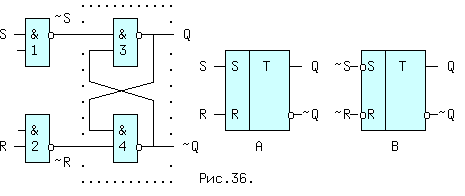

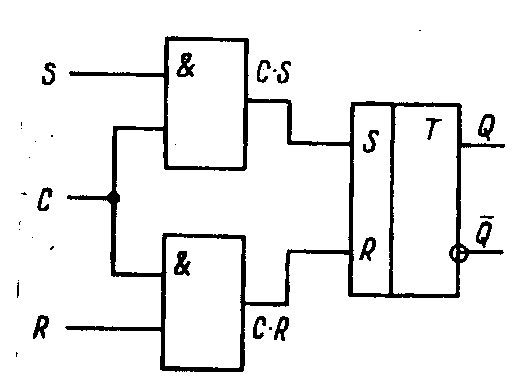

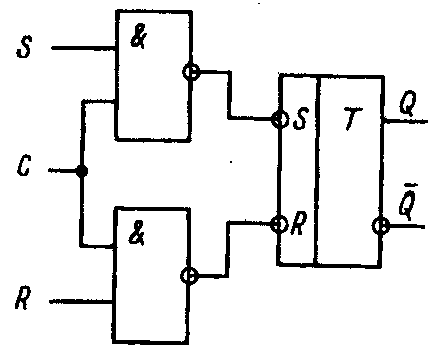

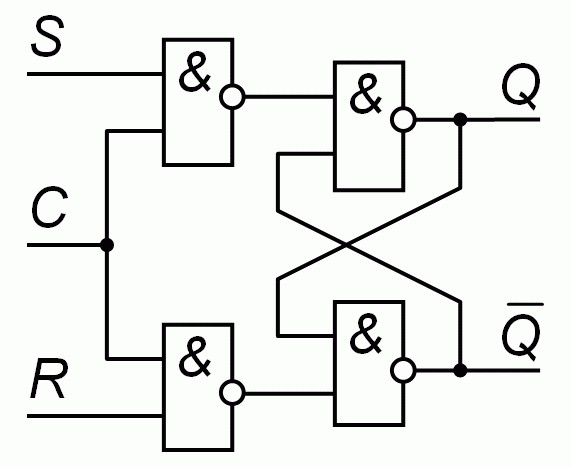

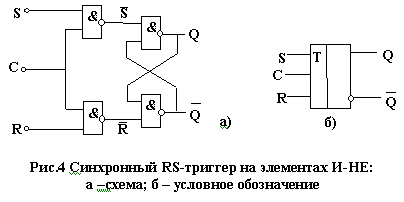

СИНХРОННЫЙ

RS – ТРИГГЕР. Если незадействованные

входы элементов И-НЕ 1 и 2 соединить

вместе (рис. 36), получится синхронный

RS — триггер со статическим управлением

(синхронизируемый уровнем).

Схема и условное обозначение приведены

на рис.39.

Нетрудно

убедиться, что при C=0 сигнал Q=~(~Q*1)=Q, а

~Q=~(Q*1)=~Q, т.е. независимо от значений S и

R, выходы сохраняют старые значения и

триггер находится в режиме памяти. При

C=1 он функционирует, как асинхронный

RS-триггер. Триггеры со статическим управлением

называют, также «прозрачными»,

т.к. при активном уровне синхросигнала

C, информация с входов беспрепятственно

проходит на выходы. Временные диаграммы

приведены на рис.40.

До момента времени t4 сигнал C = 1 и выходное значение определяется комбинациями сигналов R и S. В течение интервала времени t0…t1 на входе R действует 1, а сигнал S = 0, поэтому Q тоже равно 0. Начиная с момента t1 и до момента t2 R = S = 0 и действует режим памяти (Q не изменяется). В момент t2 R = 0,а S = 1 и триггер устанавливается (Q = 1). С момента окончания импульса S и до момента t3 триггер хранит эту единицу, а в момент t3 сбрасывается, т.к.R = 0, а S = 1. Аналогично можно проанализировать и все остальные состояния выхода.

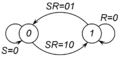

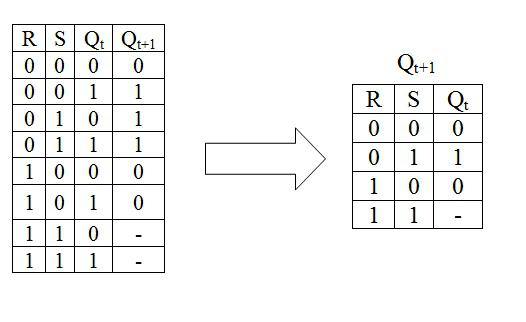

АСИНХРОННЫЙ RS – ТРИГГЕР. Асинхронный триггер имеет два входа S(et) — установка и R(eset) — сброс и два выхода прямой — Q и инверсный — ~Q. Триггер переходит из текущего состояния X на выходе к состоянию 0, при подаче на вход S нуля и на вход R единицы, а при поступлении на вход S единицы и на вход R нуля триггер переходит к состоянию 1. При нулевых значениях, когда S=R=0 триггер должен сохранять старое значение. Комбинация сигналов S=R=1 не определена.

Q

и X — могут принимать любые значения, но

Q в пределах одной строки, неизменно.

Значения d будут доопределены на этапе

минимизации. Входных переменных три —

S,R и текущее состояние выхода Qt, поэтому

всего должно быть восемь состояний при

различных значениях Q и X. Последующее

состояние выходов отделено от текущего

временем задержки сигнала dt. Таблица

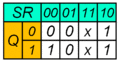

Карно функции Q(t+dt) с учетом всех возможных

состояний приведена на рис.35, слева.

Доопределяем значения d единицей и находим характеристическое уравнение RS — триггера:

Q(t+dt) = S + ~R*Qt = ~(~S * ~(~R*Q)). (26)

Этому уравнению соответствует схема на рис.35, справа. Учитывая, что Qt и Q(t+dt) сигналы на одном и том же выходе, но в разные моменты времени, свяжем их. Окончательно схема триггера и его условное обозначение будет выглядеть, как на рис.36.

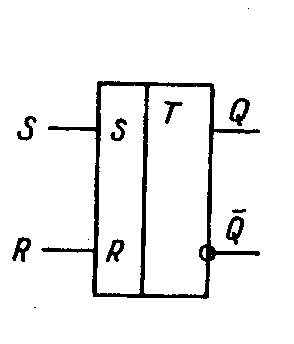

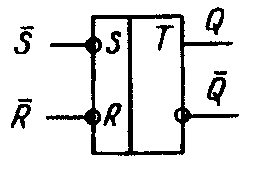

Условное обозначение B соответствует части рисунка, обведенной точками, т.е. RS триггеру с инверсными входами, а обозначение A — всему рисунку, или RS триггеру с прямыми входами.

Если на триггер с прямымивходами подать сигналы R=S=1 или на входы инверсного — нули, то оба выхода Q и ~Q будут установлены в 1, что противоречит аксиоме Q*~Q = 0. Поэтому такой режим, иногда называют запрещенным. Однако ничто не мешает разработчику использовать его, например для сигнализации об одновременном и нежелательном поступлении единичных сигналов на RS входы, введением дополнительной схемы И.

Временные диаграммы RS триггера с инверсными входами приведены на рис.37. Через время tзд.р., обозначенное «-«, от поступления сигнала ~S = 0 на вход элемента И-НЕ с номером 3, выход Q переключится первым, а следом через такой же промежуток времени переключится и выход ~Q. Спустя интервал времени t2 — t0 = dt на выходах установятся новые значения. Также протекает процесс при ~R = 0, но выход ~Q переключится первым. Отсюда вытекает, что изменение входных сигналов не должно происходить быстрее времени dt.

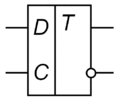

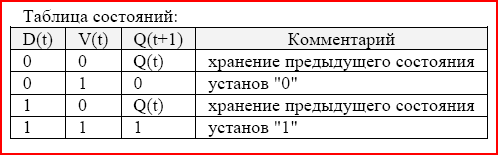

D-триггер. На практике наибольшее распространение получила схема синхронногоD-триггера со статическим управлением записью.D-триггер имеет один логический входD(Delay— задержка), состояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. СхемуD-триггера можно получить изRS-триггера, если на входRподать инвертированный сигнал входаS.Однако целесообразно использовать для инвертирования уже имеющиеся элементы (рис. 3.6).

DV-триггер. Если кD-триггеру добавить еще один входV(Vorentscheidung- предварительное разрешение) для блокирования СИ (пунктирная линия на рис 3.6), то получим синхронныйDV-триггер со статическим управлением записью. Легко заметить, что входы С иVможно поменять местами без нарушения логики работы триггера.

Одноступенчатый

асинхронный T – триггер.

Счетный Т-триггер. Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и -Q. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом . Как видно из диаграммы, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

Одноступенчатый

синхронный T – триггер.

Чтобы сгладить проблему ограничения по длине импульса в асинхронном одноступенчатом триггере можно усовершенствовать схему и сделать триггер синхронным. Т.е. взяли и добавили ещё вход С на элементы D1 и D2. Тогда действительно управляющий вход Т который разрешает работу этому Т-триггеру в счетном режиме. А вход синхронизации будет выполнять ту же самую роль что и вход Т в асинхронном режиме.

Типы триггеров rs-триггеры rs-триггер асинхронный

S | R | Q(t) | Q(t) | Q(t+1) | Q(t+1) |

0 | 0 | 0 | 1 | 0 | 1 |

0 | 0 | 1 | 0 | 1 | 0 |

0 | 1 | 0 | 1 | 0 | 1 |

0 | 1 | 1 | 0 | 0 | 1 |

1 | 0 | 0 | 1 | 1 | 0 |

1 | 0 | 1 | 0 | 1 | 0 |

1 | 1 | 0 | 1 | не определено | не определено |

1 | 1 | 1 | 0 | не определено | не определено |

Асинхронный RS-триггер с инверсными входами

RS-триггер[10][11], илиSR-триггер— триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S(отангл.Set— установить) выходное состояние становится равным логической единице. А при подаче единицы на входR(отангл.Reset— сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входаRиSодновременно поданы логические единицы не определено и зависит от реализации, например в триггере на элементах «или-не» оба выхода переходят в состояние логического «0», которое является неустойчивым и переходит в одно из устойчивых состояний при снятии управляющего сигнала с одного из входов.

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

RS-триггеры иногда называют RS-фиксаторами[12].

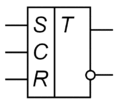

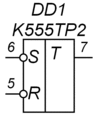

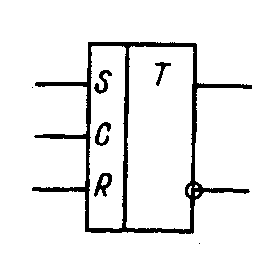

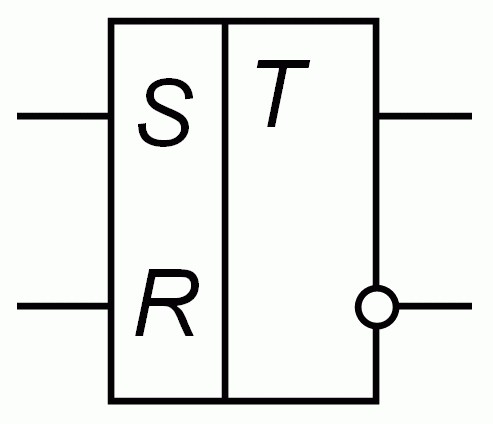

Условное графическое обозначение асинхронного RS-триггера

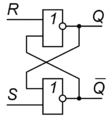

Логическая схема асинхронного RS-триггера на элементах 2И–НЕ

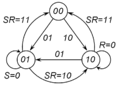

Графпереходов асинхронного RS-триггера

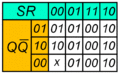

Карта Карноасинхронного RS-триггера

Асинхронный RS-триггер на логических элементах 2ИЛИ-НЕ

Схема устранения дребезга контактов

Rs-триггер синхронный

C | S | R | Q(t) | Q(t+1) |

0 | x | x | 0 | 0 |

1 | 1 | |||

1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 1 | 1 |

1 | 0 | 1 | 0 | 0 |

1 | 0 | 1 | 1 | 0 |

1 | 1 | 0 | 0 | 1 |

1 | 1 | 0 | 1 | 1 |

1 | 1 | 1 | 0 | не определено |

1 | 1 | 1 | 1 | не определено |

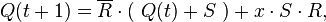

Алгоритм функционирования синхронного RS-триггера можно представить формулой

где x — неопределённое состояние.

Условное графическое обозначение синхронного RS-триггера

Схема синхронного RS-триггера на элементах 2И-НЕ

Граф переходов синхронного RS-триггера

Карта Карно синхронного RS-триггера

Rs-триггер двухступенчатый со сложной логикой

Рис. 1 Схема RS-триггера двухступенчатого со сложной логикой на элементах 2И-НЕ и 3И-НЕ

УГО данного триггера изображено на рис.1. Следует отметить, что на данном рисунке неправильно подается тактовый сигнал (На второй каскад тактовый сигнал должен подаваться с инверсией).

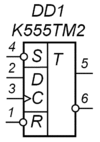

D-триггеры

D-триггеры также называют триггерами задержки(от англ. Delay).

D-триггер синхронный

Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами SиR

D | Q(t) | Q(t+1) |

0 | 0 | 0 |

0 | 1 | 0 |

1 | 0 | 1 |

1 | 1 | 1 |

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 Dвхода подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

Условное графическое обозначение D-триггера со статическим входом синхронизации С

Основные элементы цифровой микропроцессорной техники.

Полупроводниковые запоминающие устройства

4.1 Элементы микропроцессорной техники

Триггеры Интегральные триггеры обычно реализуются на логических элементах И-НЕ, ИЛИ-НЕ. Триггер предназначен для хранения значения одной логической переменной (или значения одноразрядного двоичного числа; при хранении многоразрядных двоичных чисел для запоминания значения каждого разряда числа используются отдельный триггер). В соответствии с этим, триггер имеет два состояния: одно из них обозначается как состояние 0, другое – как состояние 1. Воздействуя на входы триггера, его устанавливают в нужное состояние.

Триггер

имеет два выхода: прямой Q

и инверсный  .

Состояние, в котором находится триггер,

определяется уровнями напряжения на

этих выходах: если напряжение на выходе

Q соответствует уровню лог.0 (Q = 0), то

принимается, что триггер находится в

состоянии 0, при Q = 1 триггер, находится

в состоянии 1. Логический уровень на

инверсном выходе

.

Состояние, в котором находится триггер,

определяется уровнями напряжения на

этих выходах: если напряжение на выходе

Q соответствует уровню лог.0 (Q = 0), то

принимается, что триггер находится в

состоянии 0, при Q = 1 триггер, находится

в состоянии 1. Логический уровень на

инверсном выходе представляет собой инверсию состояния

триггера (в состоянии 0

представляет собой инверсию состояния

триггера (в состоянии 0 = 1, и наоборот).

= 1, и наоборот).

Триггеры имеют различные типы входов. Их обозначения и назначения:

R (от англ. Reset) —раздельный вход установки в состояние 0;

S (от англ. Set) —раздельный вход установки в состояние 1;

К— вход установки универсального триггера в состояние 0;

J — вход установки универсального триггера в состояние 1;

Т— счетный вход;

D (от англ. Delay) — информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе,

С—управляющий (синхронизирующий) вход.

Наименование триггера определяется типами его входов. Например, RS-триггер — триггер, имеющий входы типов R и S.

По характеру реакции на входные сигналы триггеры делятся на два типа: асинхронные и синхронные. В асинхронном триггере входные сигналы воздействуют на состояние триггера непосредственно с момента их подачи на входы, в синхронных триггерах — только при подаче синхронизирующего сигнала на управляющий вход С.

Асинхронные триггеры

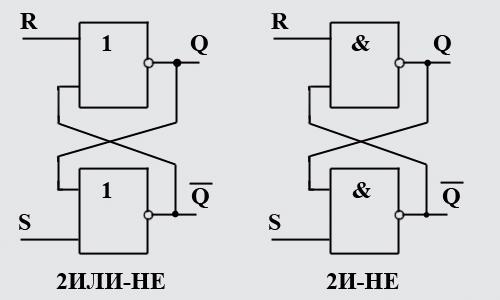

RS-триггер с прямыми входами. Логическая структура триггера представлена на рис. 4.1а. Триггер построен на двух логических элементах ИЛИ-НЕ, связанных таким образом, что выход каждого элемента подключен к одному из входов другого. Такое соединение элементов в устройстве обеспечивает два устойчивых состояния. Переключение триггера из одного устойчивого состояния в другое происходит при подаче активных сигналов на входы.

На рис. 4.2 ,б показано условное обозначение асинхронного RS-триггера.

а) б) Рис. 4.1

Rs-триггер с инверсными входами

а) б) Рис. 4.2

Логическая структура триггера приведена на рис. 4.1,а. Отличие от логической структуры рассмотренного выше RS-триггера с прямыми входами состоит лишь в том, что здесь использованы логические элементы И-НЕ. На рис. 4.2,б показано условное обозначение RS-триггера с инверсными входами.

Синхронные триггеры со статическим управлением

Отличие синхронного триггера от асинхронного состоит в том, что синхронный триггер снабжен дополнительным входом, называемым синхронизирующим (этот вход часто называют также тактирующим входом). Назначение синхронизирующего входа в том, чтобы сигналом на этом входе разрешать прием сигналов с информационных входов (входов, сигналами на которых производится переключение триггера) в заданные временные интервалы. При отсутствии сигнала на синхронизирующем входе информационные входы логически отключаются и сигналы на этих входах не влияют на состояние триггера.

Достоинство синхронных триггеров заключается в том, что они позволяют устранять влияние различий в значении задержек в распространении сигнала в отдельных элементах схемы. При этом обеспечивается одновременный прием сигналов разными частями схемы в заданные временные отрезки.

Синхронные триггеры, в свою очередь, делятся на два типа: синхронные триггеры со статическим управлением и синхронные триггеры с динамическим управлением. В первых триггеры реагируют на изменения сигналов на информационных входах, происходящие во время действия сигнала на синхронизирующем входе. Поэтому эти изменения допускаются только при отсутствии сигнала на синхронизирующем входе. В синхронных триггерах с динамическим управлением прием сигналов с информационных входов происходит в течение малой длительности фронта (положительного или отрицательного) сигнала на синхронизирующем входе. В остальное время информационные входы оказываются логически отключенными и допускаются изменения сигналов на информационных входах и в течение действия синхронизирующего сигнала (исключая длительность его фронта).

RS-триггер. На рис. 4.3а, б показаны логические структуры синхронного RS-триггера. Как видно из этих структур, синхронный RS-триггер состоит из асинхронного триггера с прямыми (либо инверсными) входами, на входах R и S которого включены логические элементы И (И-НЕ).

а) б) в) Рис. 4.3

С помощью логических элементов И (И-НЕ) обеспечивается передача активных логических уровней информационных входов S и R синхронного триггера на входы S и R входящего в его состав асинхронного триггера только при уровне лог. 1 на синхронизирующем входе С.

На рис. 4.3 в показано условное обозначение синхронного RS-триггера.

D-триггер. Этот тип триггера имеет лишь один информационный вход D. Вход С — управляющий и служит для подачи синхронизирующего сигнала.

Синхронные триггеры, построенные по принципу двухступенчатого запоминания информации

Особенность триггеров с двухступенчатым запоминанием информации состоит в том, что они содержат две триггерные структуры: одна из них образует так называемый ведущий триггер, другая — ведомый триггер. Оба триггера функционируют как синхронные триггеры со статическим управлением.

Если на синхронизирующем входе С=1, ведущий триггер устанавливается в состояние, соответствующее сигналам, поступающим на информационные входы. Ведомый триггер, имеющий инверсный синхронизирующий вход, при этом невосприимчив к информации, поступающей на его вход с выхода ведущего триггера. Он продолжает находиться в состоянии, в которое был ранее установлен (в предыдущем тактовом периоде).

При изменении значения С (с С=1 на С=0) ведущий триггер отключается от информационных входов и перестает реагировать на изменения значений сигналов на этих входах; ведомый триггер устанавливается в состояние, в котором находится ведущий триггер. С этого момента на входах устанавливаются значения, соответствующие входным сигналам, поступающим к моменту рассматриваемого фронта сигнала на синхронизирующем входе.

Управление процессами в триггере с двухступенчатым запоминанием информации за время тактового периода осуществляется двумя фронтами сигнала на синхронизирующем входе: на положительном фронте происходит установка ведущего триггера, на отрицательном фронте — ведомого триггера.

RS-триггер. Принцип работы, функциональные схемы, таблица переходов

Триггер – простейшее устройство, представляющее собой цифровой автомат. Он имеет два состояния устойчивости. Одному из этих состояний присваивается значение «1», а другому — «0». Состояние триггера, а также значение двоичной информации, которая в нем хранится, определяется выходными сигналами: прямым и инверсным. В том случае, когда на прямом выходе установится потенциал, который соответствует логической единице, состояние триггера называется единичным (при этом потенциал на инверсном выходе равен нулю). Если же на прямом выходе нет потенциала, то состояние триггера называется нулевым.

Классифицируют триггеры по следующим признакам:

Классифицируют триггеры по следующим признакам:1. По способу записываемой информации (асинхронные и синхронные).

2. По способу управлением информацией (статистические, динамические, одноступенчатые, многоступенчатые).

3. По способу реализации логических связей (JK-триггер, RS-триггеры, T-тригер, D-триггер и других типов).

Основными параметрами всех типов триггеров являются наибольшее значение длительности входного сигнала, время задержки необходимого для переключения триггера, а также разрешающее время срабатывания.

В этой статье поговорим о таком типе устройств, как RS-триггер. Они бывают двух типов: синхронные и асинхронные.

Асинхронный RS-триггер конструктивно имеет два прямых (R и S) входа. Это устройство функционирует согласно таблице переходов.

Запрещенной для такого триггера является комбинация сигналов на входах устройства, вызывающая состояние неопределенности. Эта комбинация может быть выражена требованием RtSt=0. При минимизации карты Карно выводится закон функционирования триггера, который называют характеристическим уравнением: Q(t+1)=St V R’tQt. При этом RtSt будет равно нулю.

На функциональной схеме изображен RS-триггер асинхронного типа на элементах И-НЕ и во втором исполнении на элементах ИЛИ-НЕ.

Второй тип – синхронный RS-триггер. Такое устройство конструктивно имеет три прямых входа S, R, и C. Отличие триггера синхронного типа от асинхронного заключается в наличии входа синхронизации (С). Он необходим по следующим причинам: ведь на входы устройства (логического элемента) сигналы поступают не всегда одновременно. Это связано с тем, что они проходят через различные типы и количество узлов, которые обладают разной задержкой. Это явление называют «состязанием». В результате таких «состязаний» полученные значения сигналов будут накладываться на предыдущие значения других сигналов. Все это приводит к ложному срабатыванию устройства.

Это явление можно устранить подачей на вход устройства сигналов временного стробирования. А именно: на вход логического элемента, кроме непосредственно информационных сигналов, подаются ключевые синхронизирующие импульсы, к этому моменту информационные входные сигналы успеют зафиксироваться на входах.

Главное условие правильности работы срабатывания логических каскадов в RS-триггере и управляемых ими логических схем – недопустимость одновременного действия сигнала Rt или St, переключающего устройство, и съема информации с выхода Q(t+1) триггера. В связи с этим в потенциальных сериях элементов содержатся только синхронные.

RS-триггер синхронного типа представлен характеристическим уравнением: Q(t+1)=StCt V R’tQt V QtC’t.

На фото изображен RS-триггер синхронного типа на элементах И-НЕ.

Входные логические элементы И-НЕ передают переключающую логическую единицу с информационного входа S или R на необходимые входы асинхронного триггера типа RS с инверсными входами только при условии наличия на синхронном входе (С) сигнала с уровнем логической единицы.

Входные логические элементы И-НЕ передают переключающую логическую единицу с информационного входа S или R на необходимые входы асинхронного триггера типа RS с инверсными входами только при условии наличия на синхронном входе (С) сигнала с уровнем логической единицы.7. Триггеры. Классификация. Rs-, t-, d-, jk-триггер. Способы приема информации: асинхронн

ый и синхронный. Двухступенчатые триггеры.

Триггером называется устройство, имеющее 2 устойчивых состояния, и сохраняющее любое из них сколь угодно долго, после снятия внешнего напряжения. Поэтому говорят, что триггер обладает памятью. Он способен хранить 1 бит информации: 0 или 1.

Различают асинхронные и синхронные триггеры. Синхронизация осуществляется подачей на специальные входы триггеров прямоугольных тактовых импульсов. Они используются по-разному. В одних случаях тактовые импульсы играют роль разрешающего сигнала, и изменение состояния триггера может произойти в любой момент на протяжении действия тактового импульса.

В других случаях схема триггера строится таким образом, что изменения состояния триггера могут происходить лишь в моменты перехода тактового импульса от 0 к 1 или от 1 к 0. Такие триггеры называются триггерами с динамическим входом синхронизации или динамическим управлением.

Асинхронный RS-триггер

На рис. 2 показана схема RS-триггера на логических элементах ИЛИ-НЕ. Название этого триггера происходит от английских слов: Reset – сброс, Set – установка. RS-триггер имеет 2 сигнальных входа R и S и 2 два сигнальных выхода Q и Q.

Рис.2 Асинхронный RS-триггер на элементах ИЛИ-НЕ:

а –схема; б – условное обозначение

Принцип работы.

Если на входах R и S имеется сигнал 0, т.е. R=S=0, то в этом случае схема может находится сколь угодно долго в одном из двух устойчивых состояний: 1) Q = 1 или 2) Q = 0.

Действительно, пусть Q=0. Тогда на вход элемента ИЛИ-НЕ со входом S подаются сигналы 0 и 0. На выходе этого элемента НЕ(0 ИЛИ 0)=1, т.е. НЕ(Q)=1. Этот сигнал подается на вход элемента ИЛИ-НЕ со входом R. На выходе этого элемента НЕ(1 ИЛИ 0)=0, т.е. Q=0. Таким образом, если R=S=0 и Q=0, то внутреннее устройство триггера поддерживает это состояние.

Рассуждая аналогично, получим: если R=S=0 и Q=1, то внутреннее устройство триггера поддерживает это состояние.

Если S = 1 и R = 0, то Q станет равным 1. Действительно, пусть Q=0. Тогда на вход элемента ИЛИ-НЕ со входом S, подаются сигналы 0 и1. На выходе этого элемента НЕ(0 ИЛИ 1)=0, т.е. НЕ(Q)=0. Этот сигнал подается на вход элемента ИЛИ-НЕ со входом R=0. Тогда на выходе этого элемента НЕ(0 ИЛИ 0)=1, т.е. Q=1. Подача сигнала Q=1 на вход элемента ИЛИ-НЕ со входом S не влияет на выходной сигнал НЕ(Q)=0.

Таким образом, схема переключилась в устойчивое состояние Q=1 и НЕ(Q)=0. Вход S называется установочным, так как подача на него 1 устанавливает Q равным 1.

При S=0, R=1 на выходе установится Q=0 и НЕ(Q)=1. Справедливости этого утверждения можно доказать проведя аналогичные рассуждения.

Подачи сигнала 1 на оба входа избегают и считают ее запрещенной, так как при этом схема находится в неопределенном состоянии. Таблица состояний представлена ниже. Здесь R и S входные сигналы, Q – выходной сигнал.

R | S | Q |

0 0 1 1 | 0 1 0 1 | Не изменяется 1 0 Не допускается |

R | S | Q |

1 1 0 0 | 1 0 1 0 | Не изменяется 1 0 Не допускается |

Синхронный RS-триггер

На рис. 4 показана схема синхронного RS-триггера. На вход С подаются синхронизирующие тактовые импульсы. Вследствие двойной инверсии на двух последовательно включенных логических элементах И-НЕ синхронный RS-триггер подобен RS-триггеру на элементах ИЛИ-НЕ с той лишь разницей, что он активен лишь тогда, когда имеются тактовые импульсы.

На рис. 5 приведены временные диаграммы изменения входных сигналов C, R, S и выходного сигнала Q. Как видно, значение выходного сигнала Q может измениться только в моментах времени, когда синхронизирующий сигнал С=1.

Принцип работы

До момента t1 сигналы S=0, R=1 и поэтому триггер находится в нулевом состоянии, т.е. Q=0. В момент времени t1 синхронный сигнал С=1, поскольку S=0, R=1, поэтому схема остается в нулевом состоянии.

Переключение в единичное состояние происходит в момент t2, так как при этом C=1 и S=1, R=0. В момент t3 и t4 схема остается в единичном состоянии, так как сигналы S и R не требуют установления на 0.

Переключение происходит лишь в момент t5, когда происходит тактовый импульс и R=1, S=0. В конце отметим, что обычно взаимодействие отдельных элементов цифровых устройств согласуется по времени с помощью тактовых импульсов.

D-триггер

Схема D-триггера

показана на рис. 6. Он состоит из

синхронного RS-триггера

и инвертора. Триггер управляется

единственным сигналом D,

подаваемым на единственный информационный

вход D.

Благодаря инвертору невозможно

запрещенное соотношение сигналов на

выходах S

и R.

Из временных диаграмм видно, что уровни сигнала D и Q совпадают с некоторой задержкой. Сигнал задерживается до прихода очередного тактового сигнала. В название триггера входит начальная буква английского слова delay, означающего задержку.

Двухтактный RS-триггер

Для многих применений необходимо, чтобы триггер изменял свое состояние не во время действия тактового импульса, а только после его окончания. Иначе говоря, необходимо, чтобы информация на выходе появилась только после того, как входы триггера окажутся запертыми.

Одной из таких схем является двухтактный RS-триггер, состоящий из двух триггеров: главного и вспомогательного (рис. 7). Главный триггер называют ведущим (Master), а вспомогательный – ведомым (Slave). Поэтому такие триггеры также называются MS-триггерами.

Триггеры работают поочередно, вследствие того, что тактовые импульсы на вспомогательный триггер подаются через инвертор.

Вспомогательный триггер переписывает информацию с выхода главного триггера по окончании очередного тактового импульса. Это достигается за счет инвертирования синхронизирующего сигнала вспомогательного триггера. Синхронизирующий сигнал вспомогательного триггера равен 1 только тогда, когда синхронизирующий сигнал главного триггера равен 0.

JK-триггер

Название этого триггера исходит от слов: Jump – переключаться; Keep – сохранить состояние. Этот триггер ведет себя как RS-триггер, за исключением, что устранена неопределенность, возникающая в RS-триггере, когда S=R=1. При S=R=1 JK-триггер инвертирует предыдущее состояние.

Получить JK-триггер можно из RS-триггера, состоящего из главного и вспомогательного RS-триггеров. Для этого на входе главного триггера нужно иметь два S и два R входа. Эти входы должны быть соединены через элемент И, т.е. на вход триггера подается сигнал S (R), если на оба входа S (R) подана лог. 1.

Дополнительные входы S и R должны быть соединены крест-накрест с выходными зажимами вспомогательного триггера (рис. 8).

Принцип работы. Убедимся, что при подаче на входы J и K сигналов, разрешенных для RS-триггера, на выходе JK-триггера получаются такие же сигналы. Например, пусть на выходе Q=1, а на вход подаются сигналы J=0; K=1. В этом случае при действии тактового импульса на главном триггере получим Q1=0, и вспомогательный триггер перепишет это состояние по окончании действия тактового импульса.

Аналогично убеждаемся, что и другие сигналы, разрешенные для RS-триггера, дают такой же результат в JK-триггере.

Остается убедиться в том, что комбинация J=K=1 не приводит к неопределенности. Предположим, что до прихода сигналов J и K триггер находился в единичном состоянии, т.е. Q1=1. В этом случае на входах S главного триггера сигналы S не совпадают, что эквивалентно S=0, а на входах R совпадают, что эквивалентно R=1. Следовательно, Q1=0, что и переписывает вспомогательный триггер на выход. Итак, подача J=K=1 при единичном состоянии JK-триггера переводит его в противоположное состояние.

Jn | Kn | Qn+1 |

0 0 1 1 | 0 1 0 1 | Qn 0 1 Qn |

Таблица состояний JK-триггера приведена ниже. Здесь Qn и Qn+1 означает состояние триггера до прихода n-го тактового импульса и после окончания n-го тактового импульса.

Т-триггер на базе JK-триггераТриггер, переходящий от действия каждого очередного импульса в противоположное состояние, называют Т-триггером.

видно

из схемы, сигнал Т подается на входы J

и K.

Следовательно, если Т=J=K=1,

то на выходе получим противоположный

сигнал.

видно

из схемы, сигнал Т подается на входы J

и K.

Следовательно, если Т=J=K=1,

то на выходе получим противоположный

сигнал.

Причем, выходной сигнал изменяет свое состояние на противоположное в момент окончания синхронизирующего импульса. Это вытекает из принципа работы JK-триггера, состоящего из главного и вспомогательного RS-триггеров. В момент окончания импульса активизируется вспомогательный триггер и происходит передача информации от главного к вспомогательному триггеру.