Принцип работы триггера

В устройстве современной цифровой техники, триггер является одним из наиболее важных элементов, обеспечивающих ее работу. Он не играет роли базовой детали, поскольку его собственная логическая схема очень простая. Принцип работы триггера основан на его способности к запоминанию изменяющихся двоичных значений. На этом принципе было создано большое количество аналогичных устройств. Однако, в основе каждого такого прибора лежит конструкция простейшего RS-триггера.

Как устроен триггер

Благодаря RS-триггерам, стало возможным создание различных вычислительных устройств. Они одинаково используются в игровых приставках и в суперсовременных компьютерах.

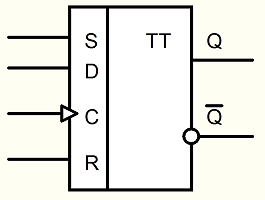

Эти приборы имеют входы установки и сброса, обозначаемые соответственно, как S и R. Кроме того, здесь имеются выходы – прямой и инверсный, обозначаемые символом Q. Чтобы их не перепутать, над знаком инверсного выхода ставится черточка.

Любое из данных устройств является бистабильной системой, соблюдающей какое-либо устойчивое состояние в течение неограниченного времени.

В некоторых случаях, отдельные модификации триггеров могут выполняться с применением элементов 2И – НЕ. Их отличие от базовой модели заключается в возможности перевода в другое состояние или активации путем потенциала, которым обладает логический нуль. При использовании других элементов, активация производится с помощью логической единицы.

На практике, это выглядит следующим образом: когда на вход S подается положительный потенциал, то на прямом выходе образуется высокий потенциал, а на инверсном выходе – низкий. В результате, в ячейке памяти, которой является триггер, отложилась единица. При подаче высокого потенциала на вход R, устройство изменит свое состояние.

Как действует триггер

После того, как питание включено, прибор принимает какое-либо одно устойчивое состояние. В этом и заключается основной принцип работы триггера. Перевести его в другое состояние можно только путем нажатия кнопки другого входа и подачи на него напряжения. Таким образом, устройство может поочередно переводиться из одного устойчивого состояния в другое.

Чтобы преодолеть такой недостаток, как асинхронность, в сложных схемах подобных устройств осуществляется синхронизация с помощью тактовых импульсов, которые воздействуют на всю схему. Для выработки импульсов используется тактовый генератор. Установленное состояние триггера поддерживается сложной логической схемой, устанавливаемой на входе. Поэтому, прибор может изменить свое состояние только после формирования специального разрешительного сигнала.

как работают RS и D устройства, схемы и характеристики

Широкое применение в импульсной технике получил триггер на транзисторах. Чаще всего он используется в качестве счётчика и элемента памяти. Кроме того, в различных приборах логическое устройство заменило собой электромеханическое реле. На основе эпитаксиальных транзисторных триггеров создаются микросхемы, без которых невозможна работа любого современного цифрового прибора.

Широкое применение в импульсной технике получил триггер на транзисторах. Чаще всего он используется в качестве счётчика и элемента памяти. Кроме того, в различных приборах логическое устройство заменило собой электромеханическое реле. На основе эпитаксиальных транзисторных триггеров создаются микросхемы, без которых невозможна работа любого современного цифрового прибора.

Устройство триггера

Триггер по своей схемотехнике очень похож на простейшее электронное устройство — мультивибратор. Но в отличие от него, он имеет два устойчивых положения. Эти состояния обеспечиваются изменениями входного сигнала при достижении им определённого значения. Переход из одного положения в другое называют перебросом. В результате на выходе логического элемента возникает скачок напряжения, форма которого зависит от скорости процессов, проходящих в радиоприборах.

Наибольшее применение получил триггер, работающий на транзисторах. Связанно это со способностью последних работать в ключевом режиме. Биполярный транзистор — это полупроводниковый прибор, имеющий три вывода.

- эмиттер;

- база;

- коллектор.

В грубом приближении транзистор представляет собой два диода, объединённых электрической связью. Состоит он из двух p-n переходов. Название биполярный элемент получил из-за того, что одновременно в нём используются два типа носителей заряда. В триггерных схемах транзистор работает в режиме ключа, суть которого заключается в управлении силой тока коллектора путём изменения значения на базе. При этом коллекторный ток по своей величине превышает базовый.

При таком включении важны лишь токи, а напряжения особой роли не играют. Поэтому при возникновении определённого тока на базе транзистор открывается и пропускает через себя сигнал. Сигнал на коллекторе полупроводникового прибора будет обратным по входному знаку, то есть инвертированным. А значит, когда на базовом выходе будет присутствовать разность потенциалов, на коллекторном она будет равна нулю, и наоборот.

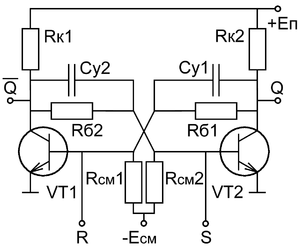

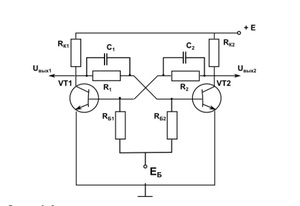

Эта способность транзисторов и используется в триггерах, схема которых построена на двух ключах с перекрёстными обратными связями. Когда используются транзисторные ключи с одинаковой обвязкой, то триггер считается симметричным, в другом же случае — несимметричным.

Принцип работы

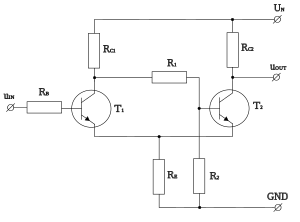

Устойчивые состояния выхода триггера обеспечиваются двумя транзисторными ключами, охваченными положительной обратной связью (ПОС). Такие положения соответствуют состоянию, когда один из транзисторов открыт и находится в режиме насыщения, а второй ключ закрыт. При этом на коллекторе закрытого элемента присутствует разность потенциалов, равная его значению на входе — логическая единица, а на выводе открытого ключа напряжение отсутствует — логический ноль.

Биполярные компоненты при таком включении относительно друг друга всегда будут находиться в противоположном состоянии из-за обратной связи. Через неё один из транзисторов (закрытый) с высоким уровнем напряжения на своём коллекторном выводе обязательно будет поддерживать другой в открытом состоянии.

Если предположить, что после подачи питания на устройство оба транзистора VT1 и VT2 окажутся открытыми, то через время из-за отличия характеристик радиоэлементов, стоящих в их плечах, возникнет перекос в коллекторных токах

Делители, собранные на резисторах R1, R4 и R2, R3, подбираются так, чтобы их коэффициент передачи был меньше единицы. Причём для поддержания уровня сигнала они шунтируются ёмкостью, ускоряющей скорость прохождения лавинообразных процессов и повышающей надёжность состояния.

Таким образом, принцип работы триггера заключается в прохождении следующих процессов. Если на схему подаётся напряжение Ek и Eb, то биполярный ключ VT1 начинает работать в режиме насыщения, а VT2 — отсечки. Импульс, пришедший на базу VT1, приводит к уменьшению величины тока, протекающего через коллектор и увеличению напряжения на переходе коллектор-эмиттер U1ke. Напряжение через С1 и R4 прикладывается к базе VT2. Это приводит к увеличению коллекторного тока на втором ключе и уменьшению напряжения на переходе U2ke, передаваемого через C2 и R3 на базу VT1.

Таким образом, принцип работы триггера заключается в прохождении следующих процессов. Если на схему подаётся напряжение Ek и Eb, то биполярный ключ VT1 начинает работать в режиме насыщения, а VT2 — отсечки. Импульс, пришедший на базу VT1, приводит к уменьшению величины тока, протекающего через коллектор и увеличению напряжения на переходе коллектор-эмиттер U1ke. Напряжение через С1 и R4 прикладывается к базе VT2. Это приводит к увеличению коллекторного тока на втором ключе и уменьшению напряжения на переходе U2ke, передаваемого через C2 и R3 на базу VT1.

Итогом этих процессов станет запирание VT1 и отпирание VT2. Такое состояние останется неизменным, пока на базу VT2 не придёт отрицательный уровень сигнала. Результатом этого будут обратные электрические процессы, и VT1 закроется, а VT2 откроется.

Характеристики приборов

Триггер условно можно назвать «автоматом», способным хранить один бит информации. Простейшего вида прибор имеет два выхода, находящихся по отношению друг к другу в инверсном состоянии. Важные параметры устройства связаны с синхронизацией (тактированием) выходов, зависящей от времени предустановки и выдержки. Первый параметр характеризуется интервалом времени, в течение которого поступает разрешающий фронт синхросигнала, а второй определяется временем нахождения устойчивого состояния в неизменном положении. Ряд других характеристик триггера связывают с сигналом, проходящим через него. К ним относится:

- нагрузочная способность — характеризуется коэффициентом разветвления (Кр) и обозначает способность прибора управлять определённым количеством параллельно подключённых элементов к выходу устройства;

- Ко — коэффициент объединения, обозначает наибольшее число входных напряжений, которые возможно завести на вход прибора;

- tи — минимальная продолжительность входного сигнала, то есть длительность импульса, при котором триггер ещё может перейти в инверсное состояние;

- tзд — коэффициент задержки, указывает на временной промежуток между подачей входного сигнала и появлением напряжения на выходе;

- tр — длительность разрешения, определяется минимальным временем прошедшим между двумя импульсами сигнала на входе и спровоцировавшего переход триггера в другое состояние.

Но наряду с этим выделяют и следующие технические параметры триггеров:

- напряжение на входе — наибольшая величина разности потенциалов, которую может выдержать устройство без повреждения своей внутренней электрической схемы;

- ток потребления — зависит от используемых элементов, обычно не превышает 2 мА;

- разность потенциалов переключения — это минимальное значение, при котором происходит инвертирование выхода;

- ток входа — обозначает минимальное значение необходимое для работы триггера;

- ток выхода — значение тока, появляющееся на выходе и определяемое отдельно для логического нуля и единицы;

- температурный диапазон — интервал, в котором технические параметры устройства не изменяются;

- напряжение гистерезиса — разность амплитуд входного сигнала, приводящая к изменению состояния выхода устройства.

Виды и классификация

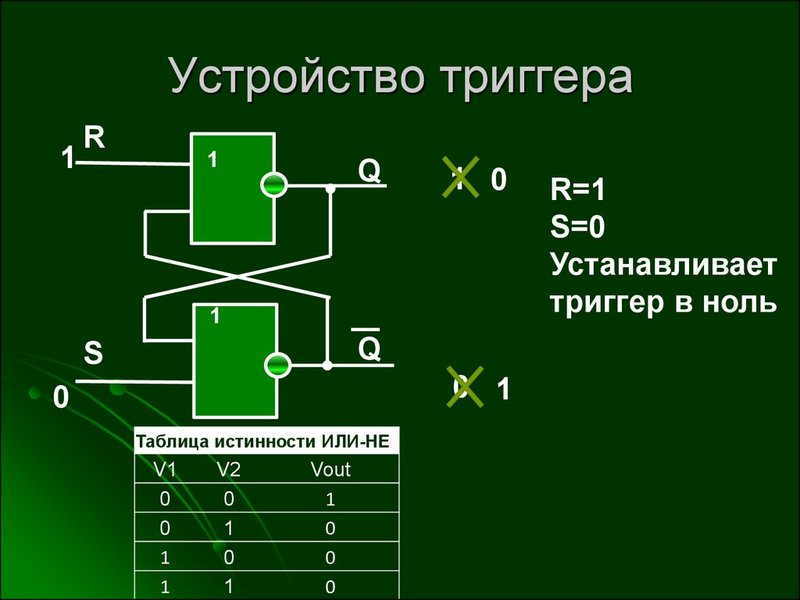

Для работы устройства на вход необходимо подать внешний сигнал, называемый установочным. Форма напряжения, приводящая к появлению логической единицы на выходе триггера, обозначается латинской буквой S (установка), а появлению ноля — R (сброс). Состояние устройства определяется по прямому входу. Для элемента ИЛИ-НЕ активным уровнем считается единица, а И-НЕ — ноль. Одновременная подача R и S приведёт к неопределённому неустойчивому состоянию.

Такой принцип используется для построения элемента памяти. Поэтому все триггеры классифицируются по способу записи информации на асинхронные и синхронные. Первые разделяются по способу управления, а вторые по виду переключения и могут быть одно- или двухступенчатыми. Устройства, зависящие от уровня сигнала, называются триггерами статического управления, а от фронта — динамического.

По типу работы логики триггеры могут быть:

RS — состоящими из двух входов;

RS — состоящими из двух входов;- D — имеющих один информационный вход и схему задержки;

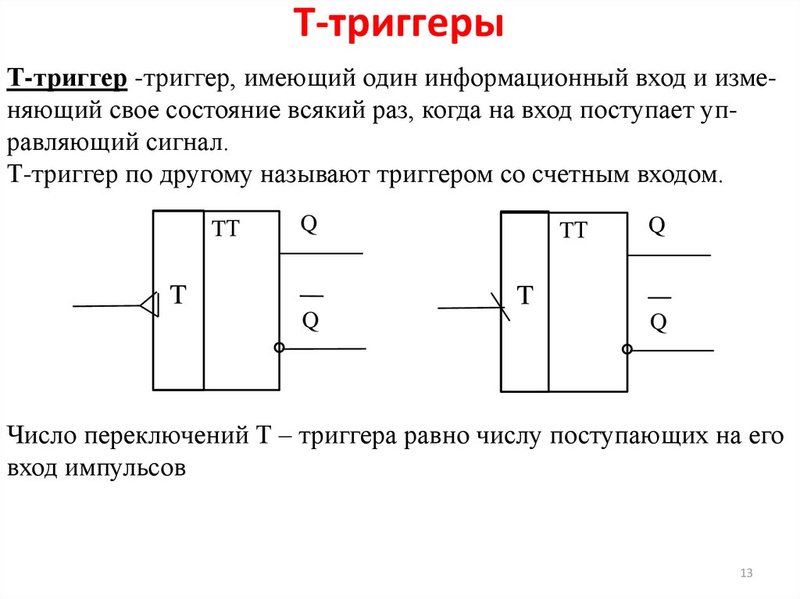

- T — инвертирующих сигнал каждый раз при подаче импульса напряжения на вход;

- JK — универсальными, допускающими одновременную подачу на свои выводы R и S сигналов;

- комбинированными — совмещающими несколько устройств, например, RST-триггер.

Наиболее распространёнными видами триггеров являются D и RS схемы. При этом триггерные устройства разделяются также по числу устойчивых состояний (двоичные, троичные, четверичные и т. д.) и составу логических элементов.

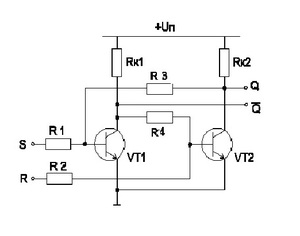

Триггер RS типа

Одной из простейших в цифровой электронике является схема RS-триггера на транзисторах. Внешним воздействием на вход прибора можно установить его выход в нужное устойчивое состояние. Схема устройства представляет собой каскады, выполненные на транзисторах. Вход каждого из них подключается к выходу противоположного. Два состояния определяются присутствием на выходе напряжения, а переход между ними происходит с помощью управляющих сигналов.

Работает схема следующим образом. Если в начальный момент времени VT2 будет закрыт, тогда через сопротивление R3 и коллектор будет течь ток, поддерживающий VT1 в режиме насыщения. Одновременно первый транзистор начнёт шунтировать базу VT2 и резистор R4. Режим отсечки VT2 соответствует значению логической единицы на выходе Q = 1, открытое состояние VT1 нулю, Q = 0. Амплитуда сигнала на коллекторе закрытого ключа определяется выражением: Uз = U * R3 / (R2+R3).

Работает схема следующим образом. Если в начальный момент времени VT2 будет закрыт, тогда через сопротивление R3 и коллектор будет течь ток, поддерживающий VT1 в режиме насыщения. Одновременно первый транзистор начнёт шунтировать базу VT2 и резистор R4. Режим отсечки VT2 соответствует значению логической единицы на выходе Q = 1, открытое состояние VT1 нулю, Q = 0. Амплитуда сигнала на коллекторе закрытого ключа определяется выражением: Uз = U * R3 / (R2+R3).

Для инверсии сигнала необходимо на вход R или S подать импульс. При этом если S = 1, то и Q = 1, а если R=1, то на выходе будет ноль. При значениях R1 = R2 и R3 = R4 триггер называется симметричным. Особенностью работы устройства является способность удерживать установленное состояние между импульсами R и S, что и используется для создания на нём элементов памяти.

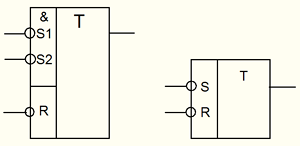

На схемах RS-триггер обозначается в виде прямоугольника с подписанными входами S и R, а также возможными состояниями выхода. Прямой подписывается символом Q, а инверсный – Q. Информация может поступать на входы непрерывным потоком или только при появлении синхроимпульса. В первом случае устройство называют асинхронным, а во втором – синхронным (трактируемым).

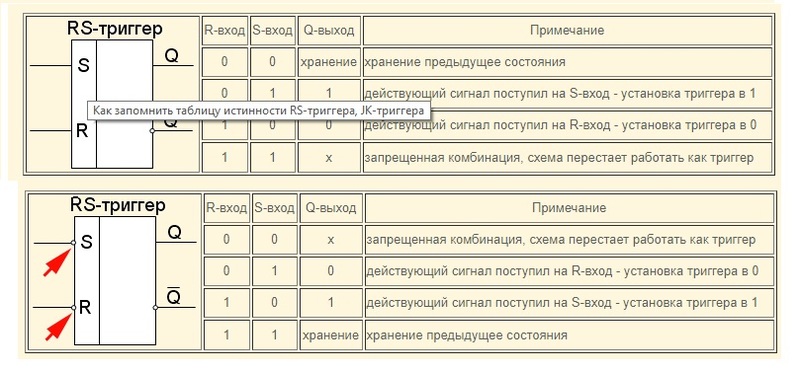

Работа устройства наглядно описывается с помощью таблицы истинности.

Она наглядно показывает всевозможные комбинации, которые могут возникнуть на выходе прибора. Такая таблица составляется отдельно для триггера с прямыми входами и инверсными. В первом случае действующий сигнал равен единице, а во втором — нулю.

Она наглядно показывает всевозможные комбинации, которые могут возникнуть на выходе прибора. Такая таблица составляется отдельно для триггера с прямыми входами и инверсными. В первом случае действующий сигнал равен единице, а во втором — нулю.

Схема D-trigger

Управление логическими элементами в приборе такого типа осуществляется с помощью входов, которые разделяются на информационные и вспомогательные. Первый фиксирует приходящий импульс и в зависимости от формы переводит триггер в устойчивое то или иное состояние. Вспомогательный вход предназначен для синхронной работы.

Английская буква D в названии обозначает, что устройство является триггером задержки (delay). Эта задержка выражается в том, что приходящий импульс подаётся на вход не сразу, а через один такт. Определяет её частота импульсов синхронизации.

На схемах D-триггер на транзисторах обозначается также в виде прямоугольника, но входы триггера подписываются как D и C. Состояние устройства определяется по форме импульса, в частности срезу, приходящему на вход C, и импульсом синхронизации, поступающим на D. Но если на C будут приходить синхроимпульсы, а сигнал на входе D не будет изменяться, то выход останется без изменений.

Таблица истинности для логического элемента выглядит следующим образом:

Использование RS и D триггеров достаточно распространено из-за простоты, универсальности и удобства построения на них логических схем. Эти элементы являются важными составляющими для создания цифровых микросхем, используются в качестве регистров сдвига и хранения.

RS-триггер. Принцип работы и его типовая схема на логических элементах.

Устройство и принцип работы RS-триггера

Одним из важнейших элементов цифровой техники является триггер (англ. Trigger — защёлка, спусковой крючок).

Сам триггер не является базовым элементом, так как он собирается из более простых логических схем. Семейство триггеров весьма обширно. Это триггеры: T, D, C, JK, но основой всех является самый простой RS-триггер.

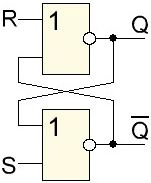

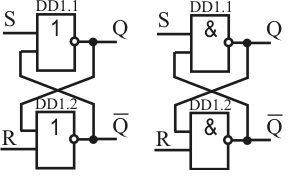

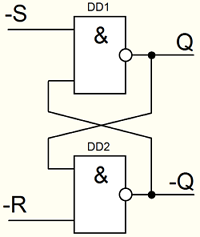

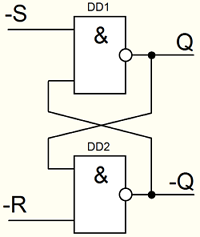

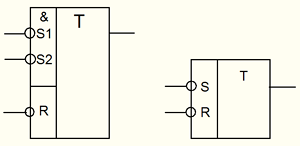

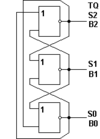

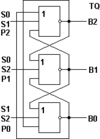

Без RS триггеров невозможно было бы создание никаких вычислительных устройств от игровой приставки до суперкомпьютера. У триггера два входа S (set) — установка и R (reset) — сброс и два выхода Q-прямой и Q— инверсный. Инверсный выход имеет сверху чёрточку. Триггер бистабильная система, которая может находиться в одном из двух устойчивых состояний сколь угодно долго. На рисунке показан RS-триггер выполненный на элементах 2ИЛИ – НЕ.

Точно так же триггер может быть выполнен и на элементах 2И – НЕ.

Единственная разница это то, что триггер на элементах И – НЕ активируется, то есть переводится в другое состояние потенциалом логического нуля. Триггер, собранный на элементах ИЛИ – НЕ активируется логической единицей. Это определяется таблицей истинности логических элементов. При подаче положительного потенциала на вход S мы получим на выходе Q высокий потенциал, а на выходе Q низкий потенциал. Тем самым мы записали в триггер, как в ячейку памяти, единицу. Пока на вход R не будет подан высокий потенциал, состояние триггера не изменится.

На принципиальных схемах триггер изображается следующим образом.

Два входа R и S, два выхода прямой и инверсный и буква Т означающая триггер.

Хорошо отображает принцип работы RS-триггера несложная схема, собранная на двух элементах 2И – НЕ. Для этого используется микросхема 155ЛА3, которая содержит четыре таких элемента. Нумерация на схеме соответствует выводам микросхемы. Напряжение питания +5V подаётся на 14 вывод, а минус подаётся на 7 вывод микросхемы. После включения питания триггер установится в одно из двух устойчивых состояний.

Исходя из того, что сопротивление переходов транзисторов логических элементов не может быть абсолютно одинаковым, то триггер после включения питания, как правило, принимает одно и то же состояние.

Допустим, после подачи питания у нас горит верхний по схеме светодиод HL1. Можно сколько угодно нажимать кнопку SB1 ситуация не изменится, но достаточно на долю секунды замкнуть контакты кнопки SB2 как триггер поменяет своё состояние на противоположное. Горевший светодиод HL1 погаснет и загорится другой — HL2. Тем самым мы перевели триггер в другое устойчивое состояние.

На данной схеме всё достаточно условно, а на реальном триггере принято считать, что если на прямом выходе «Q» высокий уровень то триггер установлен, если уровень низкий то триггер сброшен.

Основной недостаток рассматриваемого триггера это, то, что он асинхронный. Другие более сложные схемы триггеров синхронизируются тактовыми импульсами общими для всей схемы и вырабатываемые тактовым генератором. Кроме того сложная входная логика позволяет держать триггер в установленном состоянии до тех пор пока не будет сформирован сигнал разрешения смены состояния триггера.

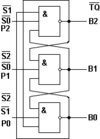

RS-триггер может быть и синхронным, но двух логических элементов для этого мало.

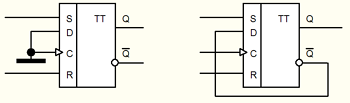

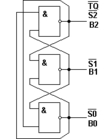

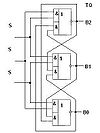

На рисунке изображена схема синхронного RS-триггера. Такой триггер может быть собран на микросхеме К155ЛА3, которая содержит как раз четыре элемента 2И – НЕ. В данной схеме переключение триггера из одного состояния в другое может быть осуществлено только в момент прихода синхроимпульса на вход «C«.

На рассмотренной выше схеме переключение триггера осуществляется с помощью кнопок. Такой вариант используется достаточно часто и именно для кнопочного управления какой-либо аппаратурой. В электронике существует понятие «дребезг контактов» то есть, когда мы нажимаем кнопку, на вход устройства проникает целый пакет импульсов, который может привести к серьёзным нарушениям в работе. Использование RS-триггера позволяет избежать этого.

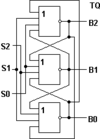

Благодаря своей простоте и недорогой стоимости RS-триггеры широко применяются в схемах индикации. Часто для повышения надёжности и устранения возможности случайного срабатывания RS-триггер собирается по так называемой двухступенчатой схеме. Вот схема.

Здесь можно видеть два совершенно одинаковых синхронных RS-триггера, только для второго триггера синхроимпульсы инвертируются. Первый триггер в связке называют M (master) — хозяин, а второй триггер называется S (slave) — раб.

Допустим на входе «С» высокий потенциал. М-триггер принимает информацию, но низкий потенциал на входе синхронизации S-триггера блокирует приём информации. После того как потенциал поменялся на противоположный информация из M-триггера записывается в S-триггер, но приём информации в M-триггер блокируется.

Такая двухступенчатая система намного надёжнее обычного RS-триггера. Она свободна от случайных срабатываний.

Для более наглядного изучения работы RS-триггера рекомендую провести эксперименты с RS-триггером.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Триггеры. Принцип работы | HomeElectronics

Всем доброго времени суток! Сегодняшний мой пост посвящён цифровым микросхемам, которые имеют память. Подобно тому, как человек помнит события из своей жизни, так и эти микросхемы могут долго хранить заложенную в них информацию, а когда необходимо выдавать её.

Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

Внутреннее устройство триггера

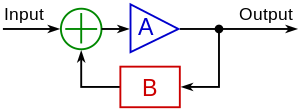

Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

Схема триггерной ячейки на логических элементах (RS триггер).

Схема на рисунке выше представляет простейший триггер (или триггерная ячейка), который имеет два входа и два выхода. Входы триггера реагируют на низкий логический уровень: вход R – сброс (англ. Reset – сброс) и вход S – установка (англ. Set – установка), выходы: прямой Q (англ. Quit – выход) и инверсный –Q.

Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности.

Таблица истинности триггерной ячейки (RS триггер).| Входы | Выходы | ||

| R | S | Q | -Q |

| 0 | 0 | Не определено | |

| 0 | 1 | 0 | 1 |

| 1 | 1 | Без изменений | |

| 1 | 0 | 1 | 0 |

Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

- RS триггеры – самый простой и редко используемый триггер, имеет обозначение ТР;

- JK триггер – имеет сложное управление, обозначение ТВ;

- D триггер – самый распространённый и имеет сложность среднюю, обозначение ТМ;

RS триггеры

Рассмотрим принцип работы RS триггера возьмём микросхему К555ТР2.

Обозначение RS триггера К555ТР2

Данная микросхема имеет 4 RS триггера, два из которых имеют по одному R входу и одному S входу, а два других – по одному R входу и по два S входа, объединенных по функции И. Все 4 RS триггера данной микросхемы имеют по одному прямому выходу. Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний.

JK триггер

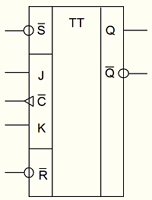

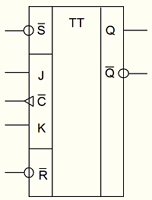

Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы.

Обозначение JK триггера К555ТВ9.

Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С.

Таблица истинности JK триггера.| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 0 | 1 | Х | Х | Х | 1 | 0 |

| 1 | 0 | Х | Х | Х | 0 | 1 |

| 0 | 0 | Х | Х | Х | Не определено | |

| 1 | 1 | 1→0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1→0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1→0 | 0 | 0 | Не изменяется | |

| 1 | 1 | 1→0 | 1 | 1 | Меняется на противоположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | 0 | Х | Х | Не изменяется | |

| 1 | 1 | 0→1 | Х | Х | Не изменяется | |

Принцип работы JK триггера следующий. Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться.

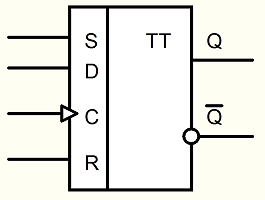

D триггер

D триггер является самым используемым, а по управлению он занимает промежуточное положение между RS триггером и JK триггером. Представителем D триггеров является микросхема К555ТМ2.

Обозначение D триггера микросхемы К555ТМ2

В составе данной микросхемы содержится два D триггера, которые имеют два входа сброса и установки R и C, информационный вход D (англ. Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера.

Таблица истинности D триггера

| Входы | Выходы | ||||

| -S | -R | C | D | Q | -Q |

| 0 | 1 | X | X | 1 | 0 |

| 1 | 0 | X | X | 0 | 1 |

| 0 | 0 | X | X | Не определено | |

| 1 | 1 | 0→1 | 0 | 0 | 1 |

| 1 | 1 | 0→1 | 1 | 1 | 0 |

| 1 | 1 | 0 | Х | Не меняется | |

| 1 | 1 | 1 | Х | Не меняется | |

| 1 | 1 | 1→0 | Х | Не меняется | |

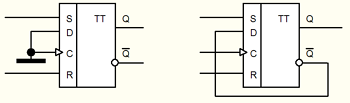

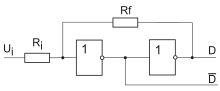

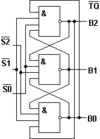

D триггер является наиболее универсальным потому, что данным триггером можно заменить все остальные RS триггеры и JK триггеры. Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров

Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа).

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

Триггер Шмитта — Википедия

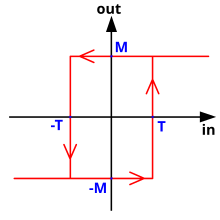

Петля гистерезиса идеального триггера Шмитта с равными по модулю порогами переключения −T, T{\displaystyle -T,\ T} и равными по модулю выходными сигналами −M, M{\displaystyle -M,\ M}. При входном сигнале, находящемся между порогами переключения, выходной сигнал триггера Шмитта определяется предысторией.

Петля гистерезиса идеального триггера Шмитта с равными по модулю порогами переключения −T, T{\displaystyle -T,\ T} и равными по модулю выходными сигналами −M, M{\displaystyle -M,\ M}. При входном сигнале, находящемся между порогами переключения, выходной сигнал триггера Шмитта определяется предысторией.Три́ггер Шми́тта — двухпозиционный релейный (переключающий) элемент, статическая характеристика которого имеет зону неоднозначности — петлю гистерезиса.

В узком смысле триггер Шмитта — электронное устройство, в более широком смысле — любой переключающий элемент с гистерезисом, реализованный на любых физических принципах — электромеханические устройства, пневматические, чисто механические.

Фазовая траектория (статическая характеристика) триггера Шмитта представляет собой характеристику переключателя, но с прямоугольной петлёй гистерезиса. Неоднозначность статической характеристики при входном сигнале, величина которого находится между порогами переключения, позволяет утверждать, что триггер Шмитта, как и другие триггеры, обладает свойством памяти — его состояние в зоне неоднозначности (состояние хранения записанной информации) определяется предысторией — ранее действовавшим входным сигналом.

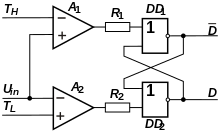

Схемотехнически электронный триггер Шмитта представляет из себя объединение двух устройств: двухпорогового компаратора и явно или неявно присутствующего RS-триггера.

В реализации, называемой «прецизионный триггер Шмитта» или, иногда, называемый более длинно — «прецизионный триггер Шмитта с RS-триггером», двухпороговый компаратор и RS-триггер присутствуют явно, причём двухпороговый компаратор выполнен в виде двух однопороговых компараторов с разными порогами[1][2][3].

В иной реализации, называемой «Триггер Шмитта с обратной связью» или «Компаратор с гистерезисом», двухпороговый компаратор схемно образуется из однопорогового компаратора с переключаемой посредством положительной обратной связи порогом, причём в одном состоянии компаратора формируется уровень верхнего порога переключения, а в другом — уровень нижнего порога переключения. Эта же положительная обратная связь организует из того же одного компаратора и неявный RS-триггер.

Электронные триггеры Шмитта используются для восстановления двухуровневого цифрового сигнала, искажённого в линиях связи помехами и искажениями, в фильтрах дребезга контактов, в качестве двухпозиционного регулятора в системах автоматического регулирования, в двухпозиционных стабилизаторах-регуляторах напряжения, в релаксационных автогенераторах. Триггер Шмитта выделяется в семействе электронных триггеров: он имеет один аналоговый вход и один выход с двумя выходными уровнями.

Существуют электромеханические и механические устройства с гистерезисом, по сути являющиеся функциональными аналогами триггера Шмитта, образуемым механически перемещаемыми деталями. Например, обычное электромеханическое реле является неэлектронным функциональным аналогом триггера Шмитта. Такие триггеры применяются в регуляторах температуры холодильников различных электронагревательных приборов (утюгов, масляных обогревателей, в стабилизаторах давления компрессоров и т. п.), в автоматическом оружии.

Электронный триггер Шмитта, реализованный на электровакуумных триодах, изобрёл американский биофизик и инженер Отто Герберт Шмитт в 1934 году, будучи в то время студентом-практикантом. В 1937 году Шмитт описал его в своей докторской диссертации под названием «термионный триггер», написанной им по результатам изучения распространения нервных импульсов в нервной системе кальмаров[4].

Прецизионный триггер Шмитта[править | править код]

Триггер Шмитта представляет собой RS-триггер, управляемый одним входным аналоговым сигналом, с двумя разными напряжениями переключения в два различных состояния. Прецизионным его называют потому, что пороги переключения задаются независимо и точность этих порогов зависит только от точности порогов переключения входных одновходовых компараторов. Обычно состояния выходного сигнала триггера обозначаются символами «0» и «1», причём, напряжение переключения в «1» выше напряжения переключения в «0». При входном напряжении находящемся между напряжениями переключения триггер Шмитта находится в состоянии хранения ранее записанной в него информации и его выходной сигнал определяется предысторией изменения входного сигнала.

Триггеры Шмитта с RS-триггером не имеют обратной связи с выхода на аналоговый вход. Они состоят из двухпорогового компаратора, в котором сравниваются два раздельно устанавливаемых напряжения порогов переключения с входным сигналом. Переключение триггера в состояние «0» и в состояние «1» происходит от выходных сигналов однопороговых компараторов, которые подаются на асинхронные входы установки и сброса S и R RS-триггера[1][2][3].

Триггер Шмитта с обратной связью[править | править код]

Триггер Шмитта на компараторе с положительной обратной связью.

Триггер Шмитта на компараторе с положительной обратной связью.A{\displaystyle A} — однопороговый компаратор с ограниченными на уровне U+, U−{\displaystyle U_{+},\ U_{-}} выходными напряжениями в двух разных состояниях;

B{\displaystyle B} — делитель напряжения в петле положительной обратной связи.

В вариантах триггера с обратной связью, обратная связь используется и для переключения напряжения порога сравнения в обычном компараторе, который имеет порог переключения равным нулю, превращая его одновременно в двухпороговый компаратор с разными порогами и в RS-триггер на одном и том же однопороговом компараторе. При высоком напряжении U+{\displaystyle U_{+}} (состояние логической «1») на выходе компаратора, обратная связь снижает напряжение порога переключения по входу Input, так как суммируется входным сумматором с входным сигналом, для того, чтобы напряжение на входе компаратора, равное выходному напряжению сумматора, стало равным нулю, входное напряжение должно стать отрицательным и равным по модулю выходному напряжению компаратора, находящегося в состоянии логической «1». Соответственно, при низком напряжении на выходе компаратора U−{\displaystyle U_{-}} (состояние логического «0») на выходе компаратора обратная связь увеличивает напряжение порога переключения.

В такой структуре затруднены раздельная и независимая установка порогов срабатывания[5]. Кроме того, при входном напряжении, значение которого лежит между порогами переключения, то есть в зоне неоднозначности, принудительная установка триггера в заданное состояние требует применения дополнительных компонентов.

Варианты исполнения триггеров Шмитта[править | править код]

Прецизионный триггер Шмитта[править | править код]

Триггер Шмитта с асинхронным RS-триггером и двумя однопороговыми компараторами

Триггер Шмитта с асинхронным RS-триггером и двумя однопороговыми компараторамиПрецизионный триггер Шмитта, иногда более длинно называемый «прецизионным триггером Шмитта с RS-триггером», состоит из двухпорогового компаратора, выполненного на двух обычных компараторах с двухуровневым выходом (двоичным выходом), который делит весь диапазон входных напряжений на три части — первый — ниже нижнего порога, второй — между порогами и третий — выше верхнего порога, и RS-триггера, переключение которого происходит при выходе входного напряжения из второго диапазона — между нижним и верхним порогами переключения[1][2][3].

Существует ряд микросхем разных изготовителей, содержащих в себе два аналоговых однопороговых компаратора и логические вентили для организации внешними перемычками между выводами в микросхеме встроенного RS-триггера, например, микросхема NE521[6].

Другая популярная микросхема, интегральный таймер 555, также выпускаемый очень многими изготовителями микросхем (отечественные аналоги микросхемы — КР1006ВИ1, КР1008ВИ1), содержит в себе все элементы прецизионного триггера Шмитта. Так, при объединении входов микросхемы «THRES» и «TRIG» будет выполнять функцию инвертирующего триггера Шмитта. Недостаток этой микросхемы в случае применения её в качестве триггера Шмитта — невозможность произвольного задания порогов переключения, которые жестко определяются внутренним резистивным делителем напряжения и составляют приблизительно треть от напряжения питания микросхемы для нижнего порога переключения и 2/3 для верхнего порога переключения.

Прецизионный триггер Шмитта удобен для построения схем двухпозиционных ключевых стабилизаторов напряжения, температуры, уровня жидкости, оборотов двигателей, реле-регуляторов и др.[7]

Электромеханическим аналогом прецизионного триггера Шмитта с ключевым исполнительным элементом является электромеханическое реле.

Другими электромеханическими или механическими аналогами прецизионного триггера Шмитта являются переключатели с тремя положениями рычага управления и с двумя выходными состояниями, в которых рычаг управления в состоянии хранения записанной в RS-триггер информации находится в среднем положении, а переключение происходит только при отклонении рычага управления от среднего положения. Например, джойстик в некоторых мобильных телефонах.

Программная реализация триггера Шмитта[править | править код]

В «программном прецизионном триггере Шмитта» двумя однопороговыми компараторами являются два оператора ЕСЛИ-ТО, а состояние RS-триггера хранит некоторая переменная, например, нулевой разряд (бит) целой переменной, или некоторая булевая переменная, принимающая значения «ЛОЖЬ» и «ИСТИНА».

При логических элементах с одинаковыми временами задержки любой аппаратный триггер Шмитта имеет значительно большее быстродействие (tзадержки ≈ 3dt, где dt — время задержки в одном логическом вентиле), чем программный. Кроме этого, в аппаратном триггере Шмитта процесс сравнения происходит одновременно по двум цепочкам двумя компараторами параллельно, а в программном триггере Шмитта в однопоточных процессорах две операции сравнения с двумя порогами происходят последовательно. Время исполнения кода программного триггера Шмитта несколько увеличивается, если язык программирования не поддерживает безусловный переход на метку, в этом случае с данными Вход < Нижний_порог исполняется второй оператор сравнения. Если язык программирования поддерживает безусловный переход, то в случаях при Вход < Нижний_порог обходятся проходы второго оператора ЕСЛИ, как показано в примере псевдокода.

Пример псевдокода неинвертирующего триггера Шмитта:

Вход, Верхний_порог, Нижний_порог - вещественные; //Верхний_порог > Нижний_порог Триггер - булевая; Задание значений Верхний_порог, Нижний_порог; Триггер := 0; //Обозначения булевой переменной: 0 и 1 это "ЛОЖЬ" и "ИСТИНА" соответственно ЦИКЛ //Например, тут можно вставить условие выхода из цикла ВВОД Вход; ЕСЛИ Вход < Нижний_порог ТО Триггер := 0; ВЫВОД Триггер; ПЕРЕХОД НА METKA1; КОНЕЦ ЕСЛИ; ЕСЛИ Вход > Верхний_порог ТО Триггер := 1; ВЫВОД Триггер; КОНЕЦ ЕСЛИ; МЕТКА1: КОНЕЦ ЦИКЛА;

Триггер Шмитта с обратной связью на аналоговый вход[править | править код]

На аналоговых элементах[править | править код]

Пример реализации триггера Шмитта на двух транзисторах приведён на рисунке. В этой схеме каскад на транзисторе T1 является простейшим компаратором. Положительная обратная связь осуществляется с эмиттера второго транзистора на эмиттер первого транзистора, для сигнала обратной связи первый транзистор работает в режиме с общей базой.

В современной аналоговой схемотехнике триггеры Шмитта обычно выполняются на операционном усилителе в режиме компаратора, охваченного резистивной положительной обратной связью, двухуровневый выходной сигнал которого, по этой же обратной связи, с некоторым запаздыванием, определяемым сопротивлением резистора обратной связи и распределённой и паразитной входной ёмкостью компаратора, изменяет напряжение сравнения компаратора. В результате этого для входного напряжения компаратор становится двухпороговым, с двумя разными входными напряжениями переключения в два состояния. Благодаря положительной обратной связи в статической характеристике устройства формируется петля гистерезиса, то есть устройство приобретает свойства триггера.

В триггере Шмитта с обратной связью после переключения триггера существует интервал, на котором действует предыдущее значение напряжения сравнения до прихода сигнала переключения напряжения сравнения по цепи обратной связи. Если на этом интервале произойдёт внезапное изменение входного сигнала в противоположную сторону, то триггер переключится по предыдущему напряжению сравнения, то есть преждевременно.

На цифровых логических элементах[править | править код]

Триггер Шмитта, выполненный на логических элементах «НЕ»

Триггер Шмитта, выполненный на логических элементах «НЕ»Простейшая реализация триггера Шмитта на цифровых логических элементах в качестве аналоговых инвертирующих усилителей — это два последовательно включенных логических инвертора, которые в таком включении образуют аналоговый однопороговый компаратор с порогом переключения приблизительно равным половинному напряжению питания. Образованный двумя элементами компаратор охвачен резистивной обратной связью, выходной сигнал которого через обратную связь изменяет пороговое напряжение переключения для входного сигнала.

Длительность фронта и скорость нарастания выходного сигнала этого устройства не зависит от скорости нарастания входного сигнала и является величиной постоянной, зависящей от быстродействия логических вентилей.

Использование логических вентилей в качестве аналогового компаратора ухудшает точность, стабильность и воспроизводимость порогов переключения, а резистивная обратная связь совместно с паразитными и входной ёмкостями несколько уменьшает быстродействие устройства.

Для восстановления искажённого при передаче двухуровневого сигнала[править | править код]

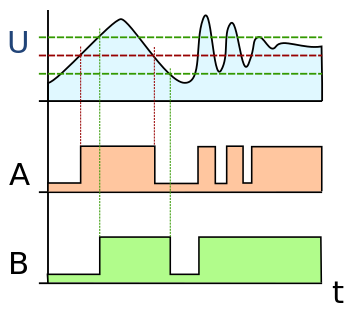

Сравнение работы однопорогового компаратора и двухпорогового триггера Шмитта для восстановления искажённого в линии передачи двухуровневого двоичного сигнала.

Сравнение работы однопорогового компаратора и двухпорогового триггера Шмитта для восстановления искажённого в линии передачи двухуровневого двоичного сигнала.U — входной искажённый сигнал, красной пунктирной линией показан порог переключения однопорогового компаратора, зелёными пунктирными линиями пороги переключения триггера Шмитта;

A — выходной сигнал компаратора;

B — выходной сигнал триггера Шмитта.

Принцип восстановления искажённого двухуровневого сигнала показан на рисунке. Предположим, что высокий уровень сигнала кодирует логическую «1», низкий уровень — логический «0». Допустим, неискажённое напряжение логической «1» немного превышает верхний порог триггера Шмитта, но при искажении в линии от помех верхний уровень на конце линии колеблется. Пусть в линию передаётся только логическая «1», если напряжение на выходе линии снизится от воздействия помехи ниже порога переключения компаратора, то на выходе компаратора возникнут ложные значения, отвечающие логическому «0».

На выходе же триггера Шмитта ложные логические «0» при передаваемой логической «1» появятся только в том случае, если уровень сигнала на выходе канала передачи опустится ниже нижнего порога переключения триггера Шмитта. Аналогично действует защита от помех при передаче логического «0».

Должным выбором уровней сигнала и порогов переключения при априорно известном уровне помех в канале передачи удаётся существенно снизить вероятность искажения передаваемой информации.

В фильтрах дребезга электромеханических ключей[править | править код]

При замыкании контактов у электромеханических коммутирующих устройств — переключателей, кнопок, электромагнитных реле и др. возникает дребезг контактов — многократные неконтролируемые замыкания и размыкания цепи, вызванные подпрыгиванием контактов при соударениях. Во многих случаях дребезг некритичен, например, в выключателях электропитания, но во многих цифровых устройствах дребезг недопустим, так как может вызывать многократные нежелательные переключения состояний триггеров цифрового устройства.

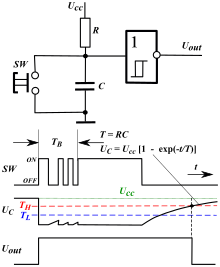

Для исключения вредного эффекта дребезга в таких устройствах применяют различные фильтры дребезга. Один из вариантов такого фильтра с инвертирующим триггером Шмитта и фильтром нижних частот (ФНЧ) на его входе приведен на рисунке.

При ненажатой кнопке SW{\displaystyle SW} напряжение на конденсаторе C{\displaystyle C} примерно равно напряжению питания, поэтому напряжение UC{\displaystyle U_{C}} на входе триггера превышает его верхний порог, и, так как триггер инвертирующий, на его выходе Uout{\displaystyle U_{out}} будет низкое напряжение, близкое к напряжению «земли», или состояние логического «0».

При нажатии на кнопку конденсатор очень быстро разрядится до нулевого напряжения, на входе триггера напряжение станет ниже нижнего порога переключения TL{\displaystyle T_{L}} и на выходе триггера установится напряжения близкое к напряжению питания — состояние логической «1».

Постоянная времени T=RC{\displaystyle T=RC} RC{\displaystyle RC}-цепи выбрана заведомо больше времени успокоения дребезга TB{\displaystyle T_{B}}, поэтому конденсатор во время дребезга, когда цепь кнопки кратковременно размыкается, не успевает зарядиться до нижнего порога переключения триггера и на выходе триггера удерживается стабильное состояние логической «1».

После отпускания кнопки конденсатор через резистор постепенно заряжается, и при достижении напряжения на нём выше верхнего порога переключения триггера выход триггера переходит в состояние логического «0».

В ключевых стабилизаторах напряжения на триггере Шмитта[править | править код]

В ключевых стабилизаторах напряжения с управлением ключом от триггера Шмитта используется гистерезисные свойства триггера Шмитта — при превышении выходным напряжением стабилизатора выше верхнего порога переключения триггера, триггер размыкает электронный ключ, что вызывают постепенное, за счёт конденсатора выходного фильтра снижение выходного напряжения, после достижения выходным напряжением нижнего порога переключения триггер переключается и снова замыкает ключ. Далее процесс повторяется. При этом периодическом процессе выходное напряжение колеблется между порогами переключения триггера Шмитта.

Электромагнитное реле, используемое как триггер Шмитта в разных регуляторах[править | править код]

Электромеханические реле являются триггером Шмитта с ключевым исполнительным элементом.

Обычное электромагнитное реле обладает петлёй гистерезиса в координатах ток обмотки реле — его состояние так как ток срабатывания реле всегда превышает ток удержания, поэтому в диапазоне токов между током срабатывания и тока удержания имеется неоднозначность состояния реле, в этом диапазоне состояние реле зависит от предыстории.

Электромагнит реле вместе с подвижным якорем являются по сути двухпороговым компаратором, который делит весь диапазон токов обмотки реле на три поддиапазона: ток ниже тока отпускания, ток выше тока удержания, но ниже тока срабатывания — аналог состояние хранения двоичного RS-триггера, и ток выше тока срабатывания.

Контактные группы реле являются ключом, имеющим два устойчивых состояния: «контакты разомкнуты» и «контакты замкнуты».

Фактически реле содержит в себе все функциональные элементы ключевого стабилизатора (регулятора) напряжения на триггере Шмитта: RS-триггер и ключевой переключатель, поэтому оно часто применяется в различных устройствах, называемых реле-регуляторами, причем такие регуляторы пригодны для двухпозиционного регулирования величин различной физической природы, например, температуры, давления и др.

В автомобильных ключевых стабилизаторах напряжения генератора[править | править код]

В автомобильных генераторах постоянного тока, в ключевых стабилизаторах напряжения с триггером Шмитта, реле является и прецизионным триггером Шмитта и ключевым управляющим элементом, шунтирующим дополнительное последовательное сопротивление в обмотке возбуждения генератора, а генератор является объектом управления.

В автомобильных генераторах переменного тока, в ключевых стабилизаторах напряжения на триггере Шмитта.

В различных терморегуляторах[править | править код]

В терморегуляторах холодильников[править | править код]

В механическом регуляторе-стабилизаторе температуры давление газа внутри термодатчика сильфонного типа поступает на пневмомеханический двухпороговый компаратор с перенастраивымым порогом срабатывания.

Пневмомеханический двухпороговый компаратор делит весь диапазон входных давлений газа внутри термодатчика сильфонного типа на три поддиапазона: давление включения, давление удержания включенного состояния и давление отключения. Давление удержания является состоянием хранения записанной в механический RS-триггер информации.

Пневмомеханический двухпороговый компаратор переключает и механический RS-триггер и порог срабатывания пневмомеханического двухпорогового компаратора. Механический RS-триггер управляет электрическим выключателем, контакты которого включают и выключают электродвигатель компрессора, либо нагревательный элемент в холодильниках абсорбционного типа.

Таким образом, механический терморегулятор холодильника является электромеханическим стабилизатором температуры с механическим триггером Шмитта с переключаемым порогом срабатывания и с контактной группой работающей как ключ и работает подобно ключевому стабилизатору напряжения на триггере Шмитта.

Другие применения в качестве терморегуляторов[править | править код]

Также электромеханические аналоги триггера Шмитта используются в терморегуляторах электрических утюгов, духовых кухонных шкафов, электроплит и электропечей, в биметаллических реле регуляторов температуры, например, бытовых отопительных котлов, в терморегуляторах бойлеров и электрических чайников с функцией бойлера.

- Калабеков Б. А. Цифровые устройства и микропроцессорные системы — М.: Телеком, 2000 г.

- Потёмкин И. С. Функциональные узлы цифровой автоматики — М.: Энергоатомиздат, 1988 г., c. 166—206.

JK-триггер. Чем он отличается от остальных триггеров?

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

На рисунке видно, что JK-триггер имеет пять входов, в том числе прямой Q и инверсный выходы Q.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С — тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер «сбросится» в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод — это корпус, а 14 вывод — это напряжение питания +5V. На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или «корпус».

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто «висит» в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Троичный триггер — Википедия

Троичный триггер (ternary trigger, ternary latch, ternary flip-flop) — электронное, механическое, пневматическое, гидравлическое, оптическое или другое устройство, имеющее три устойчивых состояния, возможность переключения из любого одного из трёх устойчивых состояний в любое из двух других устойчивых состояний и возможность определения, в каком из трёх устойчивых состояний находится это устройство. Например, троичная ячейка памяти, с возможностью записи и чтения (записанных) троичных кодов (чисел) в ней.

Графы переходов в физических троичных системах 3L LCT, 2B BCT и 3B BCT

Графы переходов в физических троичных системах 3L LCT, 2B BCT и 3B BCTГраф троичных триггеров в физических троичных системах 3B BCT («трёхпроводной») и 2B BCT («двухпроводной») — треугольник с двухсторонними переходами от любой вершины к любой другой вершине.

Граф же троичных триггеров в физической троичной системе 3L LCT («однопроводной») не имеет прямых переходов из -1 в +1 и из +1 в -1, а эти переходы совершаются через прохождение через «0» на 1/3 длительности фронта переключения, что приводит к ложным срабатываниям в последующих логических элементах в более, чем однокаскадных, схемах. В однокаскадных схемах с индикаторами, из-за инерционности зрения, мельтешения из-за этих переходов не видно.

Реверсивный счётчик на 3 и реверсивный регистр сдвига на 3 также являются троичными триггерами.

Троичные триггеры могут быть построены[1]:

1. на двухуровневых логических элементах в двухуровневой трёхбитной системе троичных логических элементов (3Bit BinaryCodedTernary, 3B BCT, «трёхпроводной»),

2. на двухуровневых логических элементах в двухуровневой двухбитной системе троичных логических элементов (2Bit BinaryCodedTernary, 2B BCT, «двухпроводной») и

3. не очень хорошего качества на трёхуровневых логических элементах в трёхуровневой системе троичных логических элементов (3-Level LevelCodedTernary, 3L LCT, «однопроводной»).

В 1956—1958 годах Николай Петрович Брусенцов с группой единомышленников (Механико-математический факультет МГУ) построил первую серийную электронную троичную ЭВМ с позиционной симметричной троичной системой счисления Сетунь.

В 1970 г. Брусенцов из МГУ построил электронную троичную ЭВМ Сетунь-70.

Известный советский компьютерный специалист профессор Д. А. Поспелов писал: «Барьеры, стоящие на пути приложения троичной симметричной системы счисления в компьютерах, являются препятствиями технического порядка. До сих пор не разработаны экономичные и эффективные элементы с тремя устойчивыми состояниями. Как только такие элементы будут разработаны, бо́льшая часть компьютеров универсального типа и многие специальные компьютеры по всей вероятности будут разработаны таким образом, чтобы они функционировали в троичной симметрической системе счисления».

Известный американский учёный Дональд Кнут выражал мнение, что «замена двоичного триггера („flip-flop“) на троичный триггер („flip-flap-flop“) в один прекрасный день обязательно произойдёт».[2](«Flip-flop» означает двухступенчатость, «flip-flap-flop» — трёхступенчатость, Кнут же думал, что «flip-flop» означает двоичность (двухзначность), а «flip-flap-flop» — троичность (трёхзначность)).

Механический троичный счетный триггер применяется в однокнопочных секундомерах.

Элементы и узлы троичных ЭВМ[править | править код]

Подключение относительно простой логики на входе трёхбитного троичного триггера позволяет создать трёхбитный троичный D-триггер с тремя D-входами (троичный D-триггер)[3].

Также возможны трёхбитные троичные аналоги двоичных T-триггеров, троичные регистры данных, троичные полусумматоры, троичные полные сумматоры, троичные арифметико логические устройства (АЛУ), троичные процессоры, троичная статическая оперативная память (SRAM), троичные микроконтроллеры, троичные компьютеры, троичные микроЭВМ.

Быстродействие[править | править код]

За один такт один разряд в троичных системах передаёт один троичный разряд (трит), имеющий три состояния, один разряд в двоичных системах передаёт один бит, имеющий два состояния, то есть один троичный разряд передаёт в 3/2=1,5 (полтора) раза больше чисел (кодов), чем один двоичный разряд.

При использовании трёхбитных и двухбитных триггеров число переключений триггеров, в среднем, такое же, как и в трёхуровневых триггерах, но на выходе трёхбитных и двухбитных триггеров частота переключений в отдельных линиях B2, B1 и B0 на 1/3 меньше, чем в трёхуровневом триггере.

При использовании в трёхбитной и в двухбитной системах обычных двоичных триггеров частота переключения в линиях B2, B1 и B0 на 1/3 меньше, чем в трёхуровневом триггере, то есть применение в троичных трёхбитной и двухбитной системах обычных двоичных триггеров и троичных триггеров на обычных двоичных триггерах позволяет применять логические элементы на 1/3 менее высокочастотные, чем в трёхуровневой однопроводной троичной системе.

Аппаратные затраты[править | править код]

В большинстве случаев при построении логических схем на троичных триггерах аппаратные затраты увеличиваются приблизительно в 2 раза по сравнению с обычными двоичными триггерами и только в очень редких случаях, при решении задач имеющих троичность (Задача «Светофор»[4]), удаётся немного уменьшить аппаратные затраты.

Надёжность[править | править код]

Так как двухуровневые трёхбитные троичные триггеры могут работать и в трёхбитном и в двухбитном режимах, то, в случае обрыва одной из трёх выходных линий (проводников), можно перейти на двухбитный режим, что повышает надёжность устройств на этих триггерах.

В трёхбитном режиме, при обрыве одного из трёх выходных проводников, по уровням на оставшихся двух проводниках возможно полное аппаратное или программное восстановление трёхбитного кода.

Система обратных связей у всех триггеров одинаковая. Выход каждого из трёх элементов соединяется со входами двух других элементов. В триггерах на трёх элементах 3ИЛИ-НЕ и на трёх элементах 3И-НЕ три входных сигнала подаются на три входа трёх элементов и «землю». Триггеры на трёх элементах 3ИЛИ-НЕ и на трёх элементах 3И-НЕ переключаются подачей сигнала переключения на два из трёх входов. В триггерах на элементах 4И-НЕ (SN7420, К155ЛА1[5], 164ЛА8, К176ЛА8, CD4012, 564ЛА8, К561ЛА8, CD4012A, К555ЛА1) и 4ИЛИ-НЕ (164ЛЕ6, К176ЛЕ6, CD4002, 564ЛЕ6, К561ЛЕ6, CD4002A, КР1561ЛЕ6, CD4002B[6]) оставшиеся 6 входов объединяются в три пары, каждая из трёх пар подключена к двум элементам. Три входных сигнала подаются на три объединённые пары и «землю». Триггеры на трёх элементах 4И-НЕ и на трёх элементах 4ИЛИ-НЕ переключаются подачей сигнала переключения на одну из трёх пар. На выходе триггеров три выходные шины и «земля» (общая), подобно трёхфазной электрической сети.

Трёхразрядный одноединичный троичный триггеры на трёх элементах 2ИЛИ-НЕ и трёхразрядный однонулевой троичный триггер на трёх элементах 2И-НЕ целесообразно использовать в ячейках троичной статической сверхоперативной памяти (троичной SRAM).

Так как при «закреплении» уровня хранения на третьем входе монтажной «1» или монтажным «0» эти триггеры работают как обычный двоичный асинхронный RS-триггер, то эти триггеры в троичной цифровой электронике являются троичными аналогами двоичного асинхронного RS-триггера.

- Входы и выходы

В троичном аналоге RS-триггера три входа: S0 (Set0) — установка в 0 (аналог R-входа), S1 (Set1) — установка в 1 (аналог S-входа), S2 (Set2) — установка в 2 (без аналога) и «земля», и три выхода: Q0 — выход инвертора 0 (аналог Q), Q1 выход инвертора 1 (аналог инверсного Q) и Q2 выход инвертора 2 (без аналога) и «земля».

Двухуровневые троичные триггеры[править | править код]

Двухуровневые троичные триггеры строятся на двухуровневых элементах, а троичность работы достигается с помощью системы обратных связей. Двухуровневые троичные триггеры могут быть двухбитными (двухпроводная двухуровневая троичная система) и трёхбитными (трёхпроводная двухуровневая троичная система).

Двухуровневые двухпроводная и трёхпроводная троичные системы более помехоустойчивы, чем трёхуровневая однопроводная троичная система, так как трёхуровневая однопроводная система работает до относительной ЭДС сигнала помехи до Uп/4=0,25 (до 25 % от Uп), а двухуровневые двухпроводная и трёхпроводная троичные системы работают до относительной ЭДС сигнала помехи до Uп/2=0,5*Uп (до 50 % от Uп).

Двухуровневые 2-разрядные[править | править код]

Одну из множества возможных троичных двухбитных двухпроводных систем кодирования («-»={00}, «0»={01}or{10}, «+»={11}) предложил Carl W. Nelson, Jr. в 1969 г.[7]. Двухбитные двухуровневые троичные триггеры работают в троичной двухбитной двухпроводной системе кодирования {00}, {01}, {10} и имеют трёхбитный или двухбитный вход и двухбитный выход.

В качестве двухбитного троичного триггера можно использовать двухуровневые трёхбитные троичные триггеры в двухбитном режиме (с отключенным выходом TQB2).

Двухуровневые трёхбитные[править | править код]

Трёхбитные двухуровневые (трёхфазные[8]) троичные триггеры имеют однозначный трёхбитный вход и однозначный трёхбитный выход. Двухуровневость позволяет строить однозначные трёхбитные троичные триггеры на обычных элементах двухуровневых логик (РТЛ, ДТЛ, ТТЛ, ЭСЛ, МОП, КМОП и др.).

Известны нижеследующие однозначные трёхбитные троичные триггеры:

- Однонулевой трёхбитный троичный триггер на трёх логических элементах 2И-НЕ (функция f2,1,0710).

- Одноединичный трёхбитный троичный триггер на трёх логических элементах 3ИЛИ-НЕ (функция f3,1,110) (триггер с сайта А. П. Стахова)[10](К155ЛЕ4, SN7427).

- Однонулевой трёхбитный троичный триггер на трёх логических элементах 3И-НЕ (функция f3,1,12710) (К155ЛА4, SN7410).

- Троичный трёхбитный одноединичный триггер на трёх логических элементах 4ИЛИ-НЕ А.Турецки[11], который в патенте Larry K. Baxter, Lexington, Mass. Assignee: Shintron Company, Inc., Cambridge, Mass. US Patent 3,764,919 Oct. 9, 1973 Filed: Dec. 22, 1972 Fig.2 уже упоминается как широко известный.

- Однонулевой трёхбитный троичный триггер на трёх логических элементах 4И-НЕ (применён в тристабильной ячейке памяти Takashi Nanya, Tokyo, Japan Assignee: Nippon Electric Company, Limited, Tokyo, Japan US Patent 3,893,086 July 1, 1975 Filed: Dec. 11, 1973 Fig.2. Блок 1) (К155ЛА1, SN7420), подобный триггер с немного усложнённой схемой управления применён в регистре сдвига описанном в патенте ««SU374663 Asynchronous shift register», В. П. Морин и Е. Е. Попов .

- Трёхбитный троичный триггер на трёх логических элементах 2И-2И-2ИЛИ-НЕ (патент SU661606 Memory cell for buffer register. А. И. Бахштаб, В. И. Варшавский, В. Б. Мараховский, В. А. Песчанский, Л. Я. Розенблюм, Н. А. Стародубцев и Б. С. Цирлин).

- Трёхбитный троичный триггер на трёх логических элементах 2И-4ИЛИ-НЕ (АС СССР 599332 25.12.76 Троичный триггер. Н. Г. Коробков, И. Н. Корнет, П. Н. Дмитриев, Л. В. Коробкова, В. И. Гордиенко и В. Д. Близнюк. Харьковский авиационный институт)[12]

Трёхуровневые троичные триггеры[править | править код]

Троичные триггеры на трёхуровневых элементах.

В трёхуровневых элементах трём состояниям соответствуют три уровня напряжения — отрицательное, ноль, положительное, (низкое, среднее, высокое).

В работе[13] на рис.9 приведена схема «троичного статического триггера» на двух трёхуровневых инверторах. Этот триггер имеет три состояния (-1,+1), (+1,-1) и (0,0), но не имеет вращения, а качается как качели или весы.

Схемы троичных трёхуровневых триггеров приведены также в[14] и[15].

Смешанные троичные триггеры[править | править код]

- С двухуровневым (трёхфазным) входом и с трёхуровневым (однофазным) выходом

- С трёхуровневым (однофазным) входом и с двухуровневым (трёхфазным) выходом

На сайте[16] приводится проект смешанного троичного аналога двоичного тактируемого D-триггера с последовательным тактируемым трёхуровневым D-входом и с параллельным двухуровневым (трёхфазным) выходом, состоящий из 11 блоков, от 3 до 5 транзисторов в каждом блоке, то есть, как минимум 33 транзистора на один троичный трёхуровневый D-триггер.

В «Приёмник троичного кода»[17] приводится схема и описание приёмника последовательных трёхуровневых троичных разрядов в «троичном полярном коде» и преобразования их в параллельные двоичные двухразрядные троичные разряды, который является троичным триггером с однолинейным трёхуровневым входом и с двухлинейным двухразрядным выходом с демультиплексором.

Троичные триггеры данных (D-триггеры)[править | править код]

- Триггер Robert C. Braddock USPat.3,662,193 May 9, 1972, Filed May 24, 1971[18] ссылка на прототип из журнала «Electronic Design»,May 10, 1966, раздел «Ideas for Design»

- Троичные триггеры данных (D-триггеры) приведены на странице Троичные триггеры.

Троичные счётные триггеры (Т-триггеры)[править | править код]

- Троичный счётный триггер. АС СССР 764138 27.11.78 Н. Г. Коробков, В. И. Гордиенко, Л. В. Коробкова, Н. Т. Березюк и К. К. Фурманов. Харьковский авиационный институт.[19]

- Троичный счётный триггер. АС СССР 780207 26.12.78 Н. Г. Коробков, Л. В. Коробкова, А. Е. Лебеденко, и К. К. Фурманов. Харьковский авиационный институт им. Н. Е. Жуковского.[20]

- Троичный счётный триггер. SU 1078632 24.12.82 Н. Г. Коробков, Л. В. Коробкова, А. Е. Лебеденко и К. К. Фурманов. Харьковский авиационный институт им. Н. Е. Жуковского.[21]

- Троичный счётный триггер. SU 1188887 28.02.84 Б. С. Цирлин. Институт социально-экономических проблем АН СССР.[22]

- Троичный счётный триггер. SU 1422405 21.01.87 А. С. Галкин, В. П. Грибок, Л. Б. Лимановская и В. О. Твердохлебова[23]. При проверке модели троичного счётного триггера на элементах ИЛИ-НЕ в логическом симуляторе реального времени Atanua триггер оказался работоспособным.

- Троичные счётные триггеры приведены на странице Троичные триггеры и на странице Троичные трёхбитные счётные триггеры (T-триггеры).

- Экономичный трёхбитный (3B BCT UU) троичный счётный триггер (Т-триггер)[24]

- Гурвич И. С. Многоустойчивые потенциальные схемы,-«Приборы и системы управления», 1968, № 10. АС СССР 599332

- Бухреев И. Н. и др. «Микроэлектронные схемы цифровых устройств». М., «Сов. радио», 1975, с.215, рис.5.51. АС СССР 599332

- Патент США № 3508033 1970

- АС СССР № 319078 1971

- АС СССР № 851785 1979

- Куликов А. С. Троичные триггеры

- Александр Кушнеров. Троичная цифровая техника. Ретроспектива и современность. // Университет им. Бен-Гуриона, Беэр-Шева, Израиль. 28.10.05

- Микросхема нового усилителя тока работающая в троичной системе.

- Prosser, F. Wu, X. Chen, X. Computers and Digital Techniques, IEE Proceedings E. Sep 1988. Volume: 135, Issue: 5, On page(s): 266—272. «CMOS ternary flip-flops and their applications» Dept. of Comput. Sci., Indiana Univ., Bloomington, IN, USA

- Zhuang, N. Wu, H. Electronics Letters. 19 July 1990 Volume: 26, Issue: 15. On page(s): 1145—1146. «Novel ternary JKL flip-flop» Dept. of Electr. Eng., Hangzhou Univ., Zhejiang, China.

- Стив Грабб. Стив Грабб. Проект элементов и узлов троичного компьютера (англ.)

- ↑ Троичные триггеры

- ↑ «Троичный принцип» Николая Брусенцова. (неопр.) (недоступная ссылка). Дата обращения 5 июня 2008. Архивировано 11 июня 2008 года.

- ↑ Троичные триггеры

- ↑ Экономичность троичной трёхбитной системы троичных логических элементов (3B BCT) на примере задачи «Светофор»

- ↑ Транзисторно-транзисторная логика

- ↑ Справочник по низкочастотным КМОП микросхемам

- ↑ US Patent 3,641,327 Feb. 8, 1972 Filed: Aug. 13, 1969

- ↑ Д. А. Поспелов. Логические методы анализа и синтеза схем. Издание третье, переработанное и дополненное. «Энергия» Москва 1974. Стр.352. Определение 9-1.

- ↑ Using CMOS gates/US5815436 Multi-level nonvolatile semiconductor memory Такая же схема, не являющаяся предметом патентования, приведена в патенте US5815436 Sep. 29, 1998 Multi-level nonvolatile semiconductor memory device having improved programming level and read/write multi-level data circuits. Tomoharu Tanaka, Hiroaki Hazama, Yokohama, Japan

- ↑ Троичный триггер («flip-flap-flop») (неопр.) (недоступная ссылка). Дата обращения 7 марта 2008. Архивировано 3 марта 2008 года.

- ↑ A.Turecki US Pat. 3,508,033 April 21, 1970. Filed Jan. 17, 1967 Fig.2.

- ↑ http://www.ee.bgu.ac.il/~kushnero/ternary/Binary%20coded%20ternary/SU599332%20Fast%20ternary%20trigger.pdf Троичный триггер. АС СССР 599332 Заявлено 25.12.76

- ↑ Троичная цифровая техника. Перспектива и современность. 28.10.05 Александр Кушнеров, Университет им. Бен-Гуриона, Беэр-Шева, Израиль.

- ↑ Figure Архивная копия от 12 мая 2010 на Wayback Machine D.45. PZN tri-flop, from Mouftah’s Image:Mouftah-8a-PZN Tri-flop.png from Mouftah’s patent[15]

- ↑ http://jeff.tk:81/wiki/Trinary/Circuits#D.5.2._PZN_Tri-Flop Архивная копия от 12 мая 2010 на Wayback Machine Figure D.48. Mouftah’s clocked PZN tri-flop, from Image:Mouftah-9-Clocked PZN Tri-flop.png

- ↑ trinary.cc

- ↑ «Приёмник троичного кода» М. А. Буркова, К. А. Гусакова, Озёрский технологический институт (филиал) МИФИ, Научная сессия МИФИ-2007. Том 1.

- ↑ TRI-STABLE CIRCUIT (недоступная ссылка)

- ↑ Троичный счётный триггер АС СССР 764138 Заявлено 27.11.78

- ↑ Троичный счётный триггер АС СССР 780207 Заявлено 26.12.78

- ↑ Троичный счётный триггер АС СССР 1078632 Заявлено 24.12.84

- ↑ Троичный счётный триггер (его варианты) АС СССР 1188887 Заявлено 28.02.84

- ↑ Троичный счётный триггер АС СССР 1422405 Заявлено 21.01.87

- ↑ Экономичный трёхбитный (3B BCT UU) троичный счётный триггер (Т-триггер)

RS — состоящими из двух входов;

RS — состоящими из двух входов;