6.6. Двухступенчатые триггеры

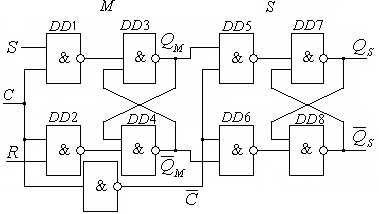

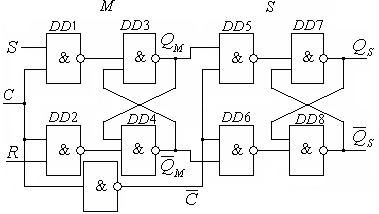

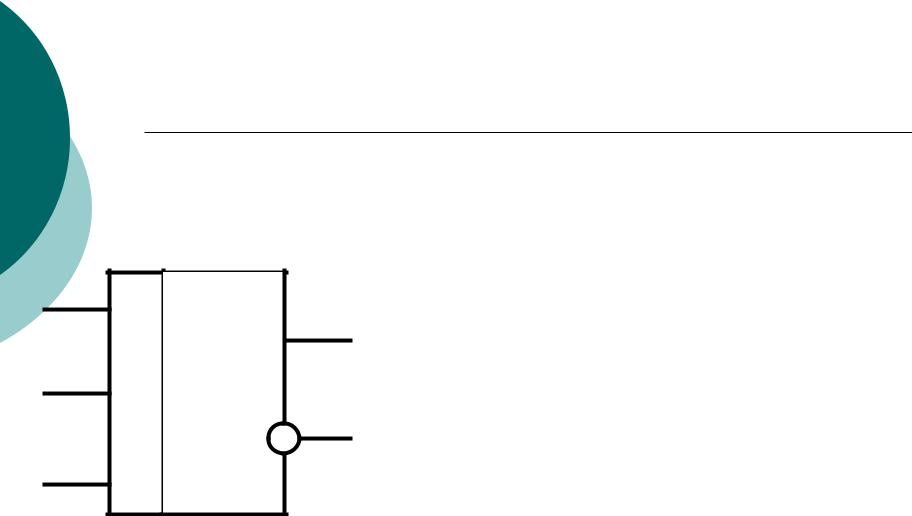

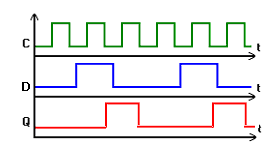

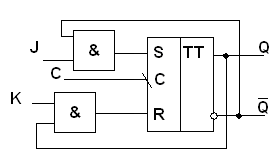

На рис. 6.12 показана схема, состоящая из двух последовательно включенных синхронных RS-триггеров, первый из которых называется ведущим или М-триггером (от master – хозяин), а второй – ведомым или S-триггером (от slave – подчиненный). Благодаря общему синхросигналу С вся схема функционирует как единое целое и называется двухступенчатым или MS-триггером (master-slave flip-flop).

Рис. 6.12. Схема MS-триггера

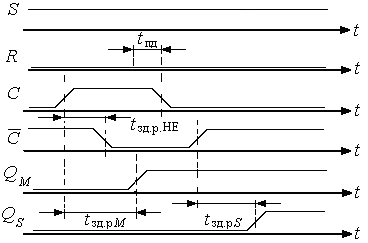

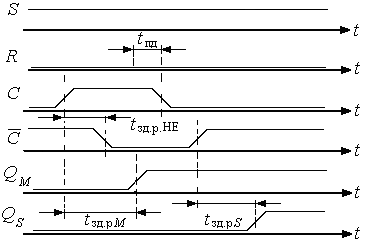

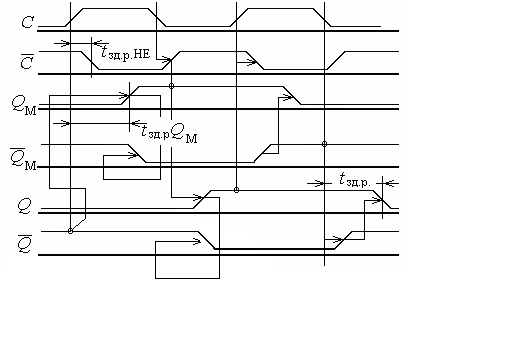

Из временной диаграммы (рис. 6.13) видно, что информация, задаваемая уровнями на входах S и R, по фронту С-сигнала принимается в М-триггер, но в течение всего времени, пока

.

Они откроются лишь при

.

Они откроются лишь при ,

т.е. на срезеС-сигнала,

и только тогда S-триггер

примет состояние М-триггера.

,

т.е. на срезеС-сигнала,

и только тогда S-триггер

примет состояние М-триггера.Отсюда важное отличие MS-триггера от триггера-защелки: MS-триггер непрозрачен по управляющим R— и S-входам ни при С = 0, ни при С = 1. Каждая ступень его сама по себе прозрачна, но включены ступени последовательно, и какая-нибудь из них всегда остается запертой – или синхросигналом, или его отсутствием. Таким образом, в

Рис. 6.13. Временная диаграмма работы

Следует отметить также, что появлению среза сигнала С должен предшествовать интервал времени подготовки tпд, в течение которого сигналы на S— и R— входах не должны изменяться. Если такого интервала не было, т.е. перед появлением среза С было изменение S- или R-сигнала и переключение М-триггера, эти процессы могут наложиться и работа MS-триггера будет неустойчивой.

6.7. JK-триггеры

Этот тип триггеров не имеет неопределенных состояний. Функциональная особенность

JK-триггеры относятся к универсальным устройствам. Они с равным успехом могут использоваться в регистрах, счетчиках, делителях частоты и других узлах. Путем определенного соединения выходов

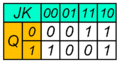

Состояния JK-триггера при различных комбинациях входных сигналов представлены в табл. 6.8.

Таблица 6.8

Такт n | Такт n+1 | |

Jn | K | Qn+1 |

0 | 0 | Qn |

0 | 1 | 0 |

1 | 0 | 1 |

1 | 1 |

|

По способу управления JK-триггеры, также как и RS-триггеры, могут быть синхронными и асинхронными. Применяют, однако, только синхронные, так как асинхронные предъявляют жесткие требования к длительности входных импульсов.

В

схемном отношении JK-триггеры

отличаются от RS-триггеров

наличием обратной связи с выходов на

входы. Схема простейшего JK-триггера

представлена на рис. 6.14. Из схемы следует,

что состояние JK-триггера

зависит не только от J и K,

но и от Q и  .

Элементы временной задержки 3 и 4 в

данной схеме играют роль стабилизаторов

состояний триггера и непосредственно

на его функциональные свойства не

влияют.

.

Элементы временной задержки 3 и 4 в

данной схеме играют роль стабилизаторов

состояний триггера и непосредственно

на его функциональные свойства не

влияют.

Рис. 6.14. Структура JK-триггера с элементами временной задержки

При Jn= Kn=

0 на выходах элементов DD1

и DD2

будет q1 = q2=

1 (независимо от значений Q и  ),

что представляет нейтральную комбинацию

для собственно триггера (элементов

),

что представляет нейтральную комбинацию

для собственно триггера (элементов

Когда Jn ¹ Kn, выходное состояние триггера будет определяться элементом DD 1 или DD 2, на входах которого действует логическая 1.

Входная комбинация Jn = Kn = 1 при любом состоянии триггера вызывает его переброс. Действительно, если Qn = 1 и Qинвn = 0, то q1 = 1, а

n =

1.

n =

1. Назначение

цепей временной задержки 3 и 4 – создание

временного сдвига между моментом ввода

входной информации и началом формирования

выходной (Qn и

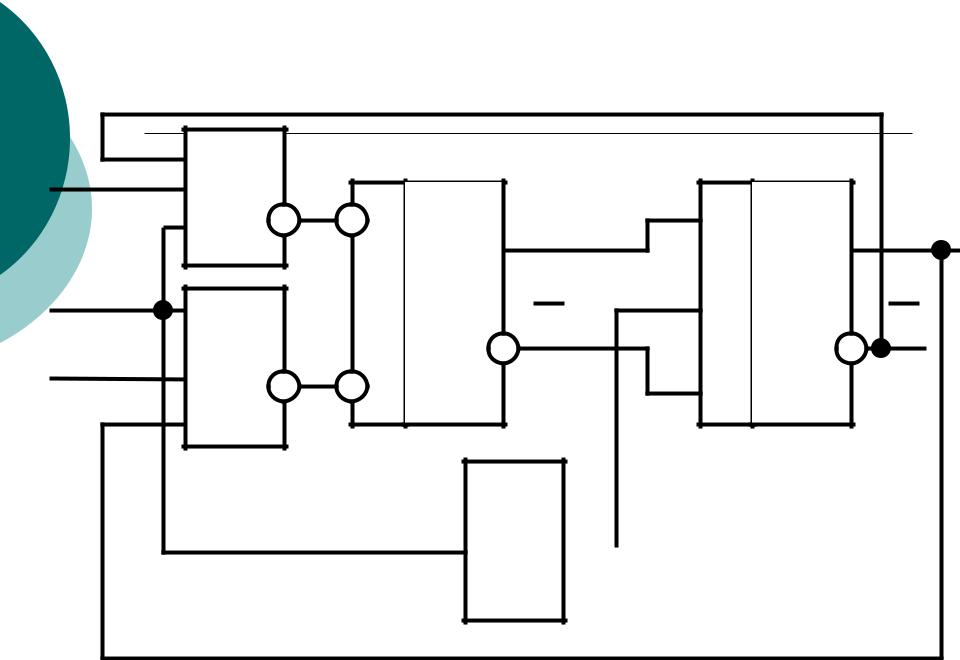

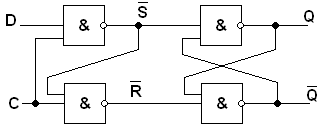

Предупреждение генерации просто и эффективно обеспечивается в триггерах с двухступенчатым управлением. Схема двухступенчатого JK-триггера с инвертором в цепи синхронизации представлена на рис. 6.15.

Двухступенчатый JK-триггер – непрозрачный триггер, выходы его петлями инвертирующих обратных связей (накрест) заведены на входные конъюнкторы

При J =

1, K =

0 синхросигналом может быть открыт лишь

элемент DD 1 и только при условии, что перед

поступлением С-сигнала

на выходе триггера был 0: Q =

0,  =

1. Тогда по срезу синхросигнала триггер

переключится в 1.

=

1. Тогда по срезу синхросигнала триггер

переключится в 1.

Рис. 6.15. Двухступенчатый JK-триггер с инвертором в цепи синхронизации

Если же триггер до синхросигнала был в 1, то он так и останется в 1. Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что К-вход выполняет функции синхронизированного R-входа, переводя триггер в 0. Поэтому при разноименных уровнях на J— и К-входах JK-триггер ведет себя как синхронный непрозрачный RS-триггер.

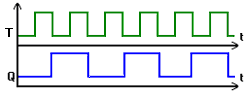

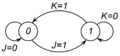

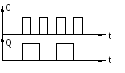

Существенно отлично от RS-триггера поведение JK-триггера при J = K = 1. Для RS-триггера такое состояние запрещено. Диаграмма работы JK-триггера в этом режиме приведена на рис. 6.16. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот конъюнктор, пройдя через который С-сигнал переведет триггер в противоположное состояние.

Таким образом, при J = K = 1 по срезу каждого С-сигнала JK-триггер меняет свое состояние на противоположное. Это уже известный четный режим. Режимы работы JK-триггера представлены в табл. 6.9.

Рис. 6.16. Временная диаграмма работы JK-триггера в счетном режиме

Таблица 6.9

Режим | Входы | Выходы | |||

С | J | K | Q |

| |

Хранения | | 0 | 0 | Q |

|

Сброс | ` ë | 0 | 1 | 0 | 1 |

Установка | ` ë | 1 | 0 | 1 | 0 |

Счетный | ` ë | 1 | 1 |

| Q |

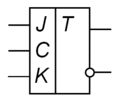

Следует отметить, что серийно выпускаемые JK-триггеры имеют по нескольку конъюнктивно связанных J- и К-входов. Примером тому является микросхема К155ТВ1. Это JK-триггер, имеющий тройные конъюнктивные входы J и К, а также асинхронные входы Rа и Sа для установки триггера в состояние 0 ипи 1 независимо от сигналов на информационных и тактирующем входе. Условное обозначение этого триггера приведено на рис.6.18.

Рис. 6.17 Условное обозначение JK-триггера K155TB1

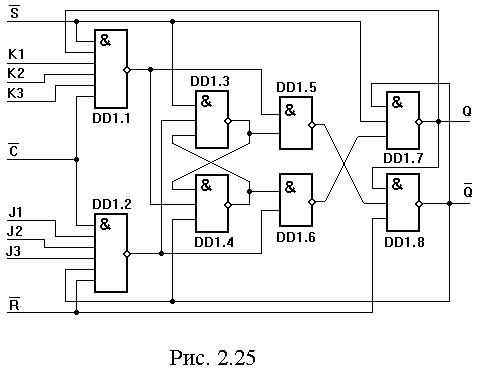

Внутренняя структура этого триггера близка к структуре JK-триггера, рассмотренной ранее (рис. 6.16), и приведена на рис 6.18.

Известны и другие разновидности JK триггеров: JK-триггер с запоминающими связями, JK-триггер, переключаемый фронтом, шестиэлементный триггер, JK-триггер, использующий задержку. Более подробные сведения о JK-триггере можно получить в справочной литературе, например [9].

Рис. 6.18 Внутренняя структура JK-триггера K155TB1

_18Л_ДвухступенчатыеТриггеры

Тактируемые триггеры

Тактируемые логические схемы кроме информационных входов имеют один или несколько входов синхронизации. Тактовые синхроимпульсы позволяют разнести во времени переходные процессы в различных каскадах логических устройств, чтобы избежать ложных срабатываний в моменты переключения. Простейшими примерами могут служить синхронный RS- и D-триггеры. Достаточно часто используют две тактовые последовательности синхроимпульсов с одинаковой частотой, но смещенных на половину периода. В сложных системах может использоваться большее число тактовых последовательностей. Тактированные логические устройства работают медленнее асинхронных, сложнее и потребляют больше энергии питания, но функционируют более устойчиво.

Двухступенчатые триггеры

Триггеры с двухступенчатым запоминанием информации состоят из двух триггеров. Первый называется ведущим, второй — ведомым т (рис. 1).

Рис.1

Оба триггера — синхронные RS-триггеры, но имеют противоположные синхровходы. Ведущий триггер срабатывает при С = 1, имеет прямой синхронизирующий вход, а ведомый при С = 0. Для этого синхроимпульс подвергается инверсии.

На первом этапе, когда происходит запись информации в ведущий триггер, ведомый отключен и продолжает сохранять предыдущее состояние. Когда синхроимпульс заканчивается, ведущий триггер переходит в режим хранения и происходит перезапись его состояния в ведомый триггер. Таким образом, происходит поэтапная запись информации.

В двухступенчатом триггере устраняется противоречие между процессами хранения старой и приема новой информации. Это дает возможность построения синхронных автоматов без опасных временных состояний, исключить предпосылки к режиму генераций. Позволяет обеспечить высокую надежность функционирования триггеров с внутренними цепями обратной связи. В то же время схемы этих триггеров более сложные, чем схемы триггеров с динамическим входом, а быстродействие ниже.

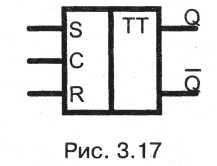

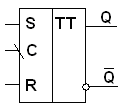

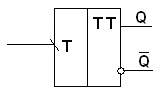

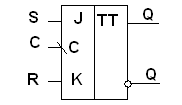

Часто двухступенчатый триггер называют MS-триггером от английских слов «master» и «slave» — хозяин и раб. На принципиальных схемах двухступенчатые триггеры обозначаются сдвоенной буквой (ТТ) рис. 2.

Рис.2

По структуре двухступенчатого триггера могут быть построены любые типы триггеров.

JK-триггер

JK-триггеры — это двухступенчатые универсальные синхронные триггеры. Универсальность заключается в том, что на их основе можно сделать любой другой тип логических триггеров RS, D, Т.

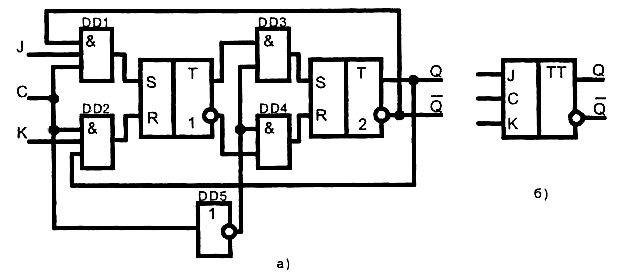

JK триггер является двухступенчатым триггером с дополнительными обратными связями, исключающими появление запрещенных комбинаций. Для этого его управление входами первого триггера построено на элементах 3И (DD1—DD2) и имеет два дополнительных входа, на которые и подаются обратные связи. На рис. 3 приведена подробная схема и условное изображение JK—триггера.

Рис.3

При уровне логического 0 на входе С первый RS-триггер не реагирует на сигналы входов J и К. При подаче на вход С = 1 первый RS—триггер устанавливается в состояние, определяемое сигналами на J и K входах. При этом связь между RS—триггерами обрывается, т. к. элементы И DD3-DD4 устанавливаются в нулевое состояние. Подача вновь сигнала С = 0 на синхровход JK-триггера приводит к отключению первого RS-триггера от входных сигналов из-за элементов DD1, DD2. Однако, при С = 0 через инвертор DD5 на входы элементов DD3, DD4 поступает логическая единица и состояние первого RS-триггера перезаписывается во второй.

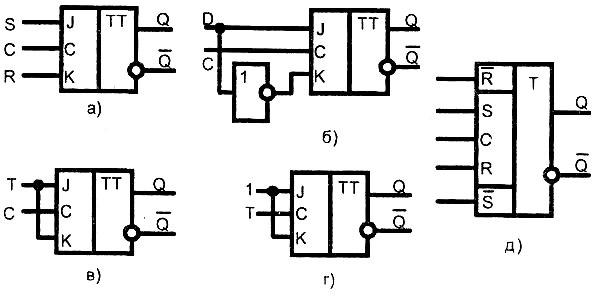

На основе JK-триггера может быть построен любой другой триггер (рис.4). На рис.4, а — синхронный RS-триггер, на рис.4, б — D-триггер, на рис.4, в — синхронный Т-триггер, на рис.4, г — асинхронный T-триггер.

Рис.4

JK-триггер, как и другие типы триггеров, может дополнительно иметь входы начальной установки (рис.4, д), которые являются инверсными по отношению ко входам J.K.

JK-триггеры — это более сложные триггеры, содержат большее число элементов, поэтому потребляемая мощность Рпот оказывается большой. Меры, принимаемые к уменьшению потребляемой мощности, нередко приводят к ухудшению частотных свойств. JK-триггер вследствие своей универсальности и отсутствия запрещенных комбинаций находит широкое применение в цифровой технике.

6.6. Двухступенчатые триггеры

На рис. 6.12 показана схема, состоящая из двух последовательно включенных синхронных RS-триггеров, первый из которых называется ведущим или М-триггером (от master – хозяин), а второй – ведомым или S-триггером (от slave – подчиненный). Благодаря общему синхросигналу С вся схема функционирует как единое целое и называется двухступенчатым или MS-триггером (master-slave flip-flop).

Рис. 6.12. Схема MS-триггера

Из

временной диаграммы (рис. 6.13) видно, что

информация, задаваемая уровнями на

входах S и R,

по фронту С-сигнала

принимается в М-триггер,

но в течение всего времени, пока С-сигнал

равен 1, не проходит в S-триггер,

поскольку его входные конъюнкторы DD5

и DD6

в это время перекрыты инверсией С-сигнала

– сигналом  .

Они откроются лишь при

.

Они откроются лишь при ,

т.е. на срезеС-сигнала,

и только тогда S-триггер

примет состояние М-триггера.

,

т.е. на срезеС-сигнала,

и только тогда S-триггер

примет состояние М-триггера.

Отсюда важное отличие MS-триггера от триггера-защелки: MS-триггер непрозрачен по управляющим R— и S-входам ни при С = 0, ни при С = 1. Каждая ступень его сама по себе прозрачна, но включены ступени последовательно, и какая-нибудь из них всегда остается запертой – или синхросигналом, или его отсутствием. Таким образом, в MS-триггере никакое изменение на управляющем входе не может само по себе, без переключения сигнала С проникнуть на выход. Триггер может изменить состояние выхода только по срезу С-сигнала. Между тем, как и для синхронного RS триггера, построенного на элементах И-НЕ(см. таблицу 6.5), комбинация сигналов S=R=1 объявляется запрещенной, поскольку приводит триггер в неопределенное состояние.

Рис. 6.13. Временная диаграмма работы MS-триггера

Следует отметить также, что появлению среза сигнала С должен предшествовать интервал времени подготовки tпд, в течение которого сигналы на S— и R— входах не должны изменяться. Если такого интервала не было, т.е. перед появлением среза С было изменение S- или R-сигнала и переключение М-триггера, эти процессы могут наложиться и работа MS-триггера будет неустойчивой.

6.7. JK-триггеры

Этот тип триггеров не имеет неопределенных состояний. Функциональная особенность JK-триггера состоит в том, что при всех входных комбинациях, кроме одной Jn = Kn = 1, они действуют подобно RS-триггеру, причем вход J играет роль входа S, а К-вход соответствует R-входу, С – тактовый вход. При входной комбинации Jn = Kn = 1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам. Они с равным успехом могут использоваться в регистрах, счетчиках, делителях частоты и других узлах. Путем определенного соединения выходов JK-триггеры легко обращаются в триггеры других типов. Это позволяет промышленности сократить номенклатуру триггеров, не сковывая в то же время разработчиков аппаратуры.

Состояния JK-триггера при различных комбинациях входных сигналов представлены в табл. 6.8.

Таблица 6.8

Такт n | Такт n+1 | |

Jn | Kn | Qn+1 |

0 | 0 | Qn |

0 | 1 | 0 |

1 | 0 | 1 |

1 | 1 |

|

По способу управления JK-триггеры, также как и RS-триггеры, могут быть синхронными и асинхронными. Применяют, однако, только синхронные, так как асинхронные предъявляют жесткие требования к длительности входных импульсов.

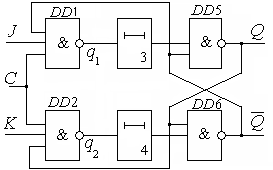

В

схемном отношении JK-триггеры

отличаются от RS-триггеров

наличием обратной связи с выходов на

входы. Схема простейшего JK-триггера

представлена на рис. 6.14. Из схемы следует,

что состояние JK-триггера

зависит не только от J и K,

но и от Q и  .

Элементы временной задержки 3 и 4 в

данной схеме играют роль стабилизаторов

состояний триггера и непосредственно

на его функциональные свойства не

влияют.

.

Элементы временной задержки 3 и 4 в

данной схеме играют роль стабилизаторов

состояний триггера и непосредственно

на его функциональные свойства не

влияют.

Рис. 6.14. Структура JK-триггера с элементами временной задержки

При Jn= Kn=

0 на выходах элементов DD1

и DD2

будет q1 = q2=

1 (независимо от значений Q и  ),

что представляет нейтральную комбинацию

для собственно триггера (элементовDD5

и DD6),

который хранит записанную ранее

информацию (см. табл. 6.3 для RS-триггера

на элементах И-НЕ).

),

что представляет нейтральную комбинацию

для собственно триггера (элементовDD5

и DD6),

который хранит записанную ранее

информацию (см. табл. 6.3 для RS-триггера

на элементах И-НЕ).

Когда Jn ¹ Kn, выходное состояние триггера будет определяться элементом DD 1 или DD 2, на входах которого действует логическая 1.

Входная

комбинация Jn = Kn = 1 при любом состоянии триггера вызывает

его переброс. Действительно, если Qn = 1 и Qинвn = 0, то q1 =

1, а q2 =

0 (т.к. Кn = Qn = 1). Сигнал q2 переключит триггер в состояние Qинвn+1 =

1 и Qn+1 =

0. Переброс будет и при Qn = 0, а  n =

1.

n =

1.

Назначение

цепей временной задержки 3 и 4 – создание

временного сдвига между моментом ввода

входной информации и началом формирования

выходной (Qn и  n+1).

Без этих цепей во время действия входной

комбинации Jn = Kn = 1 началась бы генерация из-за того, что

с каждой сменой выходных сигналов на

входах оказывалась бы комбинация,

вызывающая новое опрокидывание триггера.

Для предотвращения генерации длительность

задержки должна превысить длительность

тактовых импульсов.

n+1).

Без этих цепей во время действия входной

комбинации Jn = Kn = 1 началась бы генерация из-за того, что

с каждой сменой выходных сигналов на

входах оказывалась бы комбинация,

вызывающая новое опрокидывание триггера.

Для предотвращения генерации длительность

задержки должна превысить длительность

тактовых импульсов.

Предупреждение генерации просто и эффективно обеспечивается в триггерах с двухступенчатым управлением. Схема двухступенчатого JK-триггера с инвертором в цепи синхронизации представлена на рис. 6.15.

Двухступенчатый JK-триггер – непрозрачный триггер, выходы его петлями инвертирующих обратных связей (накрест) заведены на входные конъюнкторы DD1 и DD2. При J = K = 0 С-сигнал не может открыть входные элементы DD1 и DD2 и триггер находится в режиме хранения.

При J =

1, K =

0 синхросигналом может быть открыт лишь

элемент DD 1 и только при условии, что перед

поступлением С-сигнала

на выходе триггера был 0: Q =

0,  =

1. Тогда по срезу синхросигнала триггер

переключится в 1.

=

1. Тогда по срезу синхросигнала триггер

переключится в 1.

Рис. 6.15. Двухступенчатый JK-триггер с инвертором в цепи синхронизации

Если же триггер до синхросигнала был в 1, то он так и останется в 1. Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что К-вход выполняет функции синхронизированного R-входа, переводя триггер в 0. Поэтому при разноименных уровнях на J— и К-входах JK-триггер ведет себя как синхронный непрозрачный RS-триггер.

Существенно отлично от RS-триггера поведение JK-триггера при J = K = 1. Для RS-триггера такое состояние запрещено. Диаграмма работы JK-триггера в этом режиме приведена на рис. 6.16. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот конъюнктор, пройдя через который С-сигнал переведет триггер в противоположное состояние.

Таким образом, при J = K = 1 по срезу каждого С-сигнала JK-триггер меняет свое состояние на противоположное. Это уже известный четный режим. Режимы работы JK-триггера представлены в табл. 6.9.

Рис. 6.16. Временная диаграмма работы JK-триггера в счетном режиме

Таблица 6.9

Режим | Входы | Выходы | |||

С | J | K | Q |

| |

Хранения | | 0 | 0 | Q |

|

Сброс | ` ë | 0 | 1 | 0 | 1 |

Установка | ` ë | 1 | 0 | 1 | 0 |

Счетный | ` ë | 1 | 1 |

| Q |

Следует отметить, что серийно выпускаемые JK-триггеры имеют по нескольку конъюнктивно связанных J- и К-входов. Примером тому является микросхема К155ТВ1. Это JK-триггер, имеющий тройные конъюнктивные входы J и К, а также асинхронные входы Rа и Sа для установки триггера в состояние 0 ипи 1 независимо от сигналов на информационных и тактирующем входе. Условное обозначение этого триггера приведено на рис.6.18.

Рис. 6.17 Условное обозначение JK-триггера K155TB1

Внутренняя структура этого триггера близка к структуре JK-триггера, рассмотренной ранее (рис. 6.16), и приведена на рис 6.18.

Известны и другие разновидности JK триггеров: JK-триггер с запоминающими связями, JK-триггер, переключаемый фронтом, шестиэлементный триггер, JK-триггер, использующий задержку. Более подробные сведения о JK-триггере можно получить в справочной литературе, например [9].

Рис. 6.18 Внутренняя структура JK-триггера K155TB1

D-триггер двухступенчатый

В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ. Двухступенчатый D – триггер называют триггером с динамическим управлением. Общая схема двухступенчатого триггера

T-триггеры

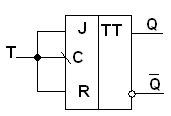

Т-триггер (от англ. Toggle — переключатель) часто называют счётным триггером, так как он является простейшим счётчикомдо 2.

Т-триггер асинхронный

Асинхронный Т-триггер не имеет входа разрешения счёта — Т и переключается по каждому тактовому импульсу на входе С.

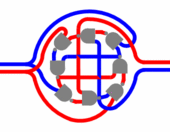

Работа схемы асинхронного двухступенчатого T-триггера с парафазным входом на двух парафазных D-триггерах на восьми логических вентилях2И-НЕ. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1

T-триггер синхронный

T | Q(t) | Q(t+1) |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

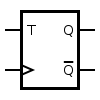

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

Синхронный Т-триггер[17], при единице на входеТ, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входеT. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы JиKлогической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входыJиК.

В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход Сподаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Твход подают единицу, а наС— сигнал с частотой, которая будет поделена на 2.

T-триггер двухступенчатый со сложной логикой tv-триггер двухступенчатый со сложной логикой jk-триггер

JK-триггер с дополнительными асинхронными инверсными входами SиR

J | K | Q(t) | Q(t+1) |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 0 | 1 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 1 |

1 | 1 | 1 | 0 |

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы JиKлогической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входыJиК[20].

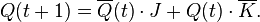

Алгоритм функционирования JK-триггера можно представить формулой

Условное графическое обозначение JK-триггера со статическим входом С

Граф переходов JK-триггера

Карта Карно JK-триггера

5.6. Двухступенчатый синхронный jk-триггер

Отличительной особенностью JK-триггера является то, что он не имеет запрещённых комбинаций входных сигналов на информационных входах. РаботуJK-триггера описывает таблица переходов (таблица 5.5), в которой активным считается сигнал логической 1. Активный сигнал входаJпереключает триггер в состояниеQ=1, а входа К – вQ=0.

Таблица 5.5

Таблица переходов JK-триггера

С | J | K | Qn | Qn+1 |

1 | 0 | | 0 | 0 |

1 | 1 | | 0 | 1 |

1 | | 1 | 1 | 0 |

1 | | 0 | 1 | 1 |

0 | 0 | | 0 | 0 |

0 | 1 | | 0 | 0 |

0 | | 1 | 1 | 1 |

0 | | 0 | 1 | 1 |

Из таблицы переходов следует, что при одновременной подаче на информационные входы JиKактивных сигналов триггер работает как счётный. Такое возможно только в двухступенчатом триггере. Структурная схемаJK-триггера представлена на рис. 5.10.

|

Рис. 5.10. Структурная схема JK-триггера

Как видно из схемы, на входы элементов 3И DD3 илиDD4 поступает с выхода триггераDD2 один сигнал логического 0 и один логической единицы. Поэтому на входахJиKмогут быть любые сигналы, но на входыSиRDD1 одновременно два активных сигнала поступить не могут.

JK-триггер является универсальным. На его основе можно создать любую схему триггера. На рис. 5.11 представлена реализация всех ранее рассмотренных триггеров наJK-триггере.

Рис. 5.11. Реализация триггеров на основе JK-триггера:

а – синхронный RS-триггер; б – D-триггер; в – Т-триггер

В серии ТТЛ JK-триггер выполнен на микросхеме К155ТВ1, в серии КМОП – К561ТВ1 и К176ТВ1, то есть всего по одной микросхеме в серии. Это объясняется малой востребованностью триггеров со статическим управлением для применения в схемах автоматики и телемеханики.

5.7. Триггер с динамическим управлением

Все рассмотренные выше триггеры являются триггерами со статическим управлением. Это накладывает определённые требования на построение схем, так как во время активного состояния сигнала синхронизации сигналы на информационных входах не должны изменяться, что бывает трудно обеспечить, особенно при большой частоте работы схемы. От такого недостатка свободны триггеры с динамическим управлением. Суть динамического управления заключается в том, что в качестве активного сигнала синхронизации выступает не уровень, а его изменение. Переключение триггера происходит в момент смены уровней на входе синхронизации.

Если триггер переключается по фронту импульса синхронизации (переключение от логического 0 к логической 1), то это прямой динамический вход, а если по срезу импульса синхронизации (переключение от логической 1 к логическому 0) –инверсный динамический вход. На рис. 5.12 показаны условные графические обозначения триггеров с прямым и инверсным динамическим входом.

а | б |

Рис. 5.12. Условные графические обозначения триггеров:

а — с прямым; б — с инверсным динамическим входом

Различие типа динамического входа иллюстрируют временные диаграммы работы триггеров, представленные на рис 5.13.

а | б |

Рис. 5.13. Временные диаграммы работы триггеров:

а — с прямым; б — с инверсным динамическим входом

Временные диаграммы аналогичны временным диаграммам Т-триггера, но следует ещё раз отметить, что триггер с динамическим управлением переключается только при изменении сигнала на входе С и не чувствителен к изменению сигналов на информационных входах во время действия сигнала синхронизации С = 0 и С = 1.

Все D-триггеры на микросхемах серий ТТЛ и КМОП имеют вход С с динамическим управлением. На рис. 5.14. представлены условные графические обозначенияD-триггеров.

К

155ТМ2

155ТМ2К

561ТМ2

561ТМ2

Рис. 5.14. Условные графические обозначения D-триггеров

Кроме динамического входа С триггеры имеют статические входы данных Dи асинхронные входы установкиSиR. У микросхемы ТТЛ К155ТМ2 асинхронные входы установки инверсные, а у микросхемы КМОП К561ТМ2 – прямые. Как уже было отмечено в п. 5.3,D-триггеры широко представлены во всех сериях микросхем ТТЛ и КМОП. На основеD-триггеров строятся схемы счётчиков и регистров.

Контрольные вопросы

1. Дайте определение триггера.

2. Перечислите наименование входов триггера.

3. Какие входы имеет асинхронный триггер?

4. Какие входы имеет синхронный триггер?

5. Нарисуйте схему асинхронного RS-триггера на элементах 2И-НЕ и 2ИЛИ-НЕ. Какая из этих схем имеет прямые, а какая инверсные входы?

6. Для какой цели применяется асинхронный RS-триггер? Приведите схему и её временную диаграмму.

7. Нарисуйте схему синхронного RS-триггера на элементах 2И-НЕ и приведите временную диаграмму работы.

8. Нарисуйте схему D-триггера на элементах 2И-НЕ и приведите временную диаграмму работы. Для какой цели применяетсяD-триггер?

9. Как превратить D-триггер в счётный Т-триггер? Приведите схему и её временную диаграмму. Какой недостаток имеет данная схема?

10. Для чего применяется схема двухступенчатого Т-триггера? Приведите схему и её временную диаграмму. Почему в схеме исключён режим генерации импульсов?

11. Для какой цели применяется JK-триггер? Почему в схемеJK-триггера исключён режим генерации импульсов?

12. Приведите примеры реализации синхронного RS-триггера, асинхронногоRS-триггера иD-триггера наJK-триггере.

13. В чём суть динамического управления триггера по входу С?

14. Приведите условные графические обозначения и временные диаграммы работы триггеров с прямым и инверсным динамическим входом.

15. Почему асинхронные входы SиRD-триггеров с динамическим входом имеют приоритет над входами С иD?

Двухступенчатый JK-триггер

|

| J | K | Qt | Qt+1 | Режим |

Q | 0 | 0 | 0 | 0 | Хранение | |

0 | 0 | 1 | 1 |

| ||

|

|

| ||||

|

| 0 | 1 | 0 | 0 | Запись |

Q |

| 0 | 1 | 1 | 0 | «0» |

|

| 1 | 0 | 0 | 1 | Запись |

|

| 1 | 0 | 1 | 1 | «1» |

|

| 1 | 1 | 0 | 1 | Переклю- |

|

| 1 | 1 | 1 | 0 | чение |

Двухступенчатый JK-триггер

J | & |

|

|

| S | Q1 | |

|

| ||

С |

|

| T |

|

| Q1 | |

K | & |

| |

R |

| ||

|

| ||

|

|

|

1

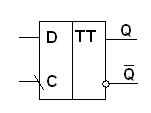

Построение D-триггера

на основе JK-триггера

D | J | Q | |

| |||

С | С | TT | |

Q | |||

| |||

|

| ||

1 | K |

|

Построение T-триггера

на основе JK-триггера

+5В | J | Q | |

| |||

T | С | TT | |

Q | |||

| |||

|

| ||

| K |

|

Двухступенчатый синхронный rs-триггер

Такой триггер состоит из двух синхронных RS-триггеров и инвертора:

При синхросигнале С=1 происходит запись информации с информационных входов в первый триггер(ведущий), при этом входы второго триггера(ведомого) закрыты, т. к. на его синхровход подается О. И только при изменении синхросигнала с 1 в 0 происходит перепись информации из ведущего триггера в ведомый. При этом закрыты информационные входы ведущего триггера, т. к. С=0. Таким образом ,двухступенчатый RS-триггер имеет динамическую снхронизацию и переключается по заднему фронту синхросигнала (инверсный синхровод), что отмечено соответствующим наклоном черты в его условном обозначении. Наличие 2-х ступеней триггеров(ведущий-ведомый) обычно обозначается двумя буквами Т.

Использование двухступенчатых триггеров позволяет строить сложные цифровые устройства с обратными связями, что часто весьма затруднительно при использовании одноступенчатых триггеров из-за неопределенности их переключений (так называемых «гонок»).

D-триггер(триггер задержки)

D-триггер имеет один иформационный вход D и синхровход С. D-триггер можно построить из двухступенчатого синхронного RS-триггера и инвертора:

Информация (логический 0 или 1) записывается в двухступенчатый D-триггер с входа D по заднему фронту синхроимпульса и сохраняется(задерживается) до прихода следующего синхроимпульса:

D-триггер (со статической синхронизацией) может быть построен и на основе одностурпенчатого RS-триггера:

Т-триггер

Т-триггер имеет один вход (Т) и изменяет свое состояние на противоположное с приходом каждого входного импульса. Т-триггер чаще выполняется по двухступенчатой схеме, например, с использованием двухступенчатого синхронного RS-триггера или двухступенчатого D-триггера:

Временные диаграммы Т-триггера:

Jk-триггер

JK-триггер состоит из двухступенчатого RS-триггера и двух элементов И:

Вход J аналогичен входу S двухступенчатого синхронного RS-триггера, а вход К – входу R. Если J=K=0, то осуществляется режим хранения информации. Если J=K=1 или J=K=C, то c приходом каждого синхроимпульса триггер изменяет свое состояние на противоположное, т. е. работает как двухступенчатый Т-триггер. Все изменения состояний такого JK-триггера осуществляется по заднему фронту синхроимпульса.

Таким образом, JK-триггер может выполнять функции двухступенчатых RS-, D- и Т –триггеров:

Кроме рассмотренных триггеров с инверсным динамическим синхровходом производятся триггеры и с прямым динамическим синхровходом, что отмечается противоположным наклоном черты в его условном обозначении.

Задание

Используя компоненты Electronics WorkBench, соберите поочередно вышеприведенные схемы триггеров, дополнив их осциллографом и лампочками (или светодиодами) для снятия выходных сигналов, а также источником постоянного напряжения, переключателями и резисторами 1 кОм для подачи входных сигналов, по следующему образцу:

Следует учитывать, что в реальных схемах имеет место кратковременный «дребезг» контактов, возникающий при замыкании и размыкании механических контактов, который может приводить к ложным срабатываниям цифровых схем. Для подавления дребезга контактов может быть использована вышеприведенная схема на базе асинхронного RS-триггера. При этом два переключателя можно заменить одним.

Задавая с помощью переключателей различные комбинации входных сигналов, составьте таблицы переходов триггеров и временные диаграммы. Для D- и Т – триггеров синхросигналы подайте от источника прямоугольных импульсов небольшой частоты 0,2…1 Гц.

n

n

n

n

)

) )

) )

) )

) 155ТМ2

155ТМ2 561ТМ2

561ТМ2