D-триггер. Принцип работы и обозначение на схемах.

Принцип работы и обозначение D-триггера

Возможно, вы уже познакомились с RS-триггером и JK-триггером на страницах сайта Go-radio.ru, но разговор о триггерах был бы неполным без упоминания D-триггера. D-триггер (англ. Delay-задержка) имеет свойственные всем триггерам входы: S (установка), R (сброс), С — вход синхронизации и D-вход. Ещё D-триггер называют – триггер с динамическим управлением. Работа D-триггера аналогична работе JK-триггера с небольшими отличиями.

Особенностью триггера является то, что при подаче на вход D низкого уровня (логического 0) и по спаду импульса на входе С, триггер сбрасывается в нулевое состояние. Если на входе D высокий уровень (логическая 1), то по спаду импульса на входе С триггер устанавливается в единицу.

Что такое спад импульса? Объяснить это лучше наглядно, например, с помощью рисунка. Вот взгляните.

Напомним, что вход C является входом синхронизации или, по-другому, входом тактирования. Он нужен для того, чтобы упорядочить работу множества отдельных микросхем в одной общей схеме.

На принципиальных схемах D-триггер обозначается следующим образом.

Бывает, что изображение на схеме несколько отличается. Но, несмотря на это, на условном обозначении D-триггера всегда присутствует указание входа «D«.

В cерии логических микросхем К561, выполненных по технологии КМОП, есть наборы D-триггеров. Например, микросхема К561ТМ2 содержит два D-триггера в одном корпусе. А в составе микросхемы К561ТМ3 уже четыре D-триггера. Для построения несложных счётчиков и делителей частоты эти микросхемы гораздо удобнее.

Вот так обозначается на схемах микросхема К561ТМ2 (К176ТМ2, К564ТМ2). Импортный аналог микросхемы К561ТМ2 — CD4013, HEF4013.

Как видим, в составе этой микросхемы два D-триггера. Для подключения питания к этой микросхеме используются вывод 14 (это плюс «+», VDD) и вывод 7 (это минус «-«, GND).

Для подключения питания к этой микросхеме используются вывод 14 (это плюс «+», VDD) и вывод 7 (это минус «-«, GND).

Для того чтобы получить из D-триггера делитель частоты на два достаточно соединить инверсный выход со входом D. То есть соединяются выводы 2 и 5 (12 и 9), а импульсы подаются на вход С.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Справочник «Цифровые Интегральные Микросхемы»

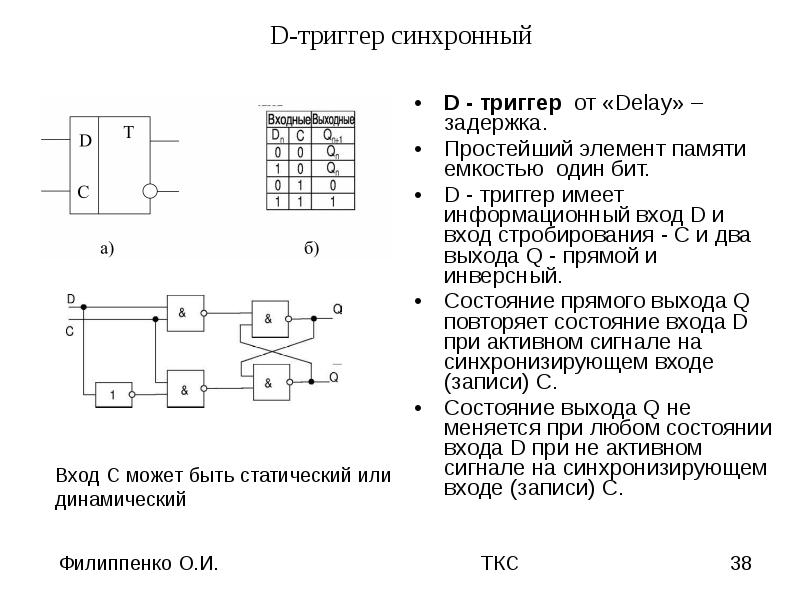

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ]2.5.2. D-триггеры

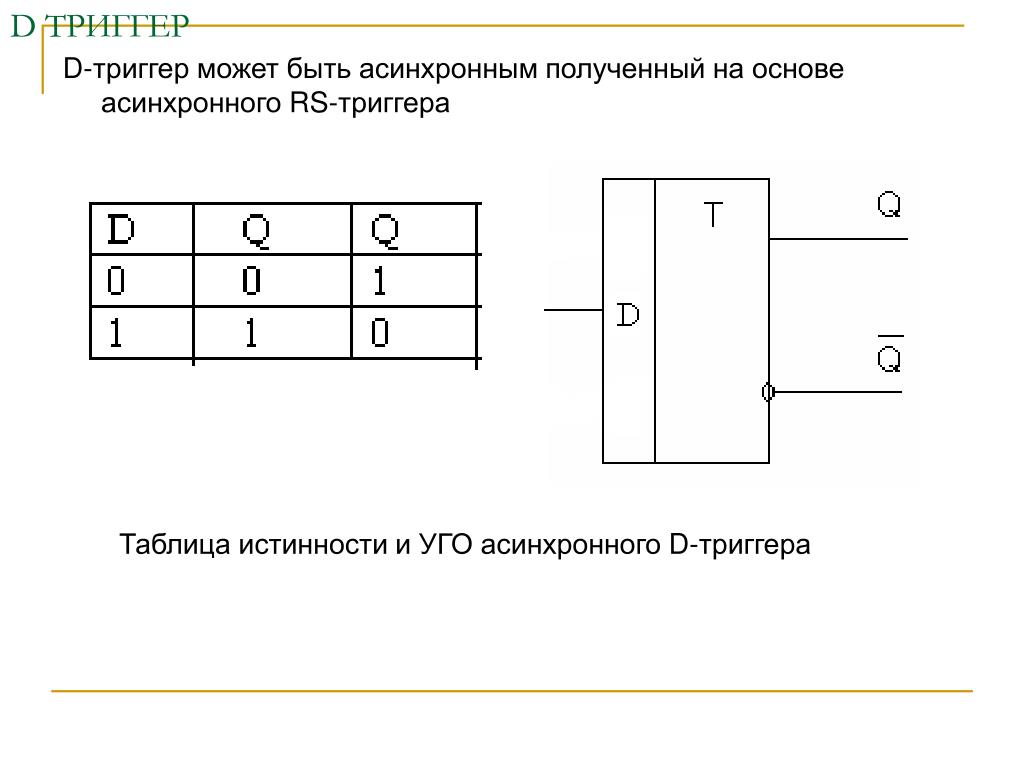

D-триггером называется триггер с одним информационным

входом, работающий так, что сигнал на выходе после

переключения равен сигналу на входе D до переключения,

т. е. Qn+1=Dn Основное назначение D-триггеров — задержка

сигнала, поданного на вход D. Он имеет информационный

вход D (вход данных) и вход синхронизации С. Вход

синхронизации С может быть статическим (потенциальным)

и динамическим.

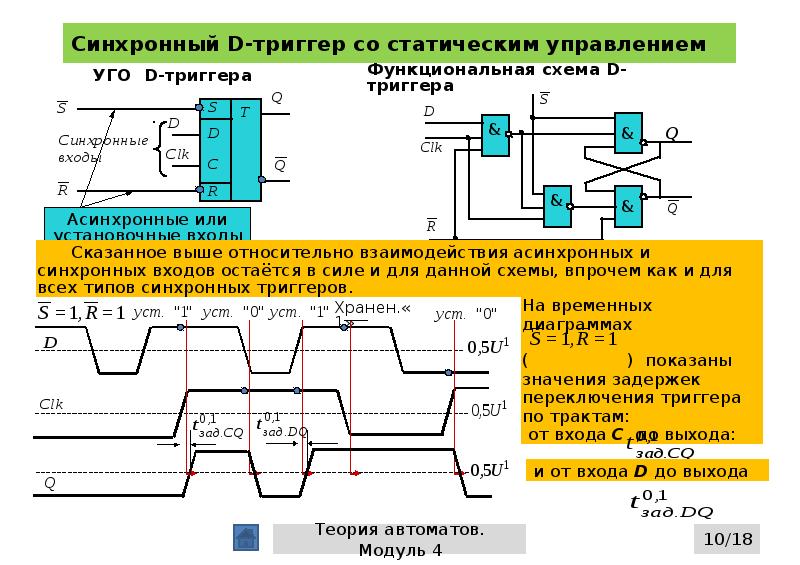

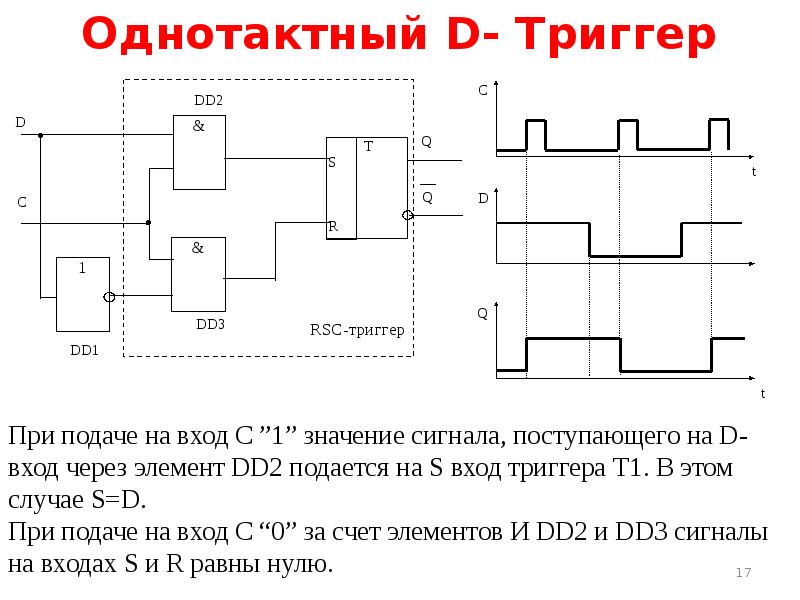

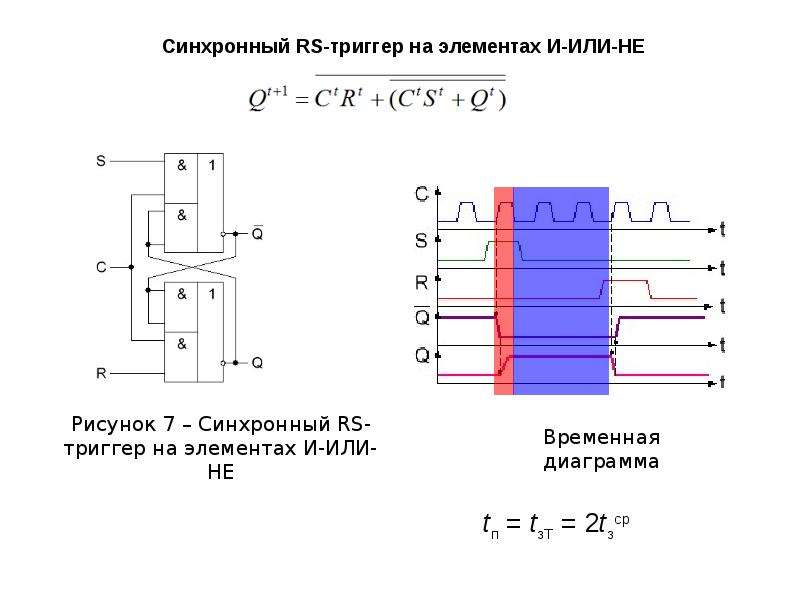

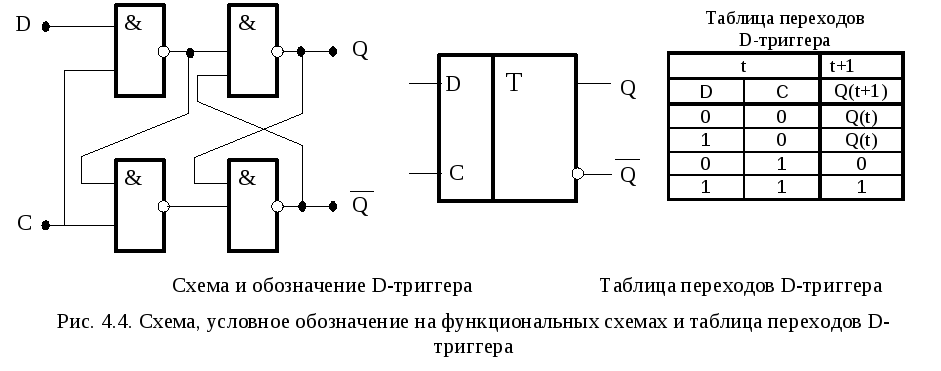

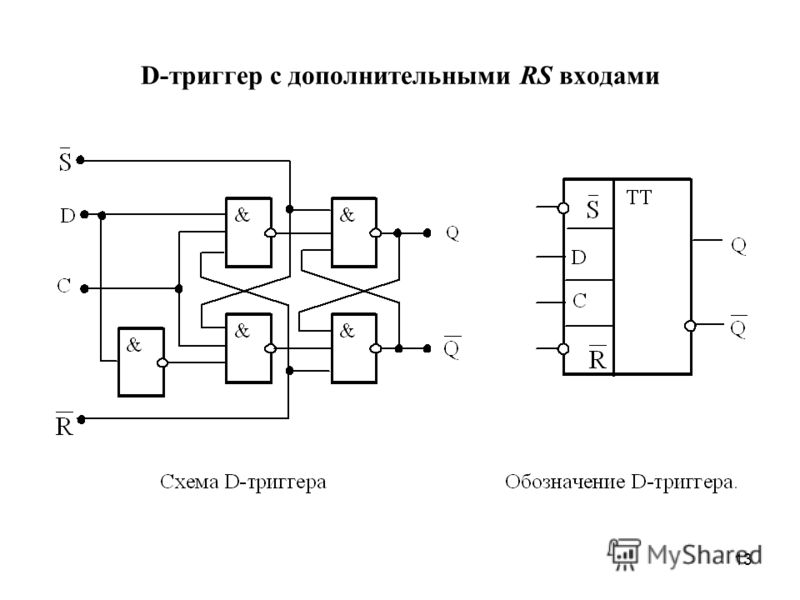

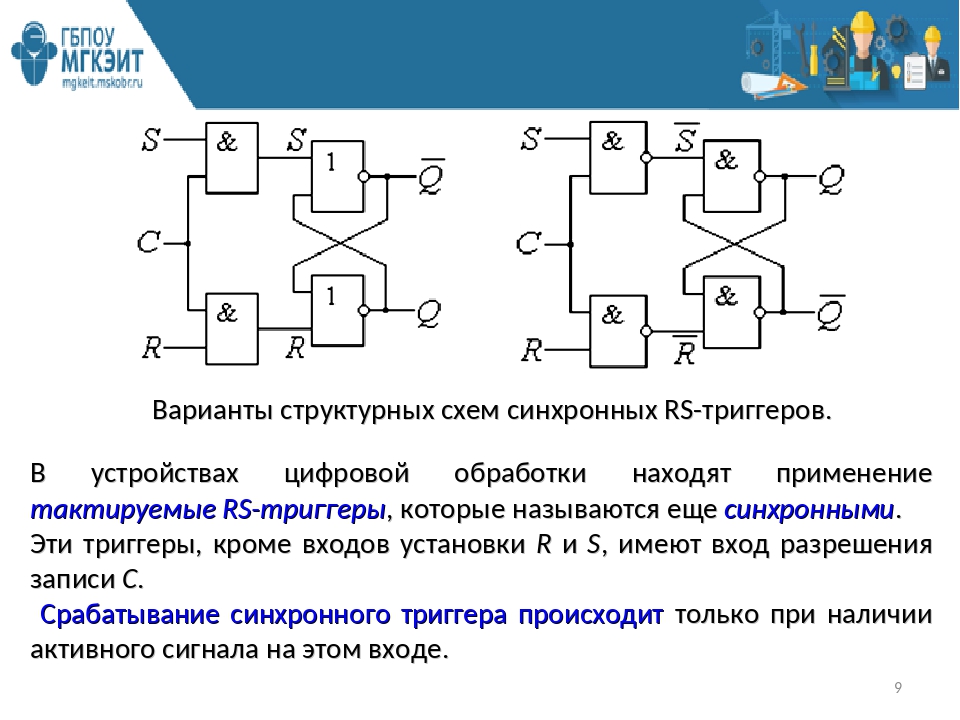

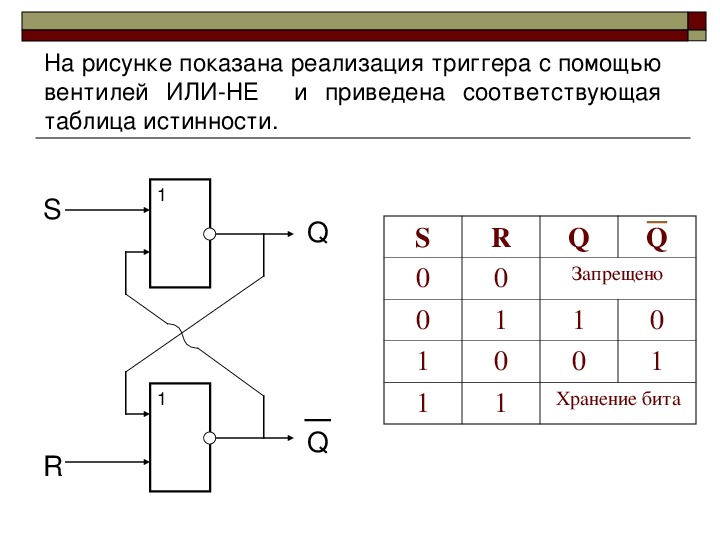

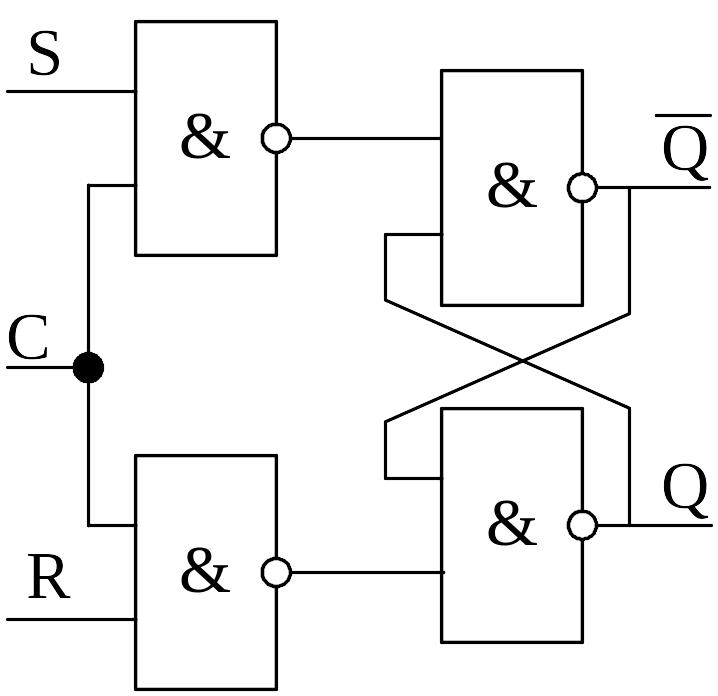

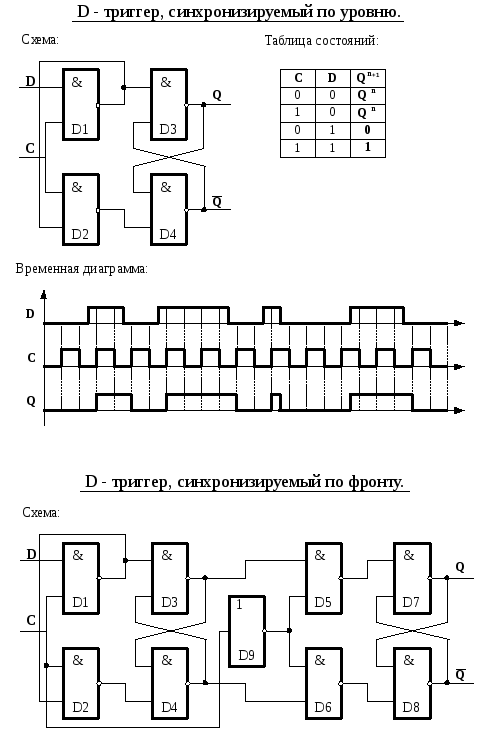

D-триггеры могут быть построены по различным схемам. На рис. 2.43,а показана схема одноступенчатого D-триггера на элементах И-НЕ и его условное обозначение. Триггер имеет прямые статические входы (управляющий сигнал — уровень логической единицы). На элементах DD1.1 и DD1.2 выполнена схема управления, а на элементах DD1.3 и DD1.4 асинхронный RS-триггер.

Рис. 2.43. Синхронный D-триггер: а — схема D-триггера на элементах И-НЕ и условное обозначение;

б — временные диаграммы; в — преобразование синхронного RS-триггера в синхронный D-триггер;

г — временные диаграммы записи и считывания.

Если уровень сигнала на входе С = 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе D. При этом на входы асинхронного RS-триггера с инверсными входами (DD1.3 и DD1.4) поступают пассивные уровни /S = /R = 1.

При подаче на вход синхронизации уровня С = 1 информация на прямом выходе будет повторять информацию, подаваемую на вход D.

Следовательно, при C=0 Qn+1=Qn, а при C=l Qn+1=Dn. Временные диаграммы, поясняющие работу D-триггера, приведены на рис. 2.43,б.

D-триггер возможно получить из синхронного RS-триггера,

если ввести дополнительный инвертор DD1.1 между входами

S и R (рис. 2.43,в). В таком триггере состояние неопределенности

для входов S и R исключается, так как инвертор DD1.1 формирует

на входе R сигнал /S. Временные диаграммы записи в D-триггер

напряжений высокого и низкого входных уровней и их считывание

приведены на рис. 2.43,г. Обязательным условием правильной

работы D-триггера является наличие защитного временного

интервала после прихода импульса на

вход D перед тактовым импульсом (вход С).

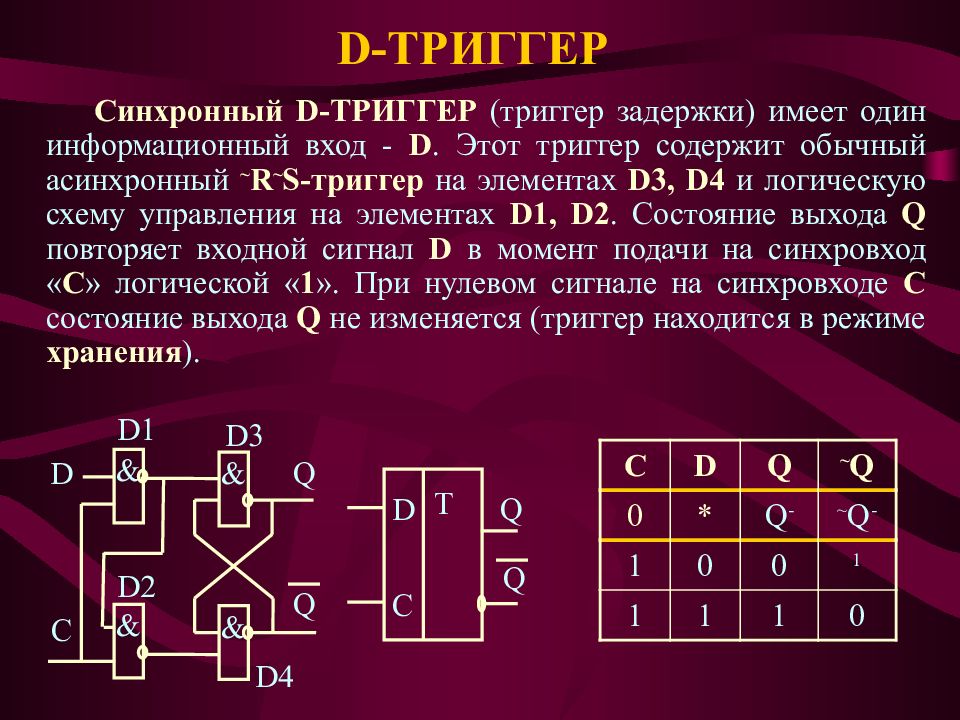

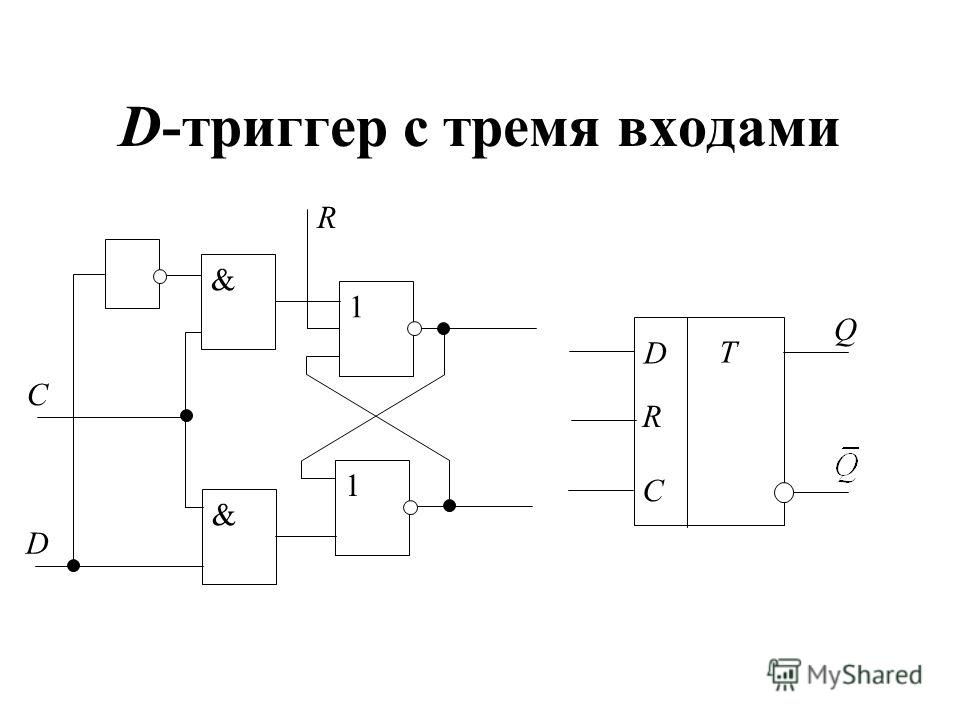

Комбинированные D-триггеры имеют дополнительные входы асинхронной установки логических 0 и 1 — входы S и R. Схема и условное обозначение одного такого триггера представлены на рис. 2.44. Триггер собран на шести элементах И-НЕ по схеме трех RS-триггеров. Входы /S и /R служат для первоначальной установки триггера в определенное состояние.

Рис. 2.44. Комбинированный D-триггер и его условное обозначение.

Если C=D=0, установить /S=0, а /R=1, то элементы

DD1.1 … DD1.5 будут закрыты, а элемент DD1.6 будет открыт,

т. е. Q=l, /Q=0. При снятии нулевого сигнала со входа /S,

откроется элемент DD1.1, состояние остальных элементов не

изменится. При подаче единичного сигнала на вход С на всех

входах элемента DD1.3 будут действовать единичные сигналы

и он откроется, а элемент DD1.6 закроется: /Q = 1. Теперь

на всех входах элемента DD1.5 действуют единичные сигналы

и он будет открыт: Q = 0. Следовательно, после переключения

триггера сигнал на выходе Q стал равным сигналу на входе D

до переключения: Qn+1=Dn=0.

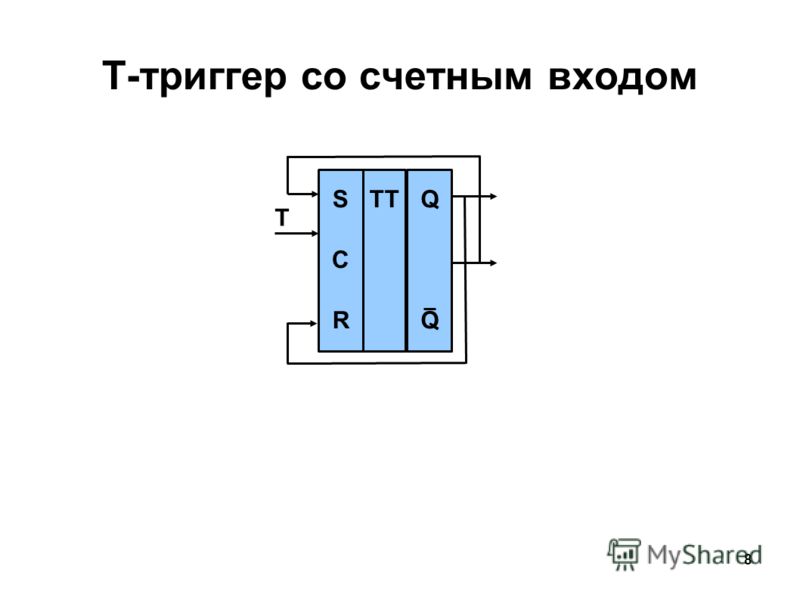

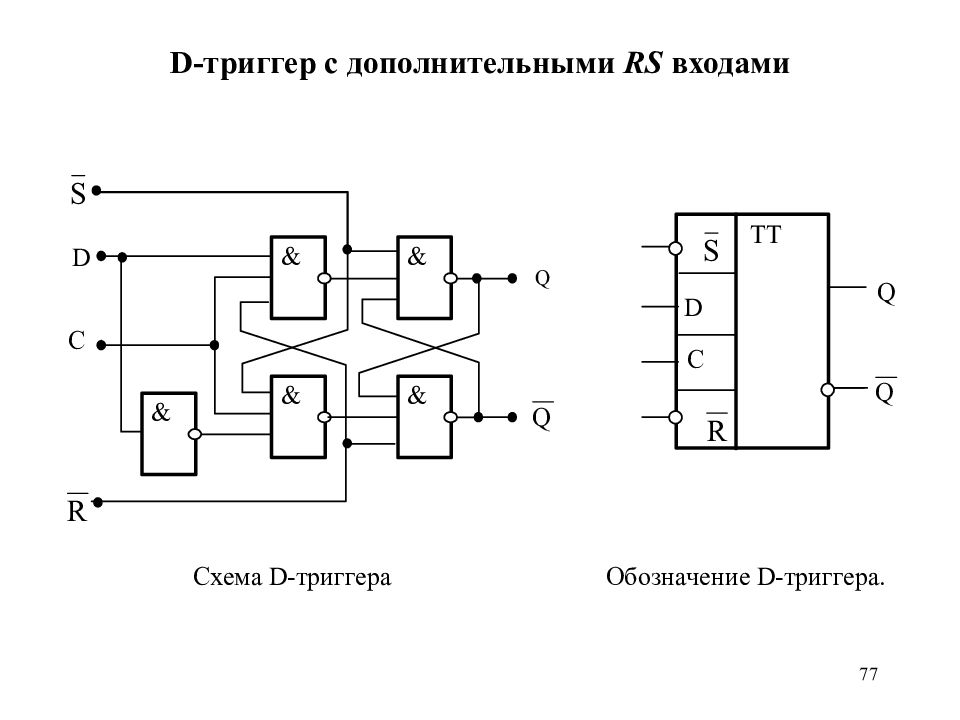

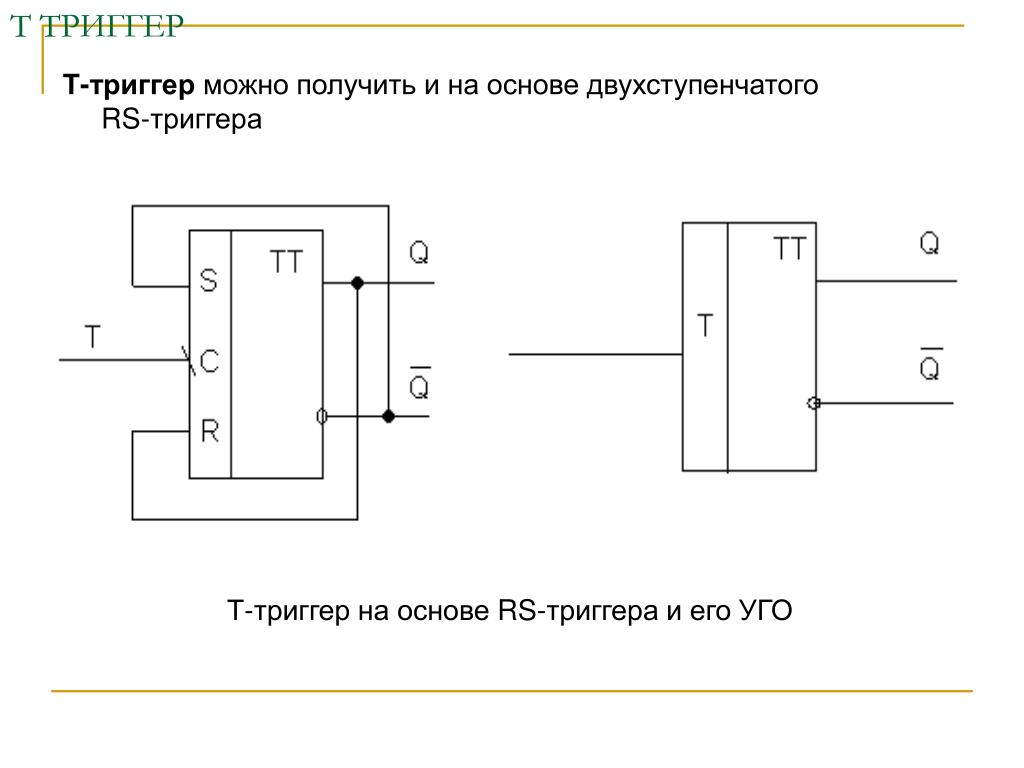

D-триггер с динамическим входом C может работать как T-триггер. Для этого необходимо вход С соединить с инверсным выходом триггера /Q (рис. 2.45,а). Если на входе D поставить дополнительный двухвходовый элемент И и инверсный выход триггера /Q соединить с одним из входов элемента И, а на второй вход подать сигнал EI, то получим T-триггер с дополнительным разрешением по входу (рис. 2.45,б).

Рис. 2.45. Схемы преобразования D-триггера. а — преобразование D-триггера в T-триггер и его временная диаграмма работы;

б — преобразование D-триггера в в T-триггер с дополнительным входом расширения EI и его временная диаграмма работы;

Микросхема ТМ2 содержит два независимых комбинированных D-триггера,

имеющих общую цепь питания. У каждого триггера имеется один

информационный вход D, вход синхронизации С и два дополнительных

входа /S и /R независимой асинхронной установки триггера в единичное

и нулевое состояния, а также комплементарные выходы Q и /Q (рис. 2.46).

Логическая структура одного D-триггера (рис. 2.46) содержит следующие

элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный

синхронный RS-триггер (Т1) записи логической единицы (высокого уровня)

в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи

логического нуля (низкого уровня) в основной триггер.

Входы /S и /R — асинхронные, потому что они работают (сбрасывают состояние

триггера) независимо от сигнала на тактовом входе, активный уровень

для них низкий (т. е. инверсные входы /S и /R).

2.46).

Логическая структура одного D-триггера (рис. 2.46) содержит следующие

элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный

синхронный RS-триггер (Т1) записи логической единицы (высокого уровня)

в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи

логического нуля (низкого уровня) в основной триггер.

Входы /S и /R — асинхронные, потому что они работают (сбрасывают состояние

триггера) независимо от сигнала на тактовом входе, активный уровень

для них низкий (т. е. инверсные входы /S и /R).

Рис. 2.46. Структура D-триггера микросхемы ТМ2

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы /S и /R. В это время входы D и С не влияют.

Если на входы /S и /R одновременно подать сигнал низкого уровня

(логический нуль), то на обоих выходах триггера Q и /Q будет высокий

уровень (логическая единица). Однако после снятия этих сигналов со

входов /S и /R состояние триггера будет неопределенным. Поэтому

комбинация /S=/R=0 для этих входов является запрещенной.

Поэтому

комбинация /S=/R=0 для этих входов является запрещенной.

Загрузить в триггер входные уровни В или Н (т. е. логические 1 или 0) можно, если на входы /S и /R подать напряжение высокого уровня: /S=/R=1. Сигнал от входа D передается на выходы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого* к высокому). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний, табл. 2.24), необходимо уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С. Причем этот защитный временной интервал должен быть больше времени задержки распространения сигнала в триггере (определяется по справочнику).

| Режим работы | Входы | Выходы | ||||

|---|---|---|---|---|---|---|

| /S | /R | D | C | Q | /Q | |

| Асинхронная установка | 0 | 1 | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | 0 | 1 |

| неопределенность | 0 | 0 | Х | Х | 1 | 1 |

| Загрузка «1» (установка) | 1 | 1 | 1 | _/ | 1 | 0 |

| Загрузка «0» (сброс) | 1 | 1 | 0 | _/ | 0 | 1 |

Цоколевка микросхемы ТМ2 приведена на рис. 2.47,

а основные параметры см. в табл. 2.20а.

2.47,

а основные параметры см. в табл. 2.20а.

Рис. 2.47. Условное обозначение и

цоколевка микросхемы ТМ2

Микросхемы ТM5 и ТМ7 содержат по четыре D-триггера, входы синхронизации

которых попарно соединены и обозначены как входы разрешения загрузки EI.

Если на такой вход разрешения EI подается напряжение высокого уровня,

то информация, поступающая на входы D, передается на выходы триггеров.

При напряжении низкого уровня на входе разрешения EI на выходах триггеров

сохраняются предыдущие состояния (состояние входов D безразлично).

В триггерах будет зафиксирована информация, имевшаяся на входах D, если

состояние входа EI переключить от напряжения высокого уровня к низкому.

Такие триггеры используются в качестве четырехразрядного регистра

хранения информации с непарным тактированием разрядов, а также в

качестве буферной памяти и элемента задержки. Каждый триггер микросхемы

ТМ5 имеет только прямой выход Q, а каждый триггер микросхемы ТМ7 имеет

прямые Q и инверсные /Q выходы. Функциональные схемы, цоколевка,

схема одного D-триггера и временные диаграммы работы приведены

на рис. 2.48, а, основные параметры триггеров даны в

табл. 2.20, состояния триггеров даны в

табл. 2.25.

Функциональные схемы, цоколевка,

схема одного D-триггера и временные диаграммы работы приведены

на рис. 2.48, а, основные параметры триггеров даны в

табл. 2.20, состояния триггеров даны в

табл. 2.25.

Рис. 2.48. Функциональные схемы, цоколевки, структура D-триггера и временные диаграммы микросхем ТМ5, ТМ7.

| Режим работы | Входы | Выходы | ||

|---|---|---|---|---|

| EI | D | Qn+1 | /Qn+1 | |

| Разрешение передачи данных на выход | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | |

| Защелкивание данных | 0 | Х | Qn=1 | /Qn=0 |

Микросхемы. TM8 и ТМ9 содержат четыре и шесть D-триггеров соответственно. Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня)

и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня)

и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Рис. 2.48. Функциональные схемы и цоколевки микросхем ТМ8 и ТМ9.

Триггеры микросхемы ТМ9 имеют только прямые входы Q, а триггеры ТМ8 — прямые и инверсные выходы Q и /Q. На входах C и /R поставлены дополнительные инверторы. Микросхемы К1533ТМ8, К1533ТМ9 имеют повышенную нагрузочную способность, т.е. на каждом из выходов поставлены дополнительные инверторы. Функционрированне триггеров в микросхемах ТМ8 и ТМ9 соответствует таблице состояний (табл. 2.26).

| Режим работы | Входы | Выходы | |||

|---|---|---|---|---|---|

| /R | D | C | Qn+1 | /Qn+1 | |

| Сброс | 0 | X | X | 0 | 1 |

| Загрузка «1» | 1 | 1 | _/ | 1 | 0 |

| Загрузка «0» | 1 | 0 | _/ | 0 | 1 |

Установка всех триггеров в состояние Q = 0 произойдет, когда на

асинхронный вход /R подать напряжение низкого уровня — 0. Входы С и D в это время не действуют. Информацию от входов D можно

загрузить в триггеры, если на вход /R подать напряжение высокого

уровня — 1. Тогда при подаче на вход синхронизации С положительного

перепада напряжения (фронта импульса) и предварительно поданного

на вход D напряжения высокого или низкого уровня появится на

выходе Q высокий или низкий уровень.

Входы С и D в это время не действуют. Информацию от входов D можно

загрузить в триггеры, если на вход /R подать напряжение высокого

уровня — 1. Тогда при подаче на вход синхронизации С положительного

перепада напряжения (фронта импульса) и предварительно поданного

на вход D напряжения высокого или низкого уровня появится на

выходе Q высокий или низкий уровень.

D-триггер с работой по уровню (защелка) и по фронту — Help for engineer

D-триггер с работой по уровню (защелка) и по фронту

D-триггер получил название от английского слова «delay» — задержка, которая реализуется подачей сигналов на вход синхронизации. В раннее рассмотренном RS-триггере было два входных сигнала, но для передачи двоичного кода достаточно одного входа с разными уровнями напряжения: высокий (1) и низкий (0). На два входа нельзя было подавать единицу одновременно, поэтому в D триггере эти входы объединены с помощью инвертора (рисунок 1 а), что исключает возможность возникновения запрещенного состояния.

Рисунок 1 – а) усовершенствованная схема RS-триггера б) графическое изображение D-триггера

Триггер D может работать по уровню сигнала, он еще называется защелка. В таком устройстве нужно ограничивать длительность синхронизирующего сигнала, потому что пока синхросигнал подается — переходной процесс со входа поступает на выход.

Схема зещелки собранная на логических элементах 2ИЛИ-НЕ (синий провод – логический ноль, красный – единица):

Временная диаграмма работы:

Триггер-защелка включается в работу только по синхросигналу. Когда на С логический ноль, то выход Q хранит прошлое записанное в него состояние, при этом уровень напряжения на входе D никак не может на него повлиять. Если подать «1» на вход синхронизации, то устройство будет работать в режиме «прозрачности» — выходной сигнал мгновенно повторяет сигнал входа. Но при отключении синхросигнала в памяти триггера останется последнее состояние входа и именно оно будет на Q. То есть получается «защелкнутый входной сигнал».

То есть получается «защелкнутый входной сигнал».

Исходя из описанного принципа работы, составим таблицу истинности:

Х означает, что состояние не имеет значения, иногда обозначают, как «тильда»

D-триггер, работающий по фронту, не требует контроля длительности синхронизирующего (тактового) сигнала, потому что фронт сигнала С проходит практически мгновенно (не может длиться продолжительное время). Триггер, который будет запоминать информацию лишь по фронту синхросигнала, можно построить из двух D-триггеров, тактовый сигнал на которые будет подаваться в противофазе:

Соответственно, схему на логических элементах можно сконструировать с помощью четырех ИЛИ-НЕ и одного инверсного блока:

На рисунке 2 (анимации) в правом верхнем углу для упрощения восприятия, на первом кадре написана цифра «1». Начиная рассматривать с этого кадра, будет проще проследить принцип работы (синий цвет – «0», красный – «1»).

Временная диаграмма Д-триггера, работающего по фронту

Рассмотрим принцип работы. Q’ – выход первого триггера, Q – второго. Так как тактовый сигнал на первый и второй вход подаются инверсировано, то когда один находится в режиме хранения, другой пропускает информацию со входа на выход. По диаграмме видно, что значение на выходе триггера Q изменится только по спадающему фронту синхронизирующего (тактового) сигнала С. То есть значение на Q будет соответствовать величине напряжения на входе D в момент изменения синхросигнала с 1 на 0.

Так как данное устройство состоит из двух более простых устройств, то условное его обозначение следующее:

Где ТТ означает наличие в строении двух простых триггеров, а «треугольник» около входа С – работу триггера по фронту сигнала.

Недостаточно прав для комментирования

Принцип работы и таблица истинности D-триггеров: синхронных и двухступенчатых

В цифровых схемах d триггер выполняет функции единичного запоминающего устройства. Такие решения применяют для оперативного и длительного хранения информации. Их используют в блоках фильтрации сигналов. Представленные ниже сведения помогут ознакомиться не только с теорией, но и с методикой решения отдельных практических задач.

Такие решения применяют для оперативного и длительного хранения информации. Их используют в блоках фильтрации сигналов. Представленные ниже сведения помогут ознакомиться не только с теорией, но и с методикой решения отдельных практических задач.

Рабочая схема триггера

Что такое Д триггерТриггерами называют устройства, способные длительное время поддерживать определенное состояние на выходе. Как правило, они контролируют соответствующие уровни напряжения. Изменения происходят при определенной комбинации входных сигналов.

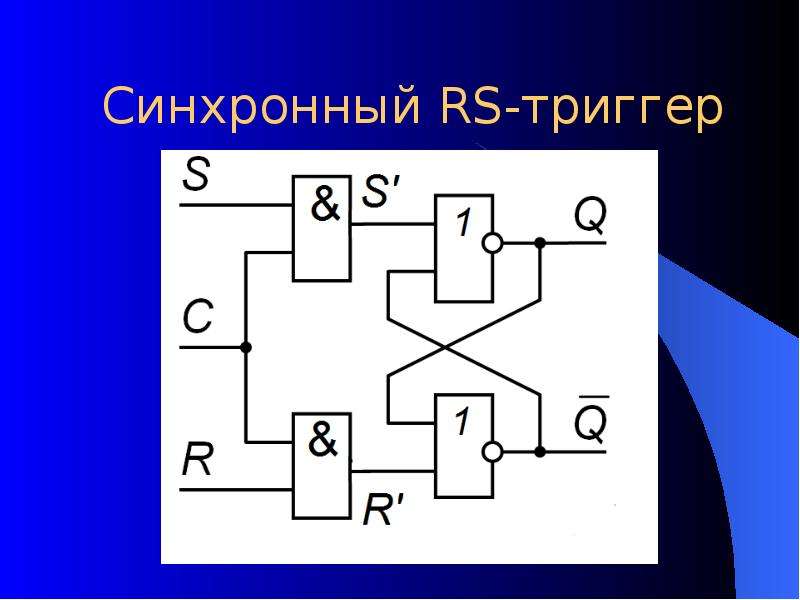

Простейшие устройства этой категории создают по схеме RS. Они запоминают состояние сигнала, поданного на один из входов. Чтобы устранить процесс сбоев, который вызывают паразитные колебания при переходе сигнала из ноля в единицу и обратно, применяют синхронизацию. Этим дополнительным сигналом устанавливают точное время (интервал) для возможных изменений.

В обозначении Д триггера отмечена главная особенность. Буквой «Д» (D лат. ) маркируют вход, на который подают информационный сигнал. Другой («С») используют для синхронизации записи. Отсутствие активности на нем исключает изменение базового состояния. Такое решение, в отличие от RS, позволяет изменять состояние с применением только одного источника данных.

) маркируют вход, на который подают информационный сигнал. Другой («С») используют для синхронизации записи. Отсутствие активности на нем исключает изменение базового состояния. Такое решение, в отличие от RS, позволяет изменять состояние с применением только одного источника данных.

Проще всего представить функциональность на основе элементарных логических элементов. Второе название триггеров данной категории – «защелка», наглядно поясняет основные принципы работы.

Схема Д триггера

На рисунке, кроме основных, отмечены входы. Вне зависимости от сигналов синхронизации, с их помощью переводят изделие в нулевое или единичное состояние. Таким образом реализован принцип приоритетности, так как активация S и R блокирует входные вентили C.

Виды D триггераТиповые решения с применением представленных логических элементов рассмотрены ниже. Допустимы другие комбинации для удвоения частоты и решения других задач.

Рассмотрим на упрощенном примере основы функционирования. Для этого уберем сервисные входы. Диаграммы демонстрируют изменение сигналов при разных комбинациях управления. В таблице показаны состояния для записи единиц и нулей, а также в режиме хранения.

D триггер: таблица истинности, схема, временные графики

Если подать на С единицу (ноль), изменение на D сопровождается появлением аналогичного сигнала на выходе Q. Следует обратить внимание на временные задержки. Пока синхронизация отсутствует, изделие не срабатывает, вне зависимости от состояния информационного входа.

В соответствующих режимах:

- Запоминается предыдущее состояние на выходе;

- Обеспечивается «прозрачность» – практически мгновенное повторение входных значений;

- Фиксируется выходной сигнал («защелкивается»), когда сигнала С нет.

В таких схемах объединяют последовательно два триггера. Первый – настраивают по увеличению входного сигнала. Второй – по спаду. Как видно на рисунке, состояние изменяется не одновременно с появлением новой информации, а с определенной временной задержкой, длительность которой равна одному полному рабочему циклу сигнала синхронизации.

Первый – настраивают по увеличению входного сигнала. Второй – по спаду. Как видно на рисунке, состояние изменяется не одновременно с появлением новой информации, а с определенной временной задержкой, длительность которой равна одному полному рабочему циклу сигнала синхронизации.

Схема и временная диаграмма двухступенчатого триггера

Принцип работыВо всех схемах имеет значение длительность рабочих реакций, которая определяет время записи (стирания). Определенное значение имеет помехоустойчивость. В следующих разделах рабочие процессы рассмотрены подробно.

Элементы с управлением по уровнюВ этом варианте изменение состояния происходит только при высоком уровне синхронизирующего сигнала. При соответствующем положении устройство копирует изменения на входе с небольшой технологической задержкой. Если на С – ноль, реакция на выходе отсутствует.

Временная диаграмма для управления триггером по уровню

Элементы с управлением по фронтуВ соответствии с названием, здесь реализована схема управления по фронту (переднему и заднему). С помощью временной диаграммы можно рассмотреть рабочие циклы внимательно.

С помощью временной диаграммы можно рассмотреть рабочие циклы внимательно.

Изменение состояния при разных информационных (управляющих) сигналах

Допустим, что для управления выбран передний фронт. При С=0 состояние триггера не изменяется, вне зависимости от информационных сигналов, – одновременно с прохождением переднего фронта записывается аналогичное уровню D. В данном примере – единица. Следующие изменения происходят по такому же алгоритму.

Чтобы расширить базовую функциональность, устройство дополняют представленными выше сервисными входами (R и S). С их помощью состояние устанавливают произвольным образом (1 или 0) в любой нужный момент. Разумеется, для выполнения таких действий понадобятся дополнительные элементы управления.

К сведению. В этом варианте не имеет значения длительность управляющего сигнала. Для функционирования схемы его можно подать с применением инвертора в противофазе на два триггера Д типа, соединенные последовательно. Такое решение будет сопровождаться изменением состояния по заднему фронту (спаду).

Такое решение будет сопровождаться изменением состояния по заднему фронту (спаду).

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

Схема реализации триггера на транзисторах

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.

Условные обозначения Д триггеров на схемеСтандарты:

- Т – триггер;

- D – информационный вход;

- C (треугольник) – синхронизация;

- S и R – входы для принудительного перевода состояния в ноль или единицу.

Условно графическое обозначение (УГО) двух последовательно подключенных триггеров

При работе с цифровыми схемами, кроме основных логических функций, надо учитывать базовые принципы радиотехники. Для поддержания хорошей работоспособности необходимо качественное электропитание. Особое внимание уделяют минимизации паразитных переходных процессов, защите от внешних неблагоприятных воздействий. Уменьшает количество сбоев эффективная защита от электромагнитных помех.

Для поддержания хорошей работоспособности необходимо качественное электропитание. Особое внимание уделяют минимизации паразитных переходных процессов, защите от внешних неблагоприятных воздействий. Уменьшает количество сбоев эффективная защита от электромагнитных помех.

принцип работы и простейшие схемы устройств, их назначение и практическое использование

Под определение триггера попадают довольно много схем в электронных устройствах. Их общая черта — это способность находиться в одном из двух устойчивых состояний, которые сменяют друг друга под воздействием какого-либо сигнала. Кроме того, триггеры обладают двоичной памятью, то есть могут запоминать своё положение и оставаться в нём даже после прекращения влияния переключающего фактора, таким образом запоминая разряд числа в двоичном коде.

Описание и принцип работы

В широком смысле триггером (от английского trigger — спусковой крючок, запускающий механизм) называют любой импульс или событие, ставшее причиной чего-либо. Термин применяют в электронике, психологии, медицине, программировании и других областях деятельности. В создании микросхем и других устройств так называют элемент, который способен принимать одно из двух стойких состояний (0 или 1) и сохранять их в течение долгого времени.

Положение триггера зависит от получаемых им сигналов на прямом и инверсном выходах. Отличительной чертой устройства является то, что его переход из одной позиции в другую обусловлен не только получением внешних инструкций, поступающих от выбранной системы управления, но и посредством обратной связи. То есть текущее положение элемента зависит от предыстории его работы.

Триггеры могут сохранять свою память только при постоянном поступлении напряжения. Если его отключить, а затем снова подключить, устройство перейдёт в случайное состояние. Поэтому при конструировании устройства важно предусмотреть способ, которым он изначально будет вводиться в правильное положение.

Поэтому при конструировании устройства важно предусмотреть способ, которым он изначально будет вводиться в правильное положение.

В основе любого триггера лежит схема, которая состоит из двух логических элементов типа И-НЕ либо ИЛИ-НЕ, имеющих друг с другом обратную положительную связь. Такой тип подключения позволяет системе иметь всего два возможных устойчивых состояния, из которых выбирается одно. Важной деталью является то, что после того как триггер перешёл в положение, он может сохранять его сколько угодно времени, до тех пор, пока не будет подан очередной управляющий сигнал.

Другой характерной особенностью устройств является возможность мгновенного осуществления перехода от одного состояния в другое после получения соответствующей команды. Задержка настолько мала, что её можно не учитывать при проведении расчётов.

Число входов может быть разным и зависит от требуемых функций. Если подать сигнал одновременно на два из них, то он примет произвольную позицию после прекращения их поступления. По своим функциям входы делятся на несколько типов, которые входят в две большие группы: информационные и управляющие. Первые из них получают сигналы и запоминают их в виде информации, в то время как вторые разрешают или запрещают её запись, а также выполняют функцию синхронизации. На схемах они имеют следующие обозначения:

По своим функциям входы делятся на несколько типов, которые входят в две большие группы: информационные и управляющие. Первые из них получают сигналы и запоминают их в виде информации, в то время как вторые разрешают или запрещают её запись, а также выполняют функцию синхронизации. На схемах они имеют следующие обозначения:

- S — устанавливает триггер в состояние «1» на прямом выходе;

- R — противоположен S, сбрасывает состояние обратно на «0»;

- С — вход синхронизации;

- D — принимает информацию для последующего занесения на триггер;

- T — счётный вход.

Комбинация разных типов входов и выходов определяет то, как работает триггер. Существует множество схем этих устройств, использующихся для разных целей.

Классификация триггеров

Триггерные системы отличаются друг от друга по функциональному признаку, типу управления, числу возможных состояний и уровней, способу реагирования на помехи, составу основных логических элементов и другим особенностям. Однако все они, начиная от самых простых схем и заканчивая сложными многоступенчатыми структурами с множеством состояний, работают по одинаковому принципу.

Однако все они, начиная от самых простых схем и заканчивая сложными многоступенчатыми структурами с множеством состояний, работают по одинаковому принципу.

Общие различия

Триггеры делят на несколько больших групп по функциональным и практическим различиям. Вот некоторых из них:

- По принципу управления они бывают статические (или потенциальные) и динамические. Первые реагируют на непосредственную подачу сигналов на вход, соответствующих единице или нулю. Вторые воспринимают изменение сигнала с одного на другой.

- Статические, в свою очередь, делятся на две группы: симметричные и несимметричные. Они отличаются по внутреннему строению электрических связей в схеме — у симметричных они идентичны во всех отдельных ячейках устройства. Именно они составляют основную массу триггеров.

- По функциональным особенностям. Самый частый тип такой классификации — синхронные и асинхронные. Первые приходят в действие только при смене такса с нуля на единицу или наоборот, в то время как вторые воспринимают непосредственный момент появления сигнала.

- Согласно количеству ступеней и уровней.

- По реагированию на возникновение помех триггеры можно поделить на прозрачные и непрозрачные, которые, в свою очередь, бывают проницаемыми и непроницаемыми.

- В соответствии с числом возможных устойчивых состояний. Чаще всего их два, но бывают и троичные, четверичные и прочие элементы.

- По логическому составу, количеству и соотношению элементов И-НЕ и ИЛИ-НЕ.

- Со сложной и простой логикой.

Все системы классификации триггеров взаимодействуют и дополняют друг друга. Например, двухступенчатый триггер может быть синхронным или асинхронным, иметь статическое или динамическое управление и так далее. Выделены также отдельные виды этих систем с разными названиями.

Типы устройств

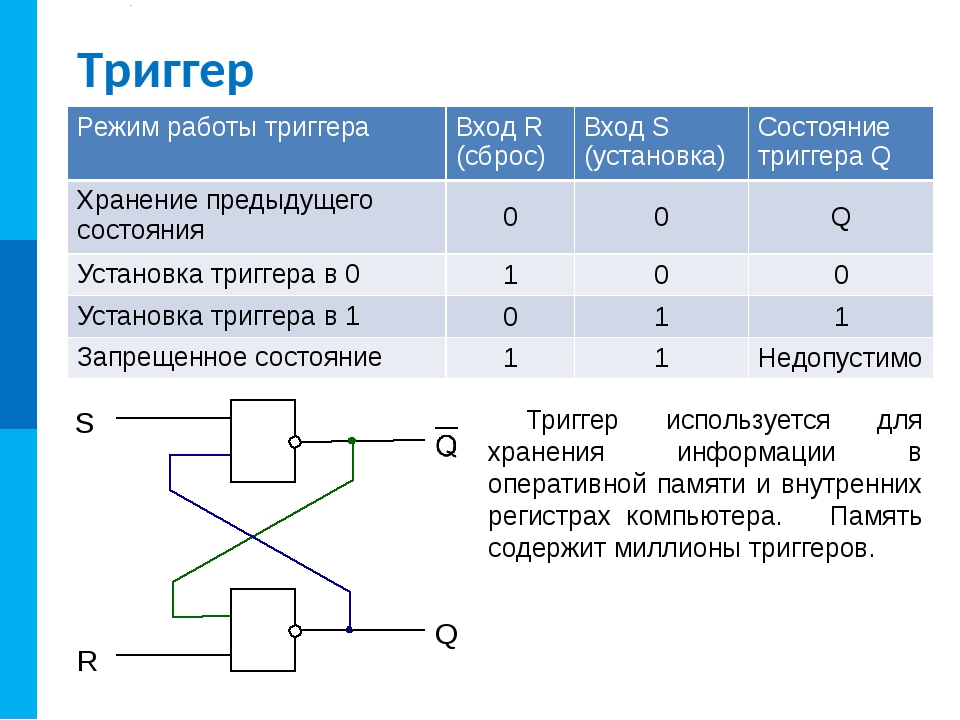

Говоря о различиях триггеров, стоит рассмотреть их отдельные типы. Самый простой из них — это RS-триггер, на основе которого строятся все остальные разновидности этих устройств, потому именно с него нужно начинать знакомство «для чайников». Это асинхронный тип системы, который состоит из двух входов — S (от английского set — установить) и R (соответственно, reset — сбросить). Он может работать как на основе логических систем И-НЕ, так и на ИЛИ-НЕ. В первом случае входы будут прямыми, во втором — инверсными.

Это асинхронный тип системы, который состоит из двух входов — S (от английского set — установить) и R (соответственно, reset — сбросить). Он может работать как на основе логических систем И-НЕ, так и на ИЛИ-НЕ. В первом случае входы будут прямыми, во втором — инверсными.

Подача активного сигнала на элемент S приведёт РС триггер в состояние логической единицы, а на R — сбросит его до нуля. Если их подать одновременно, результат зависит от реализации схемы, а когда убрать, то он будет определён случайным образом.

Из-за низкой устойчивости к помехам такой тип устройства редко применяют в электронике и микросхемах. Чаще всего его используют для устранения так называемого дребезга контактов — многократных хаотичных замыканий и размыканий, вызванных упругостью используемых для них материалов и происходящих после их подключения.

Система типа RS является асинхронной. Если возникает необходимость сохранить поступаемую на неё информацию, к устройству подключают отдельно составленную систему управления, которая будет переводить его в режимы хранения и записи.

Вторым типом является D триггер (по некоторым данным, название происходит от английского слова delay — задержка, по другим — от data — данные). В его составе должны присутствовать минимум два элемента: D-вход для получения информации и C — для синхронизации. Такие системы бывают статичными и динамичными. Первые записывают данные всё время, при котором уровень сигнала на C соответствует единице, вторые — только тогда, когда происходит перепад напряжения.

Вход на схеме D триггера изображается в виде треугольника. Когда его вершина направлена на микросхему, то его ввод прямой, а если наоборот — инверсный.

Информация на выходах в этом типе системы задерживается по сравнению с входной на один такт. Поскольку она остаётся неизменной до активации очередной команды синхронизации, устройство как бы помнит её, что и позволяет ему выполнять свои основные функции. Главная из них — это создание регистров сдвига и хранения для управления записью информации. Это очень важные элементы, без которых невозможно создать даже простейший микропроцессор.

Из-за того, что все изменения на входе D системы точно повторяются на её выходе, иногда возможны ложные срабатывания контролируемых ею устройств. Чтобы избежать этого, необходимо создать двухступенчатый триггер. Его первая ступень записывает информацию, но во вторую она не попадает до поступления сигнала перезаписи. Затем, после получения команды, первая ступень переходит в режим хранения, а вторая переписывает с неё данные, что помогает избежать состояния их «прозрачности».

Двухступенчатые триггеры обозначают как TT. Они могут управляться как статически, так и динамически.

T триггер (от слова «toggle», которое значит «переключатель») ещё называют счётчиковым, так как это простейший вариант счётчика до двух. Состоит из входа T и выхода C. Синхронные системы такого типа переключаются по каждому тактовому импульсу на выводе, в то время как работа асинхронного зависит от состояния ввода. Когда оно соответствует единице, при получении импульса на выходе триггер меняет своё значение на противоположное, а если равно нулю, то никакой реакции не происходит.

Когда оно соответствует единице, при получении импульса на выходе триггер меняет своё значение на противоположное, а если равно нулю, то никакой реакции не происходит.

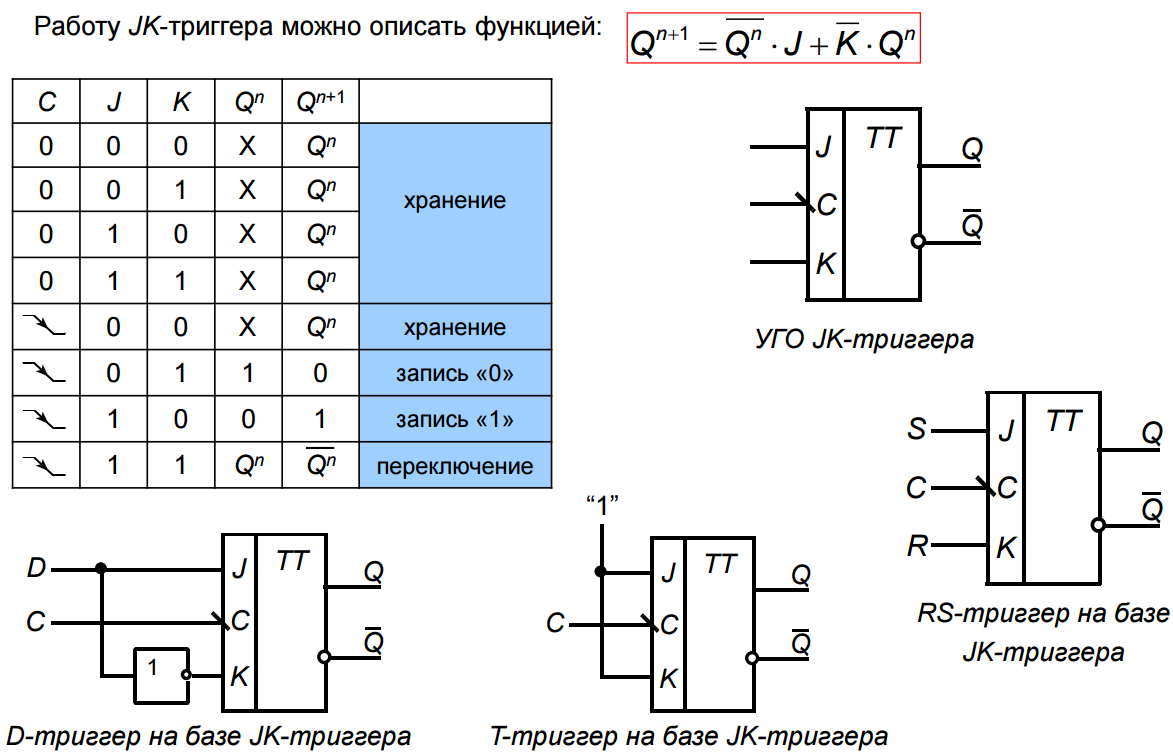

Построить такую асинхронную систему можно на основе JK или двухстепенного D-триггера. Её в основном применяют для деления частоты вдвое.

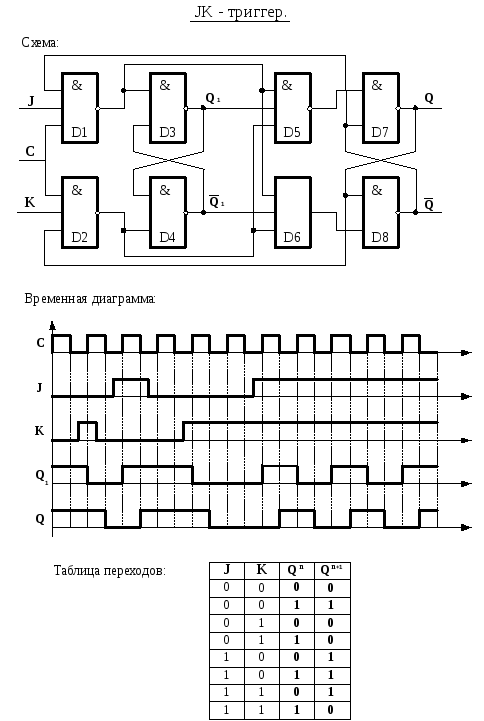

Последний из используемых наиболее часто видов — JK триггер. По принципу работы он почти идентичен RS. Его единственное отличие в том, что система типа JK меняет своё состояние на противоположное при подаче единицы на оба входа. Это помогает избежать возникающих иногда неопределённостей.

JK иногда называют универсальным триггером. У этого есть две причины. Первая — широкий спектр применения подобных элементов. Второе — тот факт, что из него можно легко получить любой другой тип системы, если это зачем-то понадобится.

Практическое использование

Чаще всего триггер используется для генерации сигнала, длительность которого соответствует продолжительности процесса в системе, которую он контролирует. Он может как непосредственно разрешать его начало и конец, так и передавать другим элементам информацию о том, что процесс запустился. Таким образом достигается контроль системы, далее нужно только позаботиться о разрешении ситуации неопределённости.

Он может как непосредственно разрешать его начало и конец, так и передавать другим элементам информацию о том, что процесс запустился. Таким образом достигается контроль системы, далее нужно только позаботиться о разрешении ситуации неопределённости.

Вторая важная функция триггера — синхронизация процессов. Это помогает избавиться от лишних и случайных импульсов, возникающих, например, когда несколько входных сигналов изменились в течение очень короткого промежутка времени. Кроме того, с помощью триггеров можно «пропустить» в систему только полные по длительности импульсы или задержать поступающую информацию.

Реализация триггеров и их применение на практике происходит в различных устройствах для запоминания и хранения памяти. Именно этот элемент представляет собой базовую ячейку ОЗУ, способную хранить 1 бит информации в статическом состоянии. Кроме того, его используют для следующих целей:

- в качестве компонентов для создания микросхем различного назначения;

- как организатор вычислительных систем;

- в регистрах сдвига и хранения;

- для изготовления полупроводниковых систем, например, транзисторов и реле.

Триггер является не только базовым элементом электроники, но и простейшим кибернетическим устройством, способным выполнять свою логическую функцию, одновременно поддерживая обратную связь. Таким образом, он используется для создания множества механизмов, целью или условием работы которых является возможность запоминания, хранения, передачи и преобразования информации. Найти триггер можно в любом приборе, начиная от систем переключения питания и заканчивая элементами цифровой микроэлектроники.

Создание запчастей для компьютеров, мобильных телефонов, роботов, управляющих панелей, транспорта и многих других приборов невозможно без использования триггеров. Применяют их и для изготовления простых схем на основе электромагнитного реле — такие конструкции всё ещё используются благодаря своей простоте и высокой защите от помех, несмотря на высокое потребление энергии.

Персональный сайт — Триггеры

Триггер — это запоминающее устройство, хранящее одно из двух состояний — либо 0 либо 1.

Содержание

Является синхронным триггером

Таким образом триггер сохраняет значение поданное на вход D.

Рис. 14. Условное обозначение D-триггера, его реализация и временные диаграммы его работы.

Рис. 15. Временные диаграммы.

При C=0 и R=S=1 возникает запрещенное состояние.

Предназначен для хранения информации на входе D при C=1

Рис. 16. Условное обозначение T-триггера.

Триггер при подаче сигнала синхронизации меняет значение на выходе на противоположное. Может иметь вход стробирования Е (при Е=0 триггер не изменяет значение на выходе ни при каких условиях).

Рис. 17. Схема T-триггера.

Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим.

Может быть реализован и на синхронном RS-триггере (рис. 5.3).

Рис. 18. Реализация T-триггера на базе RS-триггера.

18. Реализация T-триггера на базе RS-триггера.

Короткие импульсы синхронизации (менее времени срабатывания триггера) не совсем удобны для управления триггерами. Как вариант модернизации существуют двухступенчатые триггеры. Они реагируют на смену значения на входе синхронизации (фронт:0-1, либо спад:1-0).

В основе — RS триггер.

Рис. 19. Общий вид двухступенчатых триггеров.

Перезапись из первой во вторую ступень происходит при смене значения входа синхронизации.

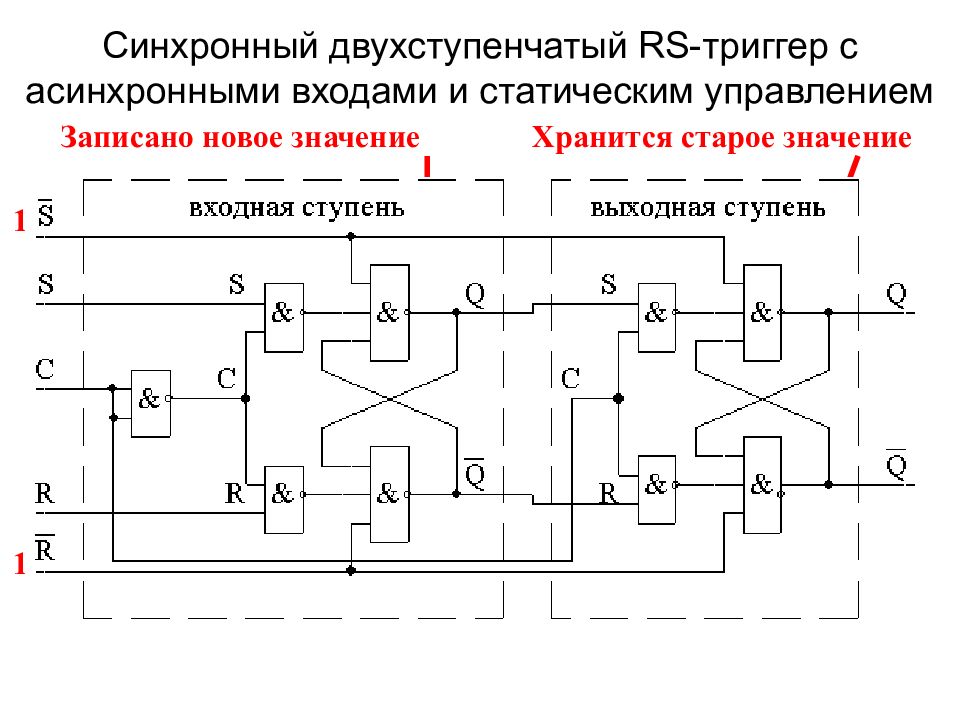

Двухступенчатый синхронный RS-триггер

Рис. 20. Схема двухступенчатого синхронного RS-триггера.

Запись происходит по спаду (изменение с 1 до 0). Основа — два обычных RS-триггера. Запись в первый триггер происходит при С=1 (второй триггер в это время в режиме хранения). При смене значения С на С=0 происходит запись значений из первого триггера во второй. Таким образом запись происходит по спаду сигнала синхронизации С (это обозначается наклонной чертой на входе синхронизации в обозначении триггера на схеме — см. рис 6.3).

рис 6.3).

Рис. 21. Условное обозначение двухступенчатого синхронного RS-триггера.

Двухступенчатый D-триггер

Рис. 22. Схема и условное обозначение двухступенчатого D-триггера.

Логика работы та же что и у RS-триггера. С=1 — запись в первый триггер, С=0 — запись из первого во второй (запись по спаду).

Двухступенчатый JK-триггер

Рис. 23. Схема двухступенчатого JK-триггера.

Поведение аналогично предыдущим триггерам кроме состояния J=1 K=1. Рассмотрим это состояние. При J=1K=1 и C=1 возникает автоколебательный процесс: 0, 1, 0, 1 и т.д. JK-триггер должен переключаться в состояние, противоположное тому, в котором находится 2-й триггер, т.е. используются только внутренние обратные связи (ОС).

Для устранения этого недостатка можно модифицировать схему (рис. 24)

Рис. 24. Схема двухступенчатого JK-триггера (без автоколебательного процесса).

Особенность схемы — наличие глубокой обратной связи (а именно, связи выходов второй ступени со входами первой ступени). В результате в триггер первой ступени записываются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно).

В результате в триггер первой ступени записываются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно).

Двухступенчатые триггеры изменяют свои значения по спаду/фронту синхроимпульса, поэтому длительность импульсов не важна.

Приведенные выше (рис. 23 и 24) схемы являются базовыми, теперь следует рассмотреть конкретные реализации.

Рис. 25. Реализация двухступенчатого JK-триггера на базе элементов «И-НЕ».

На входы D1 и D2 идет обратная связь с выходов D7, D8. Запись происходит при условии, что на выходах D1 и D2 одновременно присутствуют «1» (запись во вторую ступень). Запись в первую ступень происходит при противоположных значениях на выходах D7, D8. Запись в первую ступень происходит либо при C=1, либо при J=K=0. Перезапись — при C=0 (на выходах D1 и D2 — единицы).

Еще эту схему можно получить на базе RS-триггеров (вывод схемы — на рис. 26)

Рис. 26. Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).

Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).

Рис. 27. Пример универсального триггера.

При необходимости в схему можно ввести асинхронные входы установки в 0 и 1 — они устанавливают схему независимо от схемы управления. Триггер сч такими входами называется универсальным (т.е. он имеет и синхронные. и асинхронные входы установки). Асинхронные входы нужны для инициализации. Пример — рис 27, вход Reset переустановка всех компонентов схемы в начальное состояние. В режиме хранения требуется реагирование на синхронные входы (на их значения). При режиме записи — приоритет у асинхронных входов.

Универсальный JK-триггер

Рис. 28. Обозначение универсального JK-триггера.

Имеет как синхронные, так и асинхронные входы установки. Конъюнкции D1 и D2 могут быть и 3х-входовыми, и 6-тивходовыми, а могут иметь и большую размерность, следовательно, вместо одного сигнала J приходят несколько сигналов, объединенных конъюнкциями. Другими словами, на входе появляется «1», если на всех J — «1». Для входа K ситуация аналогичная.

Другими словами, на входе появляется «1», если на всех J — «1». Для входа K ситуация аналогичная.

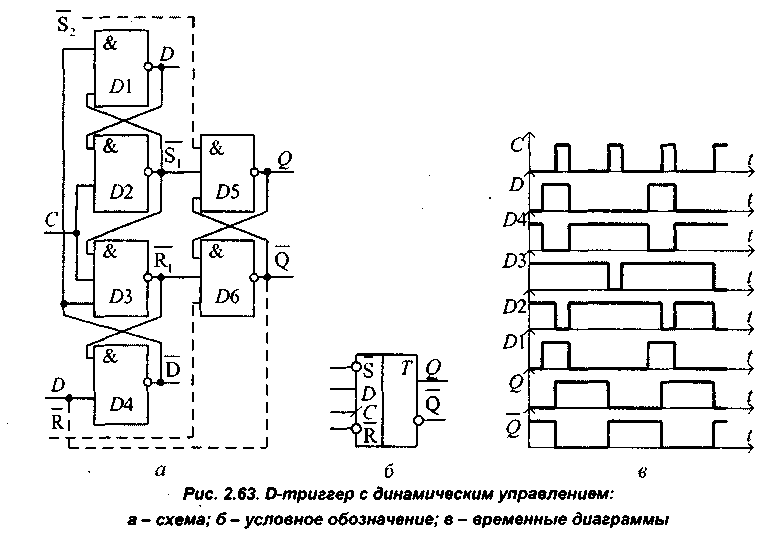

Классическая схема ступенчатого D-триггера представлена на рисунке 29.

Рис. 29. Разработка ступенчатого D-триггера.

Состоит из трех асинхронных RS-триггеров (состоят из D1-D2, D3-D4, D5-D6 соответственно). Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

T3 — с инверсными входами (рем хранение — оба значения равны «1»). Если C=0, то T2=T3=1, то есть при C=0T3=1, а при C=1 T3 определяется тем, что подается на вход D.

При C=0,D=0 в T1 записывается некоторое значение, а T2 находится в запрещенном состоянии (две «1»).

Если при C=1 T2=1 и T3=0, то произойдет переход в режим записи и произойдет запись «0» во вторую ступень.

Рассмотрим случай, когда C=0,D=1. Пусть D4=0, вход D4=0, тогда D1=1, можно наблюдать противоположную картину: T2 находится в режиме записи значения, а T1 — в запрещенном состоянии.

Пусть D4=0, вход D4=0, тогда D1=1, можно наблюдать противоположную картину: T2 находится в режиме записи значения, а T1 — в запрещенном состоянии.

Рис. 8.2. Условное обозначение ступенчатого D-триггера.

При переключении C из «0» в «1» на D3 происходит то же изменение, что и на D2 — переход из 1 в 0. Тогда T3 находится в режиме записи логической единицы:

(0)Q→1 (1)¯Q→0При C=1 значение на входе D поменяется: 1→0, выход D4 установится в значение логической «1», поэтому D1 станет равным 1 (его значение на выходе не меняется, на D2 — то же самое (только там — логический 0), поэтому значение на выходе D3 не меняется за счет D1 и D2).

При C=1 значение на входе D изменяется в порядке 1→0→1, значение D3 меняться не будет. Следовательно, при C=0 на выходе значение не будет меняться, при C=1 значение на выходе тоже не меняется. Таким образом, запись производится при переключении с 0 на 1 (по фронту).

- Первый триггер — для фиксации того, что хотим записать «0»;

- Второй триггер — для фиксации того, что хотим записать «1».

В итоге, при C:0→1 происходит запись, то есть переключение в другое состояние (или в запрещенное состояние).

Рис. 30. Условное обозначение ступенчатого D-триггера.

Рис. 31. Преобразование ступенчатого D-триггера в универсальный.

Рис. 32. Условное графическое обозначение универсального D-триггера.

КОМБИНИРОВАННЫЕ RS-D- И УНИВЕРСАЛЬНЫЕ JK-ТРИГГЕРЫ

1 Шадинова К.С. 1 Жусипбекова Ш.Е. 1 Жакипова Ш.А. 1 Мажибаева Г.П. 2 Маметжанова Н.Х. 2 Рсалина Л.А. 2 Байшыгашова Э.А. 2 Суранчиева З.Т. 2 Шаденова Н.С. 31 Казахский национальный медицинский университет имени С.Д. Асфендиярова

2 Казахский государственный женский педагогический университет

3 Общая средняя школа имени С. Аширова

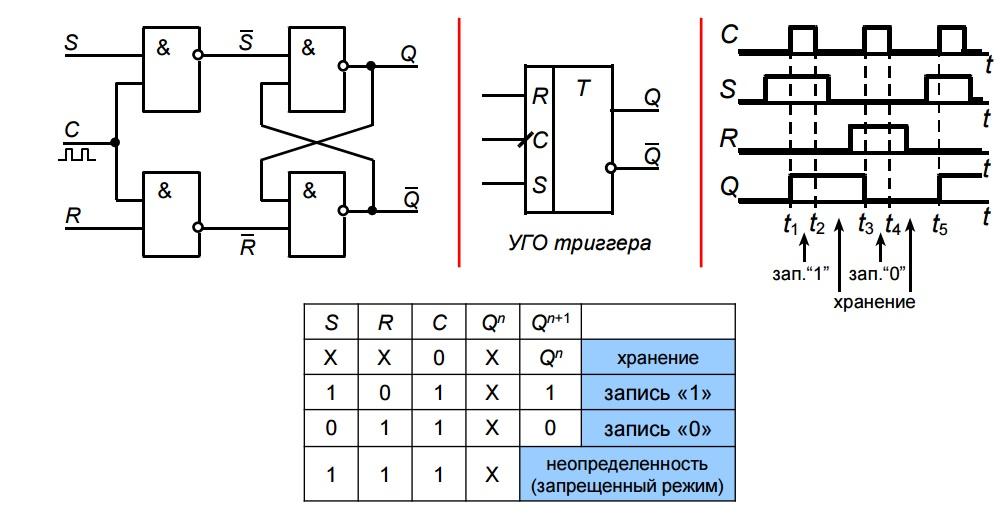

Асинхронные триггеры изменяют свое состояние непосредственно в момент появления соответствующего информационного сигнала и не обладают логическим разнообразием. Синхронизируемые триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на входе синхронизации – С (от англ. clock). Иногда этот вход называют тактирующим или стробирующим. Сигнал на информационном входе этих триггеров записывается и передается на выход по сигналу синхронизации. Еще более широкими возможностями управления обладают тактируемый D- и универсальный JK-триггеры, на которых строятся основные узлы цифровых устройств автоматических комплексов. Поэтому изучение принципа действия, области использования и функциональных возможностей таких триггеров следует считать обязательной необходимой задачей. Цель работы: Исследование принципа построения и работы комбинированного RS-D и универсального JK-триггеров с последующим переводом их в счетный режим.

триггер

логические элементы

1. Горбачев Г.Н., Чаплыгин Е.Е. Промыш-ленная электроника. – М.: Энергоатомиздат. 1988.

2. Прянишников В.А. Электроника. – С.-Пб.: Корона принт. 1998.

3. Эндерлайн Р. Микроэлектроника для всех. – М.: Мир. 1989.

4. Наумов Ю.Е. Интегральные логические схемы. – М.: Радио и связь. 1980.

5. Партала Ю.Е. Цифровая электроника. – С.-Пб.: Наука и техника. 2000.

D-триггер (от англ. delay) отличается от синхронного RS-триггера тем, что вместо двух информационных входов R и S у него имеется только один информационный вход D (рис. 1, а). Часто его называют триггером задержки. Предположим, что первоначально триггер находится в нулевом состоянии, т.е. Q = 0. Если на вход D подать логическую «1», а на вход С подать тактирующий импульс, то на выходе Q установится логическая «1», т.е. триггер примет единичное состояние (Q = 1). Если на вход D подать логический «0», а на вход С – следующий импульс, то триггер перейдет в нулевое состояние (Q = 0). Поступление новых синхроимпульсов на вход С без смены сигнала на информационном входе, не может изменить состояние триггера (рис. 1, б).

Каждый раз смена состояния триггера совершается только по переднему фронту тактирующего импульса на входе С с небольшой задержкой tз по переднему и заднему фронту.

Асинхронные и входы имеют приоритет перед информационным, поскольку элемент памяти в этом случае управляется Лог.

Рис. 1. Комбинированный RS – D триггер (а) и его временные диаграммы (б)

«0» (Q = 1) и уже его ничто не может изменить (табл. 1). Чтобы иметь возможность записать информацию на входе D, следует подать на входы и логическую «1». Условно-графическое изображение D-триггера представлено на рис. 2. На возможность управления триггером только низким потенциалом по входам S и R указывает знак инверсности.

Если информационный вход D триггера соединить с его инверсным выходом , то у триггера остается только один вход С (без учета R и S). При поступлении серии импульсов на вход С, триггер меняет свое состояние каждый раз по переднему фронту этих сигналов и, поскольку лог. «1» на выходе Q появляется в два раза реже, чем импульсы на входе С, то такой триггер осуществляет деление частоты входных сигналов на два. В этом случае такой триггер называют счетным или Т-триггером. Запрещенным состоянием для D-триггера считается одновременное присутствие на входах R = S = 0, в результате чего на обоих выходах возникает логическая «1» (табл. 1). В настоящей работе изучается D-триггер, построенный на ИМС типа К155ТМ2. Данная микросхема имеет в своем составе два независимых D-триггера, представленные на рис. 3.

Рис. 3. Расположение выводов ИМС К155ТМ2

Таблица 1

Таблица истинности D-триггера

|

ВХОДЫ |

ВЫХОДЫ |

||||

|

S |

R |

D |

C |

Q |

Q |

|

0 |

1 |

* |

* |

1 |

0 |

|

1 |

0 |

* |

* |

0 |

1 |

|

1 1 1 |

1 1 1 |

1 0 1 |

1 0 1 |

0 1 0 |

|

|

0 |

0 |

* |

* |

1 |

1 |

Примечание. Символы в табл. 1 означают кратковременный положительный перепад.

Рис. 2. Графическое изображение RS – D триггера

Наиболее универсальным среди тактируемых является JK-триггер (от англ. Jump и Keep), отличающийся от рассмотренных тем, что появление на обоих информационных входах (J и K) логических нулей приводит к изменению состояния триггера. Такая комбинация сигналов для JK-триггера не является запрещенной. Схемная реализация JK-триггера достаточно сложная. Однако, применяя ИМС, нам необязательно обращаться к внутреннему их устройству и обычно достаточно бывает знакомства с их параметрами и функциями, определяемыми условным изображением (рис. 4).

а) б)

Рис. 4. Универсальный JK – триггер (а) и его временные диаграммы (б). Примечание: 1) символ означает отрицательный перепад напряжения от высокого уровня к низкому. 2) Занесение информации в JK-триггер происходит по отрицательному перепаду напряжения на входе С

Таблица 2

Таблица истинности JK-триггера

|

ВХОДЫ |

ВЫХОДЫ |

|||||

|

S |

R |

J |

K |

C |

Q |

Q |

|

0 0 1 1 0/1 1 1 1 1 |

0 1 0 1 1 1 1 1 1 |

* * * 0 0 0 1 1 1 |

* * * 0 0 1 0 1 1 |

1 1 0 0 1/1 0 1 0 1 |

1 0 1 1 0/0 1 0 1 0 |

|

JK-триггер не имеет запрещенных входных комбинаций. Но в реальных микро-схемах используется комбинация RS-триггера с JK-триггером. Установка такого триггера по RS – и J, С, K – входам производится независимо. При одновременном поступлении сигналов на R-, либо на S-вход и на J, С, K – входы, первые имеют приоритет над вторыми. Реальный JK-триггер, построенный на ИМС К155ТВ1, имеет по три информационных J- и по три К-входов, сгруппированных в элементы «И». Логика 3И на входе означает, что значение сигнала J = 1 будет только в том случае, если J1 = J2 = J3 = 1. Аналогично значения сигнала К = 1 будет только в том случае, если К1 = К2 = К3 = 1. Как правило, из входов {J} используется только один, а остальные два входа остаются неподклю-ченными, что равносильно подаче лог. «1» на них. То же самое справедливо и для входов (К) (рис. 5).

Рис. 5. Универсальный JК-триггер на ИМС К155ТВ1

JК-триггер тоже может работать как триггер со счетным входом. Если на входы J- и К-подать лог «1», то в соответствии с табл. 2 истинности, по отрицательному перепаду входных импульсов JК-триггер будет переходить в состояние, инверсное предыдущему (рис. 6).

Из этой диаграммы видно, что триггер со счетным входом делит на два частоту следования входных синхроимпульсов.

Рис. 6. Временные диаграммы JK-триггера в счетном режиме

Порядок выполнения работы

Задание 1

Изучение D- триггера в статическом режиме.

1.1. Ориентируясь на графическое изображение схемы D–триггера на ИМС К155ТМ2 (рис. 3), начертить схему электрическую принципиальную, предназначенную для исследования комбинированного RS-D-триггера в статическом режиме. Схема должна учитывать:

а) задание информации на S, R и D – входы от тумблеров SA1-SA3;

б) подачу синхроимпульсов на вход С от одной из кнопок SB1-SB4 (контакты К1-К4) блока формирователей сигналов без дребезга;

в) подключение единичного выхода триггера к контакту HL-A1 блока индикации 1;

г) подключение инверсного выхода триггера к контакту HL-B1 блока индикации 1.

1.2. Составить и заполнить таблицу соединений.

1.3. Произвести монтаж схемы по таблице.

1.4. После проверки правильности соединений включить блок питания стенда.

1.5. Составить и заполнить таблицу истинности RS- и D- триггера в виде:

|

ВХОДЫ |

ВЫХОДЫ |

||||

|

S |

R |

D |

C |

Q |

|

Необходимо помнить, что входы S- и R- имеют приоритет перед входами D- и C-.

1.6. Найти неисправность, внесенную в схему преподавателем.

1.7. Выключить блок питания, демонтировать схему.

Задание 2

Изучение JK – триггера в статическом режиме.

2.1. Начертить схему, предназначенную для исследования комбинированного RS – и JK- триггера на ИМСК155ТВ1.

Схема должна учитывать:

а) задание информации на входы S, R и J, K от тумблеров SA1-SA4;

б) подачу синхроимпульса от одной из кнопок SB1-SB4 (контакты -) блока формирователей сигналов без дребезга;

в) подключение единичного (прямого) выхода Q к контакту HL-А1 блока индикации 1;

г) подключение нулевого (инверсного) выхода Q триггера к контакту HL-B1 блока индикации 1.

2.2. Написать таблицу соединений.

2.3. Смонтировать на стенде схему.

2.4. После проверки правильности соединений преподавателем включить блок питания стенда.

2.5. Составить и заполнить таблицу истинности для исследования комбинированного RS- и JK-триггера:

|

ВХОДЫ |

ВЫХОДЫ |

|||||

|

S |

R |

J |

K |

C |

Q |

|

Необходимо твердо помнить, что входы S и R имеют приоритет перед другими.

2.6. Найти неисправность, внесенную в схему преподавателем.

2.7. Выключить блок питания и демонтировать схему.

Задание 3

Исследование схемы комбинированного RS- и D-триггера в счетном режиме.

3.1. Смонтировать на стенде схему исследования D-триггера в счетном режиме (рис. 7).

3.2. После проверки правильности соединений, включить питание осциллографа и стенда.

3.3. Получить на экране осциллографа устойчивые изображения сигналов.

3.4. Убедиться в том, что триггер со счетным входом делить частоту следования входных сигналов на два, переключаясь по положительному перепаду;

3.5. Зарисовать в масштабе осциллограммы и определить параметры входных и выходных сигналов.

3.6. Определить быстродействие триггера путем измерения времени задержки выходного сигнала относительно входного.

3.7. Выключить питание приборов и демонтировать схему, сохранив схему генератора без нарушений.

Задание 4

Исследование комбинированного RS-JK-триггера в счетном режиме.

4.1. Начертить схему для исследования универсального RS- JK-триггера на ИМС К155ТВ1 в счетном режиме, аналогичную рис. 7.

Рис. 7. Работа D-триггера в счетном режиме

4.2. Схема должна учитывать:

а) подачу потенциала лог. «1» от контактов блока переключателей SA на входы S, R, J, K;

б) подачу синхроимпульсов от генератора на вход «С» и на вход У1 осциллографа;

в) подключение прямого выхода триггера на вход У2 осциллографа;

4.3. После проверки правильности соединений, включить питание осциллографа и стенда.

4.4. Получить на экране осциллографа устойчивые изображения входных и выходных сигналов.

4.5. Убедиться в том, что триггер делит частоту входных сигналов на два, переключаясь каждый раз по отрицательному перепаду.

4.6. Зарисовать в масштабе осциллограммы входных и выходных сигналов и определить их параметры.

4.7. Определить быстродействие триггера путем измерения задержки выходного сигнала относительно входного.

4.8. Выключить питание приборов и демонтировать схему.

4.9. Привести рабочее место в порядок и закончить работу.

Задание на дом

1. Изучить особенности принципа действия комбинированных RS- D и JK-триггеров.

2. Освоить принцип использования комбинированных триггеров в счетном режиме.

3. Освоить принцип последовательного деления частоты сигналов на 2; на 4 с помощью D- и JK-триггеров.

4. Освоить проверку работы триггеров в статическом и динамическом режимах.

5. Подготовить ответы на контрольные вопросы.

Контрольные вопросы

1. Проследите прохождение сигналов по структурной схеме D-триггера.

2. В каком случае комбинированный RS- и D-триггер переходит в счетный режим?

3. Как составляется таблица истинности D-триггера?

4. Как создаются положительные и отрицательные перепады напряжения для управления триггерами?

5. За счет чего возникает положительный потенциал на других входах JK-триггера при наличии его на одном из информационных (J или K)?

6. Особенности работы JK- триггера в счетном режиме?

Библиографическая ссылка

Шадинова К.С., Жусипбекова Ш.Е., Жакипова Ш.А., Мажибаева Г.П., Маметжанова Н.Х., Рсалина Л.А., Байшыгашова Э.А., Суранчиева З.Т., Шаденова Н.С. КОМБИНИРОВАННЫЕ RS-D- И УНИВЕРСАЛЬНЫЕ JK-ТРИГГЕРЫ // Международный журнал прикладных и фундаментальных исследований. – 2017. – № 5-2. – С. 227-231;URL: https://applied-research.ru/ru/article/view?id=11576 (дата обращения: 12.08.2021).

Предлагаем вашему вниманию журналы, издающиеся в издательстве «Академия Естествознания»

(Высокий импакт-фактор РИНЦ, тематика журналов охватывает все научные направления)

Что такое триггер Шмитта, как он работает и приложения

Что такое триггер Шмитта?

Триггер Шмитта представляет собой схему компаратора (не исключительно), в которой используется положительная обратная связь (небольшие изменения на входе приводят к большим изменениям на выходе в той же фазе) для реализации гистерезиса (модное слово для обозначения замедленного действия) и используется для удаления шума из аналогового сигнала при его преобразовании в цифровой.

ИНВЕРТИРОВАНИЕ И НЕИНВЕРТИРОВАНИЕ ТРИГГЕРОВ SCHMITT С ИСПОЛЬЗОВАНИЕМ LM193 (ОТНОСИТЕЛЬНЫЙ LM393)Он был изобретен еще в 1937 году Отто Х.Шмитта (чье наследие несколько преуменьшено), который назвал это «термоэмиссионным триггером».

Почему триггеры Шмитта?Компараторы по своей природе очень быстрые, так как им не хватает компенсирующего конденсатора, который есть у их собратьев по операционным усилителям. Компараторы не ограничены скоростью нарастания выходного сигнала, а время перехода составляет порядка наносекунд. Компараторы также имеют особенно чувствительные входы из-за их очень высокого усиления — даже незначительные изменения на входе могут вызвать мгновенное изменение состояния на выходе.

Эта проблема усугубляется, когда дифференциальные входные сигналы достигают мертвой зоны, то есть минимального входного дифференциального напряжения, необходимого для поддержания стабильного выходного сигнала. В этом узком диапазоне компаратор не знает, что делать со своим выходом, что приводит к так называемой моторной лодке, то есть к колебаниям выходного сигнала. Эта проблема также возникает с сигналами, которые имеют медленное время перехода — входной сигнал проводит достаточно времени в мертвой зоне (конечно, относительно опорного напряжения) для создания нескольких выходных переходов, как показано на рисунке ниже.

НЕСКОЛЬКО ПЕРЕХОДОВ НА ВЫХОДЕ БЕЗ ГИСТЕРЕЗИСА (СИНИЙ ВХОД, ЖЕЛТЫЙ ВЫХОД)Если вы внимательно заметили, входной сигнал изменяется с размахом выходного сигнала, и на шине питания много шума (как видно на выходе через подтягивающий резистор), что является результатом плохой развязки!

Если бы к выходу была подключена какая-либо логика (что в большинстве случаев верно), она обнаружила бы множественные переходы и вызвала бы хаос — триггеры переключались бы несколько раз, что, возможно, привело бы к сбросу чего-то важного.

Это то, что можно исправить с помощью гистерезиса — в данном случае добавлением единственного резистора между инвертирующим выводом (который в данном случае является опорным) и выходом. Разница заметна снова на рисунке.

ЧИСТЫЙ ПЕРЕХОД С ИСПОЛЬЗОВАНИЕМ HYSTERISISСнова обратите внимание на нестабильное опорное напряжение.

Как работает триггер Шмитта?Триггер Шмитта использует положительную обратную связь — он берет образец выходного сигнала и подает его обратно на вход, чтобы, так сказать, «усилить» выход, что является полной противоположностью отрицательной обратной связи. , который пытается аннулировать любые изменения вывода.

Это усиливающее свойство полезно — оно заставляет компаратор определять состояние выхода, которое он хочет, и заставляет его оставаться там, даже в пределах того, что обычно является мертвой зоной.

Рассмотрим эту простую схему:

ИНВЕРТИРУЮЩИЙ КОМПАРАТОР С ГИСТЕРЕЗИСОМПредположим, что входное напряжение ниже, чем опорное напряжение на неинвертирующем выводе, и поэтому выходное напряжение высокое.

В * — это опорное входное напряжение, которое создает фиксированное смещение на неинвертирующем входе.Поскольку выходной сигнал через подтягивающий резистор высокий, это создает путь тока через резистор обратной связи, немного увеличивая опорное напряжение.

Когда входное напряжение превышает опорное напряжение, выходное напряжение становится низким. Обычно это никоим образом не должно влиять на опорное напряжение, но поскольку есть резистор обратной связи, опорное напряжение падает немного ниже номинального значения, потому что обратная связь и нижний опорный резистор теперь параллельны относительно земли (поскольку низкий выходной сигнал закорачивает этот вывод резистора на массу).Поскольку опорное напряжение понижается, нет шансов, что небольшое изменение входного сигнала вызовет множественные переходы — другими словами, больше нет мертвой зоны.

Чтобы выходной сигнал стал высоким, вход должен теперь пересечь новый нижний порог. После пересечения на выходе устанавливается высокий уровень, и схема «сбрасывается» в исходную конфигурацию. Вход должен пересечь порог только один раз, что приведет к единственному чистому переходу. Схема теперь имеет два эффективных порога или состояния — она бистабильная.

Это можно резюмировать в виде графика:

КРИВАЯ ГИСТЕРЕЗИСАЭто можно понимать в обычном смысле — ось x является входом, а ось y — выходом. Прослеживая линию от x до y, мы обнаруживаем, что после пересечения нижнего порога гистерезис становится высоким, и наоборот.

Работа неинвертирующего компаратора аналогична — выход снова изменяет конфигурацию цепи резисторов, чтобы изменить порог, чтобы предотвратить нежелательные колебания или шум.

Применение триггеров Шмитта Триггеры Шмиттанаходят широкое применение, в основном в качестве логических входов. Опять же, нехорошо иметь единый логический порог, в случае зашумленных или медленных сигналов может произойти несколько переходов на выходе. Читая техническое описание любой логической микросхемы, вы обнаружите, что указаны два порога — один для нарастающего фронта и один для спадающего фронта — это свидетельство входного действия Шмитта.

Иногда логические элементы изображаются с маленьким символом «молнии» внутри них, это стилизованная кривая гистерезиса, указывающая на то, что устройство имеет триггерные входы Шмитта.

1. Простые генераторы

Наличие двух пороговых значений дает триггерам Шмитта 555-подобную способность действовать как предсказуемые осцилляторы.

ПРОСТОЙ ТРИГГЕРНЫЙ ОСЦИЛЛЯТОР SCHMITTПредположим, что конденсатор изначально не заряжен.

Гейт определяет это как низкий уровень входа и устанавливает высокий уровень выхода, поскольку это инвертирующий вентиль. Конденсатор начинает заряжаться через резистор R. Как только достигается верхний порог, затвор переключается на низкий выходной сигнал, разряжая конденсатор до нижнего порога, обеспечивая предсказуемую выходную частоту.

Выражение для частоты может быть получено с помощью небольшого математического жонглирования:

Где R и C — сопротивление и емкость, V T + — верхний порог, V T — нижний порог и V DD — напряжение питания. Обратите внимание на символ «примерно равно».

2. Отключение переключателяМеханические переключатели в качестве логических входов — не самая лучшая идея. Контакты переключателя имеют тенденцию быть несколько пружинящими, вызывая много нежелательного дрожания, которое снова может вызвать множественные переходы и сбои в дальнейшем по линии.

Использование триггера Шмитта с простой RC-цепью может помочь смягчить эти проблемы.

ВЫКЛЮЧАТЕЛЬ SCHMITT TRIGGER DEBOUNCERКогда переключатель нажат, он разряжает конденсатор и на мгновение устанавливает высокий уровень на выходе, пока конденсатор снова не зарядится, создавая чистый импульс на выходе.

Где я могу найти триггеры Шмитта?

Триггеры Шмитта более известны в мире логики как буферы или инверторы, но будьте осторожны, не все вентили являются триггерами Шмитта.Как и вся логика, они доступны в форме DIP или SMD с несколькими воротами в одном корпусе. Хорошим примером является 74HC04, шестнадцатеричный инвертор с триггерными входами Шмитта.

Конечно, и другие логические элементы, такие как 4-элементный логический элемент И 4081, также имеют входы Шмитта.

Заключение Триггеры Шмиттаполезны при использовании зашумленных сигналов — они убирают шум и предотвращают нежелательные множественные переходы и колебания.

Работа с таблицей истинности и объяснение

Термин «цифровой» в электронике означает создание, обработку или сохранение данных в виде двух состояний.Два состояния могут быть представлены как ВЫСОКИЙ или НИЗКИЙ, положительный или неположительный, установленный или сброшенный, что в конечном итоге является двоичным. Высокое значение равно 1, а низкое — 0, поэтому цифровая технология выражается в виде серии нулей и единиц. Например, 011010, в котором каждый термин представляет отдельное состояние. Таким образом, этот процесс фиксации в аппаратном обеспечении выполняется с использованием определенных компонентов, таких как защелка или триггер, мультиплексор, демультиплексор, кодеры, декодеры и т. Д., Которые вместе называются последовательными логическими схемами .

Итак, мы собираемся обсудить триггеры , также называемые защелками . Защелки можно также понимать как бистабильный мультивибратор как два стабильных состояния. Как правило, эти схемы защелок могут быть либо активными с высоким, либо с активными с низким уровнем, и они могут запускаться сигналами HIGH или LOW соответственно.

Общие типы шлепанцев:

- RS Триггер (RESET-SET)

- D Триггер (данные)

- Джек-шлепок (Джек-Килби)

- T Триггер (тумблер)

Из вышеперечисленных типов только триггеры JK и D доступны в форме интегрированной ИС и также широко используются в большинстве приложений.В этой статье мы поговорим о флип-флопе D типа .

D Триггер:

D Триггеры также используются в составе элементов памяти и процессоров данных. D-триггер может быть построен с использованием логического элемента NAND или логического элемента NOR. Благодаря своей универсальности они доступны в виде корпусов IC. Основное применение D-триггера состоит в том, чтобы ввести задержку в схему синхронизации, в качестве буфера, выборки данных через определенные интервалы. D-триггер проще с точки зрения подключения проводов по сравнению с JK-триггером.Здесь мы используем логических элементов NAND для демонстрации D-триггера.

Всякий раз, когда синхросигнал НИЗКИЙ, вход никогда не будет влиять на состояние выхода . Часы должны быть высокими, чтобы входы стали активными. Таким образом, D-триггер представляет собой управляемую бистабильную защелку, в которой тактовый сигнал является управляющим сигналом. Опять же, это делится на D-триггеров, запускаемых положительным фронтом, и D-триггеров, запускаемых отрицательным фронтом . Таким образом, выход имеет два стабильных состояния, основанных на входах, которые обсуждались ниже.

Таблица истинности D-триггера:

Часы | ВХОД | ВЫХОД | |

Д | квартал | Q ’ | |

НИЗКИЙ | х | 0 | 1 |

ВЫСОКИЙ | 0 | 0 | 1 |

ВЫСОКИЙ | 1 | 1 | 0 |

D (данные) — это состояние входа для D-триггера.Q и Q ’представляют собой выходные состояния триггера. Согласно таблице, в зависимости от входов выход меняет свое состояние. Но важно учитывать, что все это может происходить только при наличии тактового сигнала. Это работает точно так же, как триггер SR, только для дополнительных входов.

Представление D-триггера с использованием логических вентилей:

ВХОД | ВЫХОД | |

Вход 1 | Ввод 2 | Выход 3 |

0 | 0 | 1 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

Таким образом, сравнивая таблицу истинности логического элемента И-НЕ и применяя входные данные, указанные в таблице истинности D-триггера, можно проанализировать выходные данные.Анализ вышеуказанной сборки как трехступенчатой конструкции с учетом предыдущего состояния (Q ’) как 0

, когда D = 1 и ЧАСЫ = ВЫСОКИЕ

Выход: Q = 1, Q ’= 0. Работа исправна.

ПРЕДВАРИТЕЛЬНАЯ УСТАНОВКА и ОЧИСТКА:

D-триггер имеет еще два входа, а именно PRESET и CLEAR. Сигнал HIGH на выводе CLEAR приведет к сбросу выхода Q, равному 0. Точно так же сигнал HIGH на контакте PRESET заставит выход Q установить значение 1. Следовательно, само название объясняет описание контактов.

Часы | ВХОД | ВЫХОД | |||

ПРЕДУСТАНОВКА | ОЧИСТИТЬ | Д | квартал | Q ’ | |

Х | ВЫСОКИЙ | НИЗКИЙ | Х | 1 | 0 |

Х | НИЗКИЙ | ВЫСОКИЙ | Х | 0 | 1 |

Х | ВЫСОКИЙ | ВЫСОКИЙ | Х | 1 | 1 |

ВЫСОКИЙ | НИЗКИЙ | НИЗКИЙ | 0 | 0 | 1 |

ВЫСОКИЙ | НИЗКИЙ | НИЗКИЙ | 1 | 1 | 0 |

Корпус микросхемы:

Используемая здесь микросхема — HEF4013BP (двойной триггер D-типа). Это 14-контактный корпус, который содержит 2 отдельных D-триггера. Ниже представлена схема контактов и соответствующее описание контактов.

PIN | PIN Описание |

квартал | Истинный выход |

Q ’ | Выход комплимента |

CP | Тактовый вход |

CD | CLEAR-Прямой ввод |

D | Ввод данных |

SD | PRESET — Прямой ввод |

В SS | Земля |

В DD | Напряжение питания |

Требуемых компонентов:

- IC HEF4013BP (триггер Dual D) — 1

- LM7805 — 1 No.

- Тактильный переключатель — 4

- аккумулятор 9В — 1 шт.

- светодиод (зеленый — 1; красный — 1)

- Резисторы (1 кОм — 4; 220 кОм -2)

- Макет

- Соединительные провода

D Схема триггера и пояснение:

Здесь мы использовали IC HEF4013BP для демонстрации схемы D-триггера, , которая имеет два D-триггера внутри. Источник питания IC HEF4013BP V DD имеет диапазон от 0 до 18 В, и данные доступны в техническом описании.Это показано на снимке ниже. Поскольку на выходе мы использовали светодиод, источник был ограничен до 5 В.

Мы использовали регулятор LM7805 для ограничения напряжения светодиода.

Практическая демонстрация D-триггера:Кнопки D (Данные), PR (Предустановка), CL (Очистить) являются входами для D-триггера. Два светодиода Q и Q ’представляют собой выходные состояния триггера. Батарея 9 В действует как вход для регулятора напряжения LM7805. Следовательно, регулируемый выход 5 В используется в качестве напряжения постоянного тока и вывода на ИС.Таким образом, для разных входов в D соответствующий выход можно увидеть через светодиоды Q и Q ’.

Штыри CLK, CL, D и PR обычно опущены в исходное состояние, как показано ниже . Следовательно, состояние входа по умолчанию будет НИЗКИМ для всех контактов. Таким образом, исходное состояние согласно таблице истинности такое, как показано выше. Q = 1, Q ’= 0.

Ниже мы описали различные состояний триггера типа D с использованием схемы D-триггера, выполненной на макетной плате .

Состояние 1:

Часы — НИЗКИЙ; D — 0; PR — 0; CL — 1; Q — 0; Q ’- 1

Для входов Состояния 1 горит КРАСНЫЙ светодиод, указывающий, что Q ’ВЫСОКИЙ, а ЗЕЛЕНЫЙ светодиод показывает, что Q является НИЗКИМ. Как обсуждалось выше, когда CLEAR установлен на HIGH, Q сбрасывается на 0 , что можно увидеть выше.

Состояние 2:

Часы — НИЗКИЙ; D — 0; ПР — 1; CL — 0; Q — 1; Q ’- 0

Для входов Состояния 2 горит ЗЕЛЕНЫЙ светодиод, указывающий, что Q — ВЫСОКИЙ, а КРАСНЫЙ светодиод показывает, что Q ’НИЗКОЕ.Как обсуждалось выше, когда PRESET установлен на HIGH, Q устанавливается на 1 , что можно увидеть выше.

Состояние 3: Часы — НИЗКИЙ; D — 0; ПР — 1; CL — 1; Q — 1; Q ’- 1

Для входов состояния 3 светятся КРАСНЫЙ и ЗЕЛЕНЫЙ светодиоды, указывая на то, что Q и Q ’изначально находятся в ВЫСОКОМ состоянии. Когда PR и CL опускаются при отпускании кнопок, состояние становится очищенным.

Состояние 4: Часы — ВЫСОКИЙ; D — 0; PR — 0; CL — 0; Q — 0; Q ’- 1

Для входов состояния 4 светится КРАСНЫЙ светодиод, указывая на то, что Q ’ВЫСОКИЙ, а ЗЕЛЕНЫЙ светодиод показывает, что Q на НИЗКОМ. Это состояние стабильно и сохраняется до следующих часов и ввода . Поскольку ЧАСЫ срабатывают по фронту от НИЗКОГО до ВЫСОКОГО, перед нажатием кнопки ЧАСЫ следует нажать кнопку ввода D.

Состояние 5: Часы — ВЫСОКИЙ; D — 1; PR — 0; CL — 0; Q — 1; Q ’- 0

Для входов состояния 5 светится ЗЕЛЕНЫЙ светодиод, указывающий, что Q находится в ВЫСОКОМ состоянии, а КРАСНЫЙ светодиод показывает, что Q ’НИЗКОЕ. Это состояние также стабильно и сохраняется до следующих часов и входа .Поскольку ЧАСЫ срабатывают по фронту от НИЗКОГО до ВЫСОКОГО, перед нажатием кнопки ЧАСЫ следует нажать кнопку ввода D.

Схема запускаШмитта с использованием микросхемы операционного усилителя uA741, конструкция, схема, работа

Схема триггера Шмитта или рекуперативного компаратора

Схема триггера Шмитта также называется схемой рекуперативного компаратора. Схема разработана с положительной обратной связью и, следовательно, будет иметь регенеративное действие, которое будет переключать уровни выхода.Кроме того, использование положительной обратной связи по напряжению вместо отрицательной обратной связи помогает преобразовать напряжение обратной связи входному напряжению, а не противодействовать ему. Использование регенеративной схемы предназначено для устранения трудностей в схеме детектора перехода через нуль из-за низкочастотных сигналов и входных шумовых напряжений.

Ниже представлена принципиальная схема триггера Шмитта. По сути, это схема инвертирующего компаратора с положительной обратной связью. Триггер Шмитта предназначен для преобразования любой входной волны правильной или неправильной формы в прямоугольное выходное напряжение или импульс.Таким образом, ее также можно назвать схемой возведения в квадрат.

Схема триггера Шмитта с использованием микросхемы операционного усилителя uA741Как показано на принципиальной схеме, делитель напряжения с резисторами Rdiv1 и Rdiv2 установлен в положительной обратной связи операционного усилителя 741 IC. Те же значения Rdiv1 и Rdiv2 используются для получения значения сопротивления Rpar = Rdiv1 || Rdiv2, которое последовательно соединено с входным напряжением. Rpar используется для минимизации проблем со смещением. Напряжение на R1 возвращается на неинвертирующий вход. Входное напряжение Vi запускает или изменяет состояние выхода Vout каждый раз, когда его уровни напряжения превышают определенное пороговое значение, называемое верхним пороговым напряжением (Vupt) и нижним пороговым напряжением (Vlpt).