Триггер Шмитта на цифровых логических элементах — Википедия

Материал из Википедии — свободной энциклопедии

Триггер Шмитта на логических элементах «НЕ»

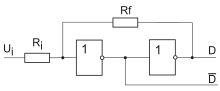

Триггер Шмитта на логических элементах «НЕ»Простейшая реализация триггера Шмитта на двух цифровых логических элементах «НЕ» работающих как два последовательно включённых аналоговых инвертирующих усилителей приведена на рисунке.

Имеет неинвертирующий D{\displaystyle D} и инвертирующий D¯{\displaystyle {\overline {D}}} цифровые выходы.

Триггер работает следующим образом. Вначале пусть выход триггера D находится в состоянии «0», то есть на выходе низкий потенциал относительно «земли», предполагаем, что логика положительна и состоянию «1» соответствует высокий потенциал и напряжение входа вначале нулевое. При повышение входного напряжения его потенциал станет равным порогу переключения логического элемента, который здесь работает как одновходовый компаратор напряжения, при этом выходное напряжение первого по схеме логического элемента начнёт уменьшаться до порога переключения второго по схеме логического элемента. Это вызовет увеличение его выходного напряжения, что по цепи положительной обратной связи вызовет ещё большее увеличение потенциала входа первого логического элемента. В результате в схеме развивается лавинообразный регенеративный процесс завершающийся переходом выхода первого логического элемента в состояние логического «0», в второго — в состояние логической «1». Такое изменение состояния изменит потенциал входа первого элемента — то есть теперь порог переключения станет ниже исходного. Чтобы теперь перевести триггер в состояние логического нуля входное напряжение нужно снизить ниже нижнего порога. Переключение в состояние «0» аналогично описанному.

Для вычисления порогов приведённой схемы предположим, что выходное напряжения элемента «НЕ» в его состоянии логической «1» равно Eo1,{\displaystyle E_{o1},} а в состоянии логического «0» Eo0.{\displaystyle E_{o0}.} Также пусть порог переключения логического элемента по входу равен Es{\displaystyle E_{s}}. Входной ток логического элемента равен 0, что с хорошей точностью выполняется для логических элементов КМОП-серий.

В состоянии выхода логический «0» или «1» потенциал входа Ei{\displaystyle E_{i}} первого логического элемента находится как потенциал, снимаемый со средней точки резистивного делителя Ri, Rf{\displaystyle R_{i},\ R_{f}} в котором Ri{\displaystyle R_{i}} подключен к Ui,{\displaystyle U_{i},} а Rf{\displaystyle R_{f}} — к Eo0{\displaystyle E_{o0}} или к Eo1{\displaystyle E_{o1}} в зависимости от состояния триггера:

- Ei0=Eo0+(Ui−Eo0)RfRi+Rf{\displaystyle E_{i0}=E_{o0}+(U_{i}-E_{o0}){\frac {R_{f}}{R_{i}+R_{f}}}} при состоянии выхода триггера логический «0» и

- Ei1=Eo1+(Ui−Eo1)RfRi+Rf{\displaystyle E_{i1}=E_{o1}+(U_{i}-E_{o1}){\frac {R_{f}}{R_{i}+R_{f}}}} при состоянии выхода триггера логическая «1».

Переключение триггера происходит при равенстве потенциала входа первого логического элемента его порогу переключения Es{\displaystyle E_{s}}, то есть при Ei=Es{\displaystyle E_{i}=E_{s}}. Значения порогов находятся из решения этих уравнений относительно Ui0{\displaystyle U_{i0}} (верхний порог) и Ui1{\displaystyle U_{i1}} (нижний порог):

- Es=Eo0+(Ui0−Eo0)RfRi+Rf,{\displaystyle E_{s}=E_{o0}+(U_{i0}-E_{o0}){\frac {R_{f}}{R_{i}+R_{f}}},}

- Es=Eo1+(Ui1−Eo1)RfRi+Rf.{\displaystyle E_{s}=E_{o1}+(U_{i1}-E_{o1}){\frac {R_{f}}{R_{i}+R_{f}}}.}

Решения этих уравнений относительно Ui0{\displaystyle U_{i0}} и Ui1{\displaystyle U_{i1}}:

- Ui0=Eo0+(Es−Eo0)Ri+RfRf,{\displaystyle U_{i0}=E_{o0}+(E_{s}-E_{o0}){\frac {R_{i}+R_{f}}{R_{f}}},}

- Ui1=Eo1+(Es−Eo1)Ri+RfRf.{\displaystyle U_{i1}=E_{o1}+(E_{s}-E_{o1}){\frac {R_{i}+R_{f}}{R_{f}}}.}

Разность порогов, или ширина петли гистерезиса:

- Ui0−Ui1=(Eo1−Eo0)RiRf.{\displaystyle U_{i0}-U_{i1}=(E_{o1}-E_{o0}){\frac {R_{i}}{R_{f}}}.}

- Пример.

Современные логические элементы КМОП-серий питают обычно от источника +5 В, а порог переключения элементов приблизительно равен половине напряжения питания — около 2,5 В. Для КПОП-логики Eo0≃0 V; Eo1≃5 V{\displaystyle E_{o0}\simeq 0\ V;\ E_{o1}\simeq 5\ V} При равенстве Ri=Rf{\displaystyle {R_{i}}={R_{f}}} верхний порог Ui0≃5 V{\displaystyle U_{i0}\simeq 5\ V} а нижний Ui1≃0 V{\displaystyle U_{i1}\simeq 0\ V}.

Время развития регенеративного процесса при переключении триггера ограничивается в основном временем перезаряда входной ёмкости Ci{\displaystyle C_{i}} первого элемента через резистивный делитель обратной связи и приближённо равно τ=re⋅Ci{\displaystyle \tau =r_{e}\cdot C_{i}}, где re{\displaystyle r_{e}} — импеданс резистивного делителя, re=RiRf/(Ri+Rf){\displaystyle r_{e}=R_{i}R_{f}/(R_{i}+R_{f})}.

Скорость нарастания выходного сигнала или длительность фронта импульса не зависит от скорости нарастания входного сигнала и для данной технической реализации является величиной постоянной и зависит от быстродействия логических вентилей.

Использование цифрового логического элемента в качестве аналогового компаратора ухудшает точность, стабильность и воспроизводимость порогов переключения, так как собственный порог переключения логических элементов подвержен дрейфу от температуры и дрейфу от нестабильности источника питания.

7. Триггер из логических элементов

Триггер из логических элементов

Триггер — простейший автомат* с двумя устойчивыми состояниями — один из основных элементов цифровой техники. В серии микросхем ТТЛ, ТТЛШ, КМОП и другие обязательно входят те или иные его разновидности. Но если в арсенале радиолюбителя таких микросхем нет, триггер можно составить из других элементов. Покажем, как можно построить одну из его разновидностей — так называемый RS -триггер — из элементов, реализующих логические функции.

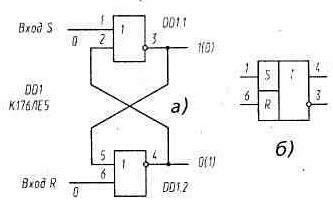

На рис. 101, а изображен RS -триггер, составленный из логических элементов ИЛИ-НЕ. Легко видеть, что в режиме хранения информации — при напряжениях низкого уровня (лог. 0) на входах S и R — он может находиться, в одном из двух состояний: иметь высокий уровень (лог. 1) на выходе элемента DD1.1 и низкий на выходе DD1.2 или, наоборот, низкий на DD1.1 и высокий на DD1.2.

Устанавливают триггер в то или иное состояние обычным образом: подавая на вход S или R напряжение высокого уровня. Это может быть и очень короткий, на пределе физического быстродействия микросхемы, импульс напряжения «единичной» амплитуды. Функции входов-выходов этого триггера, в «триггерном» его изображении, показаны на рис.101, б.

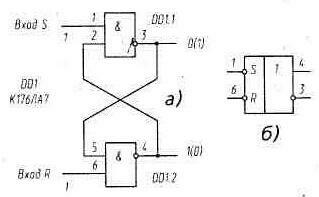

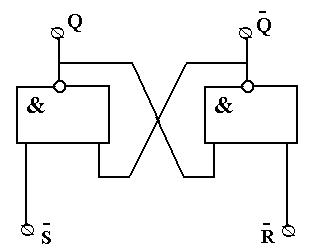

RS-триггер можно составить и из элементов «И-НЕ» (рис. 102, а, б). Здесь режиму хранения информации соответствует напряжение высокого уровня на входах S и R. Напряжение низкого уровня, поданное на вход S, переведет триггер в состояние 1. Оно же, но поданное на вход R, установит триггер в состояние 0.

Рис. 101. Триггер из «ИЛИ-НЕ»

Рис. 102. Триггер из «И-НЕ»

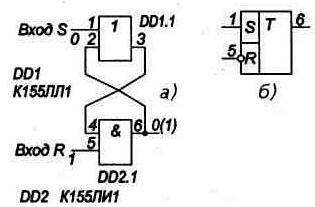

Рис. 103. Триггер из «И» и «ИЛИ»

Оба эти триггера составлены из так называемых шефферовых элементов, каждый из которых сам по себе обладает функциональной полнотой**. Но RS-триггер можно построить и из элементов, не составляющих функционально полной системы.

Такой триггер показан на рис. 103, а, б. Режиму хранения здесь соответствует напряжение низкого уровня на входе S и высокого — на входе R. Триггер устанавливают в состояние 0 подачей на вход R напряжения низкого уровня. Напряжение высокого уровня, поданное на вход S, переведет триггер в состояние 1. Триггеры такой конфигурации замечательны тем, что имеют минимальную сложность в базисе И, ИЛИ, НЕ***.

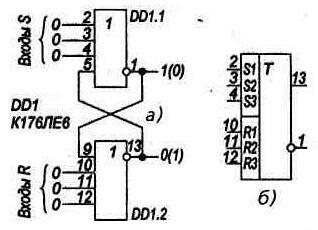

В практическом синтезе может возникнуть необходимость управлять триггером по нескольким, никак не связанным друг с другом S- или R-входам. Такой триггер показан на рис. 104, а, б. Это, очевидно, разновидность триггера, изображенного на рис. 101. Появление «единичного» напряжения на любом из S-входов переводит триггер в состояние 1. Оно же, но приложенное к любому из R-входов, вернет его в состояние 0.

Функционально ту же многоканальность управления триггером можно было бы получить, включив на S- и R-входы триггера по многовходовому дизъюнктору. Но этот вариант бьы бы, очевидно, более громоздким.

Как известно, в триггере комбинацию входных сигналов, инверсную по отношению к режиму хранения, принято запрещать. Для триггера, изображенного на рис. 101, это {S=1, R=1}. Инверсный набор входных сигналов запрещают потому, что при возвращении триггера в режим хранения — при смене {S=1, R=1} на {S=0, R=0} — он может непредсказуемо оказаться как в нулевом, так и в единичном состоянии. Это зависит от того, на каком из входов — S- или R — сигнал 1 задержится чуть дольше. Но если такой неопределенности нет и смещение спадов S- и R-сигналов известно и даже специально организовано, то накладывать безусловный запрет на SR-комбинацию, инверсную по отношению к режиму хранения, нет необходимости.

Заметим в заключение, что триггеры, составленные из логических элементов, не только’позволяют обойтись без специальных, «триггерных» микросхем, но могут существенно упростить трассировку монтажа, так как «синтетический» триггер можно собрать из ближайших по месту на печатной плате свободных логических элементов.

*) К автоматам относят устройства, имеющие собственную память.

**) Функционально полными называют наборы логических элементов, пользуясь которыми можно реализовать любую двоичную функцию. Функционально полный набор может состоять и из одного элемента. Функция, реализуемая таким элементом, называется шефферовой. К универсальным, шефферовым относятся логические элементы, реализующие функции ИЛИ-НЕ и И-НЕ (…ЛЕ… и …ЛА… в микросхемных сериях).

***) Принятое в работах по синтезу схем выражение «в базисе…» означает, что при создании того или иного устройства разработчик имеет право пользоваться лишь элементами, указанными в базисном наборе. Достижение требуемого результата возможно меньшим числом базисных элементов — одна из основных задач конструктора. Построение схемы, реализующей заданную функцию минимально возможным числом базисных элементов, относится к числу труднейших задач математической логики.

D-триггер с работой по уровню (защелка) и по фронту — Help for engineer

D-триггер с работой по уровню (защелка) и по фронту

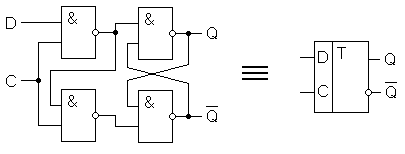

D-триггер получил название от английского слова «delay» — задержка, которая реализуется подачей сигналов на вход синхронизации. В раннее рассмотренном RS-триггере было два входных сигнала, но для передачи двоичного кода достаточно одного входа с разными уровнями напряжения: высокий (1) и низкий (0). На два входа нельзя было подавать единицу одновременно, поэтому в D триггере эти входы объединены с помощью инвертора (рисунок 1 а), что исключает возможность возникновения запрещенного состояния.

Рисунок 1 – а) усовершенствованная схема RS-триггера б) графическое изображение D-триггера

Триггер D может работать по уровню сигнала, он еще называется защелка. В таком устройстве нужно ограничивать длительность синхронизирующего сигнала, потому что пока синхросигнал подается — переходной процесс со входа поступает на выход.

Схема зещелки собранная на логических элементах 2ИЛИ-НЕ (синий провод – логический ноль, красный – единица):

Временная диаграмма работы:

Триггер-защелка включается в работу только по синхросигналу. Когда на С логический ноль, то выход Q хранит прошлое записанное в него состояние, при этом уровень напряжения на входе D никак не может на него повлиять. Если подать «1» на вход синхронизации, то устройство будет работать в режиме «прозрачности» — выходной сигнал мгновенно повторяет сигнал входа. Но при отключении синхросигнала в памяти триггера останется последнее состояние входа и именно оно будет на Q. То есть получается «защелкнутый входной сигнал».

Исходя из описанного принципа работы, составим таблицу истинности:

Х означает, что состояние не имеет значения, иногда обозначают, как «тильда»

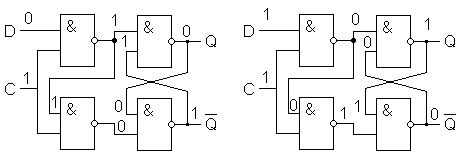

D-триггер, работающий по фронту, не требует контроля длительности синхронизирующего (тактового) сигнала, потому что фронт сигнала С проходит практически мгновенно (не может длиться продолжительное время). Триггер, который будет запоминать информацию лишь по фронту синхросигнала, можно построить из двух D-триггеров, тактовый сигнал на которые будет подаваться в противофазе:

Соответственно, схему на логических элементах можно сконструировать с помощью четырех ИЛИ-НЕ и одного инверсного блока:

На рисунке 2 (анимации) в правом верхнем углу для упрощения восприятия, на первом кадре написана цифра «1». Начиная рассматривать с этого кадра, будет проще проследить принцип работы (синий цвет – «0», красный – «1»).

Временная диаграмма Д-триггера, работающего по фронту

Рассмотрим принцип работы. Q’ – выход первого триггера, Q – второго. Так как тактовый сигнал на первый и второй вход подаются инверсировано, то когда один находится в режиме хранения, другой пропускает информацию со входа на выход. По диаграмме видно, что значение на выходе триггера Q изменится только по спадающему фронту синхронизирующего (тактового) сигнала С. То есть значение на Q будет соответствовать величине напряжения на входе D в момент изменения синхросигнала с 1 на 0.

Так как данное устройство состоит из двух более простых устройств, то условное его обозначение следующее:

Где ТТ означает наличие в строении двух простых триггеров, а «треугольник» около входа С – работу триггера по фронту сигнала.

Недостаточно прав для комментирования

4. Элементы последовательностной логики, триггеры

В цифровых автоматах значение функции зависит не только от значения переменных в данный момент времени (данный такт), но и от их последовательности в предыдущие моменты (такты). Поэтому раздел алгебры логики, описывающий работу цифровых автоматов, обладающих памятью, называется последовательностной логикой. Основным элементом последовательностной логики является триггерный элемент или просто триггер.

Триггером называется устройство, обладающее двумя состояниями устойчивого равновесия и способное под воздействием внешнего управляющего сигнала переходить скачком из одного состояния в другое.

Основные области применения триггера:

запоминающая ячейка в устройствах электронной памяти ЭВМ;

элемент деления на 2 в импульсных счетчиках и делителях частоты;

устройство для расширения (увеличения длительности) импульсов;

устройство, восстанавливающее форму прямоугольного импульса.

Классификация триггеров по способу организации логических связей:

триггеры с раздельным запуском или триггеры с установочными входами – RS-триггеры;

триггеры со счетным входом Т-триггеры;

Триггеры с приемом информации по одному входу – D-триггеры;

Универсальные триггеры – JK-триггеры.

По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация, записанная в триггер, может изменяться в любой момент времени при изменении входных сигналов. В синхронизируемых триггерах информация на выходе может меняться только в определенные моменты времени, задаваемые дополнительным синхронизирующим сигналом.

Как правило, триггер имеет два выхода:

прямой Qи инверсный Состояние триггера определяется по

прямому выходу Q.Число входов зависит от

выполняемых функций:

Состояние триггера определяется по

прямому выходу Q.Число входов зависит от

выполняемых функций:

R – вход установки триггера в нулевое состояние;

Т – счетный вход;

D – вход приема информации;

С – вход синхронизации;

J,K – логические входы;

V – вход разрешения / запрета работы триггера.

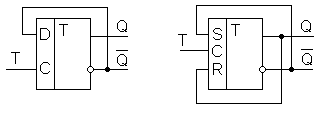

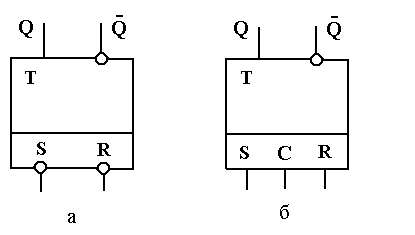

Условные обозначения триггеров приведены на рис.6.

Рис. 6. Условные обозначения триггеров

Рис. 7. Схема асинхронного RS-триггера и его условное обозначение (кружки у входов указывают на инверсные входы – управление сигналом логического 0)

В основе всех схем триггеров лежит основной (базовый) асинхронный RS-триггер.RS-триггер может быть построен на двух логических элементах И-НЕ (рис.7) (или ИЛИ-НЕ).

Элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента.

Триггер имеет два входа: S – вход установки в единичное состояние (от англ. set – установка) и R – вход сброса в нулевое состояние (от англ. reset – сброс). Логика элементов И-НЕ, на которых построен триггер, приведена в табл. 2 и имеет простое словесное выражение: любой ноль на входе дает единицу на выходе. Из этого следует, что управляющими сигналами для этого триггера будут сигналы логического 0.

При подаче нуля на вход S и единицы на вход R (S=0, R=1) на прямом выходе будет уровень логической 1. Эта единица по цепи обратной связи поступает на один из входов нижнего по схеме элемента и вместе с единицей на входе R дает логический 0 на инверсном выходе. Это режим установки триггера в единичное состояние.

При входных сигналах S=1 и R=0 триггер будет установлен в нулевое состояние: на прямом выходе уровень логического 0, на инверсном – 1.

При подаче на оба входа нулевых сигналов на обоих выходах триггера появится уровень логической 1. Это запрещенный режим. Нельзя одновременно подавать сигналы на установку триггера в нулевое и единичное состояние.

В случае, если S=1 и R=1, то триггер не изменяет своего состояния. В этом можно убедиться, предполагая последовательно, что триггер находился в нулевом или единичном состоянии. Полная таблица истинности RS-триггера приведена в табл. 4.

Таблица 4

S | R | | | |

0 | 0 | 0 | 1 | 1 |

0 | 1 | 0 | 1 | 0 |

1 | 0 | 0 | 0 | 1 |

1 | 1 | 0 | 0 | 1 |

0 | 0 | 1 | 1 | 1 |

0 | 1 | 1 | 1 | 0 |

1 | 0 | 1 | 0 | 1 |

1 | 1 | 1 | 1 | 0 |

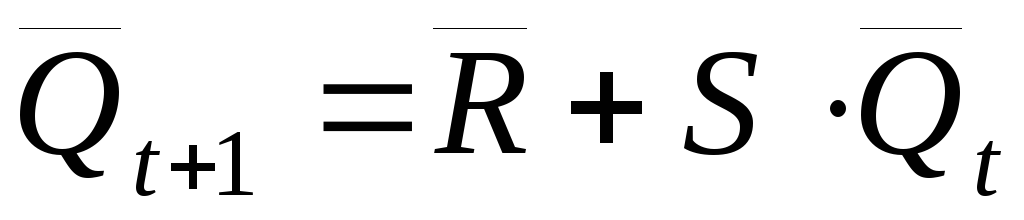

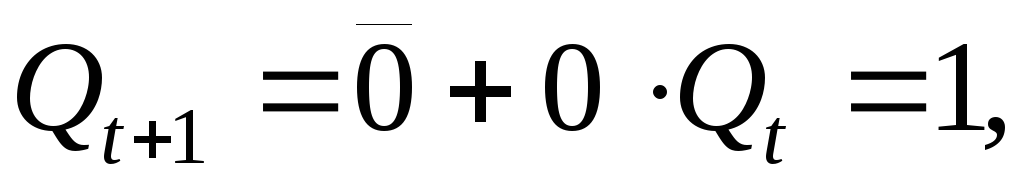

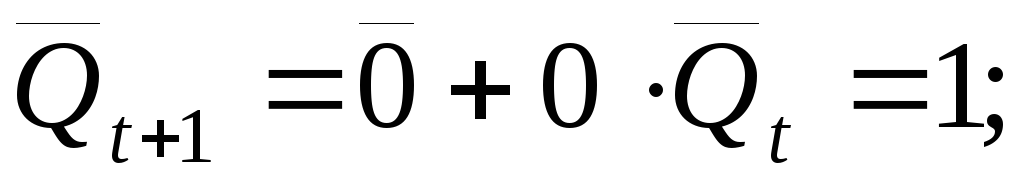

Уравнения описывающие эту таблицу для  и

и  после их упрощения (способы

написания таких уравнений описаны ниже

в разделе «Синтез цифровых схем») имеют

вид:

после их упрощения (способы

написания таких уравнений описаны ниже

в разделе «Синтез цифровых схем») имеют

вид:

и

и .

Здесь

.

Здесь  —

состояние триггера до подачи управляющих

сигналов,

—

состояние триггера до подачи управляющих

сигналов,  —

состояние триггера после подачи

управляющих сигналов.

—

состояние триггера после подачи

управляющих сигналов.

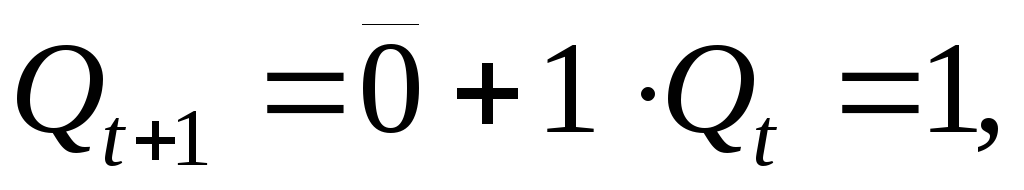

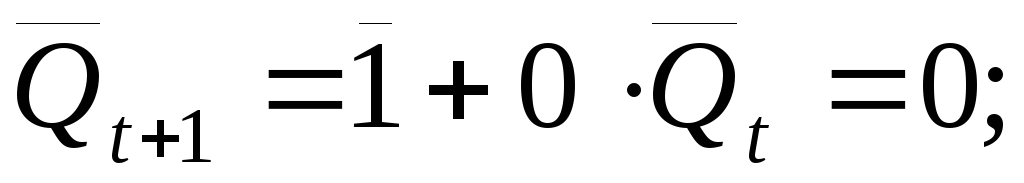

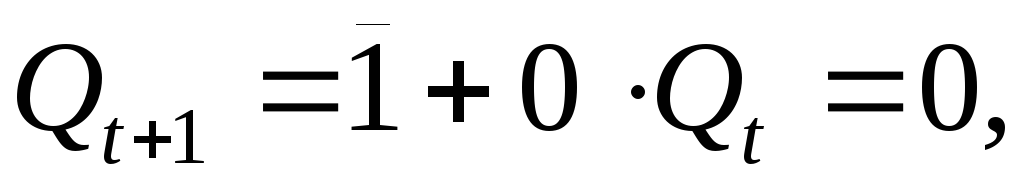

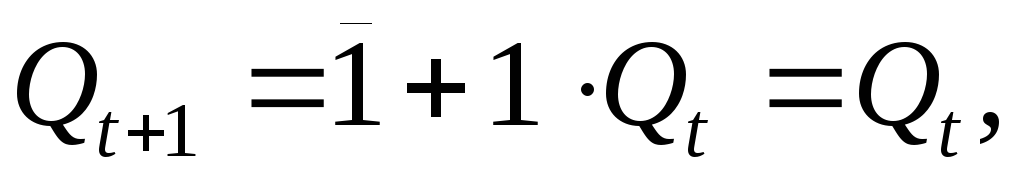

При S=0

и R=0

при S=0

и R=1

при S=1

и R=0

при S=1

и R=0

при S=1

и R=1

при S=1

и R=1

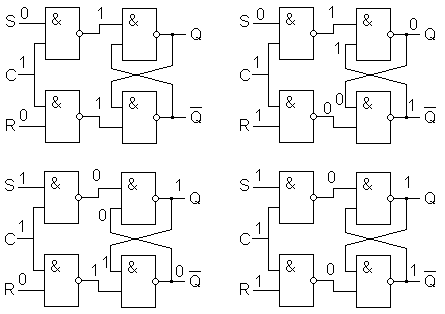

Рис. 8. Схема синхронного RS-триггера на элементах И-НЕ

В синхронном RS-триггере (рис. 8) использованы 4 логических элемента И-НЕ.

Вход С– вход синхронизации. Переключение триггера под действием входных сигналовSиRвозможно только при наличии синхронизирующего импульса, т.е. приС=1. При таком (единичном) сигнале на входеСвходные элементы И-НЕ по другому входу выполняют функцию НЕ, т.е. этот триггер по входамSиRуправляется единичными сигналами. ПриС=0 на выходах входных элементов будут уровни логической 1, что для следующего за входными элементами простогоRS-триггера (см. табл.4) определяет режим хранения, т.е. триггер хранит свое предыдущее состояние и не переключается.

При С=1,S=0 иR=0 на выходах входных элементов уровни логической 1 – триггер находится в режиме хранения (см. рис.9).

При С=1,S=0 иR=1 на прямом выходе появится логический 0, на инверсном – 1. Это режим установки триггера в нулевое состояние.

Рис. 9. Распределение сигналов в синхронном RS-триггере при разных комбинациях сигналов на входахRиS(приС=1)

При С=1,S=1 иR=0 на прямом выходе логическая 1, на инверсном – 0. Это режим установки триггера в единичное состояние.

При С=1,S=1 иR=1 на обоих выходах уровень логической 1 – запрещенный режим. Запрещено одновременно подавать сигналы на установку триггера в единичное и нулевое состояние.

Уравнения для синхронного RS-триггера:

Подставляя в уравнения разные значения С, S, RиQt, получаем результаты, совпадающие с данными, полученными при анализе схемы.

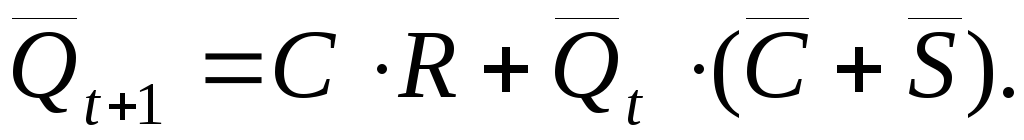

D-триггер (рис.10) имеет в своем составе 4 логических элемента И-НЕ, два из которых образуют простойRS-триггер, а входные подключены к клеммамD(вход приема информации) иС(вход синхронизации). ПриС=0, как и в синхронном триггере, на выходах входных элементов установятся уровни логической 1. Для выходногоRS-триггера это режим хранения.

Рис. 10. Схема D-триггера на логических элементах И-НЕ

Независимо от состояния входа Dна выходе информация не меняется (Qt+1=Qt). ПриС=1 информация со входаDпереписывается на выходQ (Q t+1 = D t). Проследить за состояниями сигналов во всех точках схемыD-триггера приD=0 иD=1 можно по рис. 11.

Рис. 11. Распределение сигналов в D-триггере приD=0 (слева) иD=1 (справа)

В Т-триггере,

при каждом импульсе на входеТ,

триггер переключается в противоположное

состояние.Т-триггер

может быть построен на основеD-триггера

при соединении инверсного выхода со входомD.

ВходСD-триггера

становится входомТТ-триггера.Т-триггер

может быть построен также на основе

синхронногоRS-триггера

соединением входаRс прямым выходомQ,

а входаSс инверсным выходом

со входомD.

ВходСD-триггера

становится входомТТ-триггера.Т-триггер

может быть построен также на основе

синхронногоRS-триггера

соединением входаRс прямым выходомQ,

а входаSс инверсным выходом (рис. 12).

(рис. 12).

Принцип работы Т-триггера иллюстрируется диаграммами напряжений на рис. 13.

Рис. 12. Варианты реализации Т-триггера

Рис. 13. Диаграммы напряжений для Т-триггера, построенного на основе D-триггера (слева) и синхронногоRS-триггера (справа)

Для реализации Т-триггера необходимо использовать не простые (статические)DилиRS-триггеры, описанные выше и срабатывающие по единичному уровню на входеС, а динамические триггеры, срабатывающие по фронту сигнала на входеС. Тогда для схемыТ-триггера на основеD-триггера к моменту прихода первого фронта на входеС, на входеDбыл уровень логической 1. Эта единица и переписывается на выходQсогласно логикеD-триггера. На инверсном выходе появится логический 0. К приходу второго фронта входного сигнала (С) на входеDбыл уровень логического 0. Он и перепишется на выходQ. Эти процессы записи информации со входаDна выходQпоказаны на рис. 13 стрелками. ДляТ— триггера на основе синхронногоRS-триггера процессы аналогичны и основаны на логике синхронногоRS-триггера. К моменту прихода первого фронта сигнала на входС, на входеRбыл уровень логического 0, а на входеS– уровень логической 1. Триггер установится в единичное состояние. При следующем такте (фронте на входеС) входыRиSобменяются состояниями, на выходеQпоявится уровень логического 0.

Таким образом, при каждом входном импульсе Т-триггер переключается в противоположное состояние. Если сравнить периоды входного и выходного сигналов, то можно заметить, что период выходного сигнала в 2 раза больше входного. Т.е.Т-триггер является делителем частоты на 2 и используется в схемах деления частоты и в цифровых счетчиках.

Вопросы для самопроверки

4.1. Опишите логику работы основных типов триггеров.

4.2. Какими символами обозначаются входы триггеров и что эти символы означают?

4.3. Каким будет состояние RS-триггера на элементах И-НЕ приR=0 иS=1? ПриR=1 иS=0?

4.4. Какую роль выполняет вход Св синхронномRS-триггере?

4.5. На все входы синхронного RS-триггера поданы уровни логического нуля. В каком он будет состоянии?

4.6. Начертите схему D-триггера и объясните при каких входных уровнях триггер будет оставаться в режиме хранения информации?

4.7. Какой логический уровень установится на инверсном выходе D-триггера приD=1 иС=1?

4.8. Как получить Т-триггер имея в наличииD-триггер? СинхронныйRS-триггер?

4.9. Напишите уравнение, описывающее работу Т-триггера.

4.10. Возможно ли реализовать триггеры на элементах ИЛИ-НЕ. Объясните это на примере RS-триггера.

Триггеры на логических элементах

Триггер— спусковое устройство с двумя состояниями устойчивого равновесия, которое переходит из одного состояния в другое при воздействии входных сигналов за счет регенеративного процесса.

Регенеративный процесс— это переходный процесс в электрической цепи, охваченной положительной обратной связью с петлевым коэффициентом усиленияK>1в широком диапазоне частот, сопровождающийся резким изменением токов и напряжений цепи.

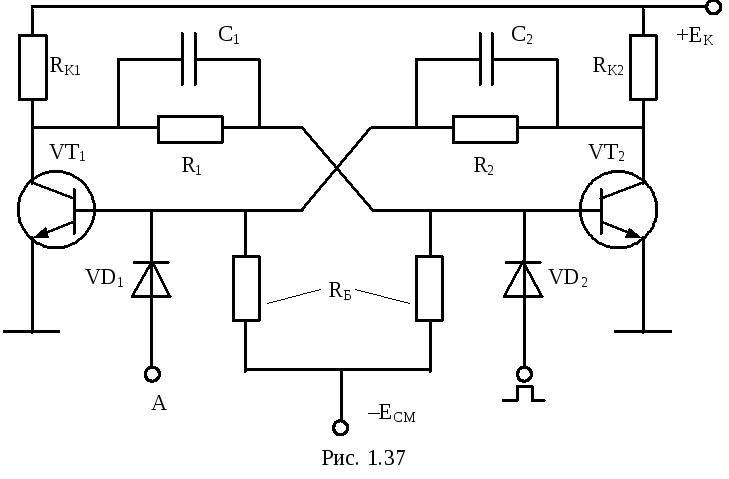

Симметричный триггер на биполярных транзисторах типа n-p-n представлен на рис.1.37.

Через диод VD2на базу транзистораVT2 подадим импульс положительной полярности. ТранзисторVT2начнет открываться, ток коллектораIK2 начнет увеличиваться, напряженияUK2 и UБ1 будут уменьшаться, транзисторVT1выйдет из насыщения и начнет запираться, ток его коллектораIK1 будет уменьшаться, а напряжениеUK1 будет увеличиваться. На базе транзистораVT2 напряжениеUБ2увеличивается, иVT2еще сильнее открывается. Таким образом, в результате действия ПОС транзисторVT1закроется, аVT2откроется, и в этом состоянии триггер будет находиться, пока внешний сигнал не выведет его из этого состояния.

Оба транзистора могут находиться в активной области, но такое состояние является неустойчивым.

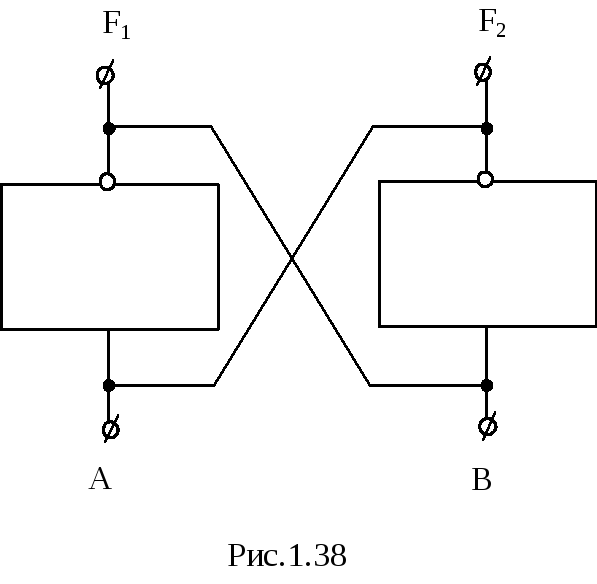

Схему рассмотренного триггера можно изобразить как состоящую из двух инверторов (рис. 1.38).

Если во включенном состоянии один транзистор насыщен, то такой триггер называется насыщенным.

Если во включенном состоянии один транзистор находится на грани насыщения, то такой триггер называется ненасыщенным.

Емкости С1и С2в схеме на рис. выполняют функцию запоминающих элементовони запоминают предыдущее состояние триггера. Другая их функцияускоряющая.

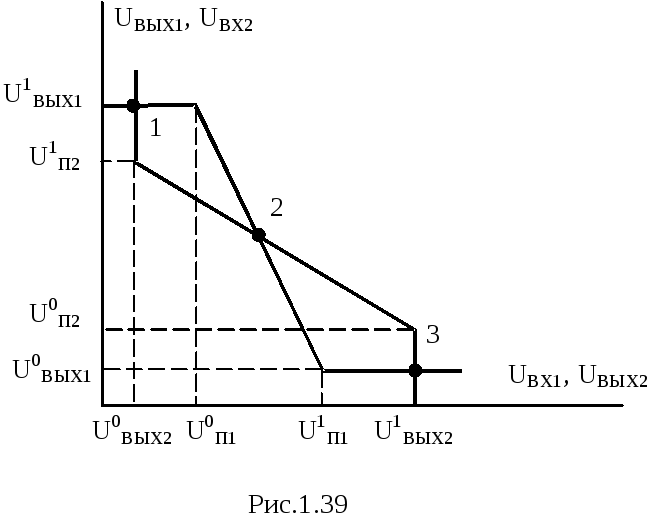

Работу рассмотренной схемы можно исследовать с помощью характеристик переключения (рис. 1.39). В точке 2 могут находиться оба транзистора в активном режиме, но точка 2неустойчивая, тогда как точки 1 и 3устойчивые.

Существует много способов соединения ЛЭ в схему триггеров. Все триггеры на ЛЭ делятся по двум признакам:

По способу записи информации в триггер (способ записи обуславливает временную диаграмму работы триггера):

асинхронные (несинхронизируемые) триггеры,

синхронизируемые (тактируемые) триггеры.

По функциональному назначению:

триггеры с установочными входами (RS-триггеры),

триггеры со счетным входом (Т-триггеры),

триггеры задержки (D-триггеры), или триггеры записи информации по одному входу,

универсальные триггеры, в которых при помощи внешних соединений входных цепей можно получить перечисленные выше триггеры.

Rs-триггеры

RS-триггеры могут выполняться на элементах ИЛИ-НЕ или на элементах И-НЕ.

Рассмотрим триггер, выполненный на элементах ИЛИ-НЕ (рис. 1.40). На схемах такой триггер обозначается как на рис.1.41.

Вход триггера S (set) устанавливает выходQ = 1, а входR (reset) устанавливаетQ = 0.

Ниже представлена таблица переходов RS-триггера.

n | n + 1 | ||

R | S | Q n | Q n +1 |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 1 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 0 | |

1 | 1 | 1 | |

Комбинация

сигналов R = S = 1для данного типа триггеров является

запрещенной, т.к. в этом случае .

Если снять эту комбинацию сигналов,

подав ,например,R = S = 0,

то схема установится в состояние,

определяемое асимметрией триггера.

.

Если снять эту комбинацию сигналов,

подав ,например,R = S = 0,

то схема установится в состояние,

определяемое асимметрией триггера.

Комбинация сигналов R = S = 0не изменяет текущее состояние триггера.

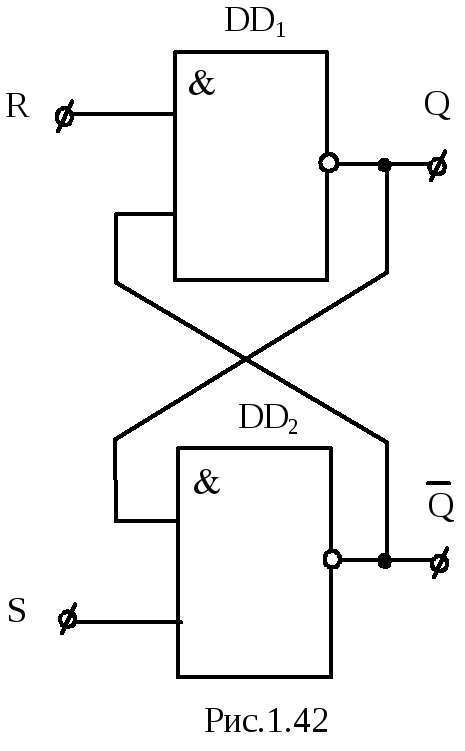

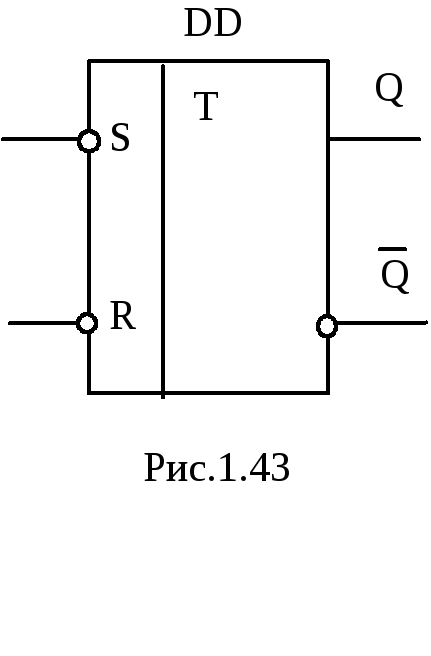

Рассмотрим триггер, выполненный на элементах И-НЕ (рис. 1.42). На схемах такой триггер обозначается как на рис.1.43.

Ниже представлена таблица переходов RS-триггера на элементах И-НЕ.

n | n + 1 | ||

R | S | Q n | Q n +1 |

0 | 0 | 0 | |

0 | 0 | 1 | |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 0 | 1 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 0 |

1 | 1 | 1 | 1 |

Комбинация

сигналов R = S = 0для данного типа триггеров является

запрещенной, т.к. в этом случае .

Если снять эту комбинацию сигналов,

подав ,например,R = S = 1,

то схема установится в состояние,

определяемое асимметрией триггера.

Комбинация сигналовR = S = 1не изменяет текущее состояние триггера.

Триггер на элементах И-НЕтриггер с инверсным управлением.

.

Если снять эту комбинацию сигналов,

подав ,например,R = S = 1,

то схема установится в состояние,

определяемое асимметрией триггера.

Комбинация сигналовR = S = 1не изменяет текущее состояние триггера.

Триггер на элементах И-НЕтриггер с инверсным управлением.

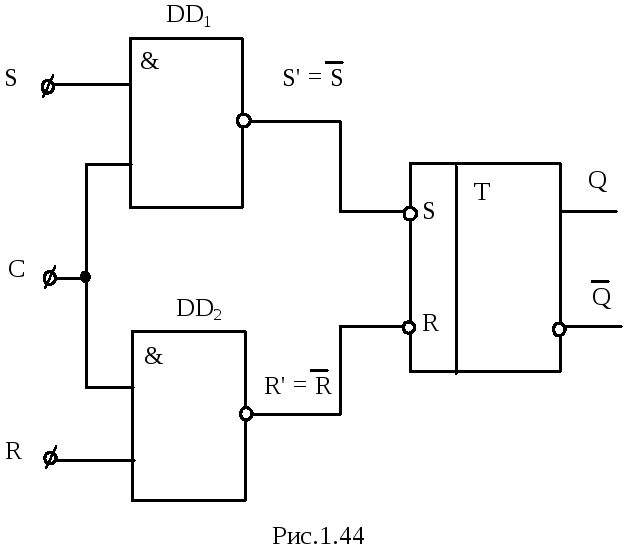

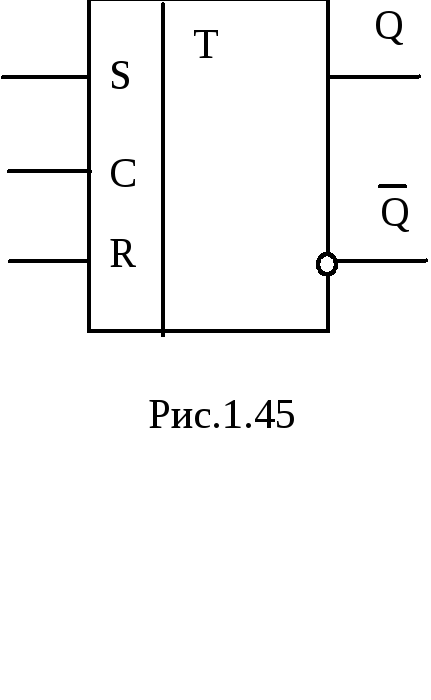

Рассмотренные выше два триггера относятся к асинхронным триггерам. Рассмотрим синхронизируемый RS-триггер(рис.1.44), который изображается на схемах как на рис.1.45.

Вход С синхронизирующий вход. Если С = 0, то, не зависимо от сигналов на входахS иR, на выходах обеих схем совпаденияDD1 иDD2сигналыR’ = S’ = 1, а такая комбинация не меняет состояния триггера. Предположим, чтоQ = 1и действует комбинация сигналовS = 1, R = 0, C = 1. ТогдаR’ = R = 1 и S’ = S = 0, и триггер установится в единицу, т.е.Q = 1. Таким образом, только при наличии синхронизирующего импульса можно изменять состояние триггера.

мир электроники — Триггеры на логических элементах

материалы в категории

Триггер на логических элементах

Собсна гря про триггеры (в том числе и триггеры на транзисторах) уже вкратце было рассказано в отдельной статье, здесь-же немного по-подробнее и о том как сделать триггер из «подручных» базовых элементов.

Итак:

Триггер — это устройство, обладающее двумя состояниями устойчивого равновесия. Триггер еще можно назвать устройством с обратными связями. На рисунке изображена схема триггера на логических элементах ИЛИ-НЕ.

Такая схема называется асинхронным RS-триггером. Первый (сверху) выход называется прямым, второй — инверсным. Если на оба входа (R и S) подать лог. нули, то состояние выходов определить невозможно. Триггер установится как ему заблагорассудится, т. е. в произвольное состояние. Допустим, на выходе Q присутствует лог. 1, тогда на выходе не Q (Q с инверсией) обязательно будет лог. 0. И наоборот. Чтобы установить триггер в нулевое состояние (когда на прямом выходе лог. 0, на инверсном — лог. 1) достаточно на вход R подать напряжение высокого уровня.

Если высокий уровень подать на вход S, то это переведет его в состояние 1, или как говорят, в единичное состояние (на прямом выходе лог. 1, на инверсном — лог. 0). И в том, и в другом случаях напряжение соответствующего уровня может быть очень коротким импульсом — на грани физического быстродействия микросхемы. То есть, триггер обладает двумя устойчивыми состояниями, причем эти состояния зависят от ранее воздействующих сигналов, что позволяет сделать следующий вывод —триггер является простейшим элементом памяти. Буквы R и S по-буржуйски set — установка, reset — сброс (предустановка). На рис. 2 RS-триггер показан в «микросхемном исполнении».

RS-триггер можно соорудить и на элементах И-НЕ, как показано на рисунке 3. Такая конструкция встречается тоже довольно часто:

Принцип работы такой же, как у триггера на элементах ИЛИ-НЕ, за исключением инверсии управляющих сигналов, т. е. установка и сброс триггера производится не лог. 1, а лог. 0. Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными.

Если схему асинхронного триггера немного дополнить, то получим вот такое:

В таком триггере вводится дополнительный вход С, называемый тактовым или синхронизирующим. Изменение состояний триггера происходит при подаче сигналов лог. 1 на входы R и S и последующим воздействием на вход С тактового (синхронизирующего) импульса. Если на тактовый вход импульс не воздействует, то состояние триггера не изменится. Другими словами, изменение состояния триггера происходит под действием синхроимпульса, поэтому такие триггеры называются синхронными.

D-триггер

D-триггер отличается от синхронного RS-триггера тем, что у него только один информационный вход D. D-триггер показан на рисунке:

Если на вход D подать логическую единицу, затем на вход С подать импульс, то на выходе Q (прямой выход) установится лог. 1. Если на вход D подать лог. 0, на С импульс, то на Q установится лог. 0. Т. е. D-триггер осуществляет задержку информации, поступающей на вход D. При чем эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульса триггер переключится, т. е. если на выходе был лог. 0, то станет лог. 1. При следующем импульсе триггер снова переключится, т. е. лог. 1 сменится лог. 0. Таким образом, триггер осуществляет деление частоты входных импульсов на 2 (ведь уровень сигнала на выходе меняется в два раза реже). В таком режиме D-триггер называют счетнымили Т-триггером. Этот режим (режим деления частоты) используется довольно широко.

Нетрудно заметить, что для RS-триггера (рис. 1) существует запрещенная комбинация, когда на оба входа поданы лог. 1, на его выходах также устанавливаются лог. 1 и триггер перестает выполнять свои функции (зависает). Поэтому придумали так называемый JK-триггер. У него три входа — J, K, C. Вход J вместо R, вход К вместо S, С так и остается — синхронизацией. Если на вход J подана лог. 1, на К — лог. 0 или наоборот, то он работает как синхронный RS-триггер, если на оба входа J и К поданы лог. 1, то он работает как счетный Т-триггер.

Триггер Шмитта на логических элементах

Триггер Шмитта — это специфический вид триггера, имеющего один вход и один выход. Такой триггер Еще называют нессиметричным. В триггере Шмитта переход из одного устойчивого состояния в другое осуществляется при определенных уровнях входного напряжения, называемых пороговыми уровнями. Триггер Шмитта изображен ниже.

Если на вход триггера Шмидта подавать нарастающее напряжение (нижний график), то при некотором уровне Uп1 в момент t1 напряжение на выходе скачком переходит из состояния 0 в состояние 1. Если уменьшать напряжение на входе до некоторого напряжения Uп2 в момент t2 напряжение на выходе скачком переходит из состояния 1 в состояние 0. Явление несовпадения уровней Uп1 и Uп2 называется гистерезисом. Соответственно, передаточная характеристика триггера Шмитта обладает гистерезисным характером. Триггер Шмитта, в отличие от других триггеров, не обладает памятью и используется для формирования прямоугольных импульсов из напряжения произвольной формы.

Примечание: основной материал взят с сайта naf-st.ru

Лекция 11 Последовательностные логические элементы, Тригеры

5.3. Последовательностные логические устройства

Из логических элементов составляются схемы, называемые логическими устройствами. Типовые функциональные узлы этих устройств выпускаются в виде отдельных интегральных микросхем. Если на выходе логического устройства информация определяется не только действующей в настоящий момент на входе комбинацией логических переменных, но и всей последовательностью переменных, действующей в предшествующие моменты времени, то такое устройство является последовательностным. Такие устройства частот называют цифровыми автоматами или автоматами с памятью. Очевидно, в последовательностных устройствах должны вводиться элементы, способные запоминать предшествующую информацию. Такую функцию выполняют триггерные элементы.

К числу функциональных узлов последовательностных логических устройств, кроме триггеров, относятся счетчики импульсов и регистры.

7.5. Триггеры

Триггером называется логическое последовательностное устройство, которое имеет два устойчивых состояния. В любом из этих состояний он может пребывать сколь угодно долго, если отсутствует внешнее воздействие. Перевод триггера из одного состояния в другое осуществляется подачей определенного вида входного сигнала. Данные свойства триггера позволяют его использовать в качестве устройства, сохраняющего информацию, представленную в двоичном коде, что определило его широкое применение как элемента памяти в ЭВМ. При этом одно из состояний триггера считается соответствующим логической единице, а другое – логическому нулю.

Триггеры могут создаваться, в частности, при использовании транзисторов и ОУ. В интегральной микросхемотехнике они выполняются в виде интегральных микросхем на основе логических элементов.

Триггеры имеют

два выхода, прямой и инверсный, обозначаемые Q и  ,

по напряжению на которых и определяют

состояние устройства. Состояние триггера

определяется по информации на прямом

выходе: состоянию “1” соответствует Q = 1, при этом

,

по напряжению на которых и определяют

состояние устройства. Состояние триггера

определяется по информации на прямом

выходе: состоянию “1” соответствует Q = 1, при этом  = 0; состоянию

“0”соответствует Q = 0,

= 0; состоянию

“0”соответствует Q = 0,  = 1.

= 1.

По способу управления различают два типа триггеров: асинхронные и синхронные (тактируемые). В асинхронных триггерах переход из одного состояния в другое происходит непосредственно под действием сигналов, поступающих на информационный вход (или входы). В синхронных триггерах, кроме информационных входов, имеется специальный вход для подачи тактового сигнала. Только при его подаче в этих триггерах могут изменяться состояния под воздействием информационного сигнала.

Триггеры также различаются по функциональным свойствам. Наибольшее распространение получили RS, D, Т, JK типы триггеров. Простейшими из них являются RS-триггеры, схемы построения которых будут рассмотрены подробно. Эти триггеры имеют два информационных входа. По одному из них S осуществляется установка определенного состояния (set), по другому R – возвращение в исходное состояние (reset). Первые буквы английских слов и дали наименование типа триггера.

Рисунок 7.12. Структурная схема асинхронного RS— триггера

на логических элементах «И-НЕ»

На рис. 7.12 приведена

схема асинхронного RS-триггера

на элементах “И-НЕ”. Его возможные

состояния в зависимости от подавляемых

информационных сигналов иллюстрируются

таблицей состояния (табл.7.7). В этой

таблице символ Q соответствует состоянию триггера до

поступления информационных сигналов,

символ Q

соответствует состоянию триггера до

поступления информационных сигналов,

символ Q — состоянию триггера после поступления

сигналов.

— состоянию триггера после поступления

сигналов.

Табл. 7.7 состояний

асинхронного RS-

триггера проверяется при использовании

табл. 7.5 истинности элемента “И-НЕ”, из

которой видно, что при логическом “0”

хотя бы на одном входе этого элемента

на его выходе устанавливается логическая

“1”. Поэтому, если на вход  триггера подан логический “0”, то на

прямом выходе Q устанавливается логическая “1”, которая

по цепи обратной связи передается на

вход другого элемента “И-НЕ” с входом

триггера подан логический “0”, то на

прямом выходе Q устанавливается логическая “1”, которая

по цепи обратной связи передается на

вход другого элемента “И-НЕ” с входом  .

При наличии на входе

.

При наличии на входе  логической “1” (вторая строка табл.

7.7) в соответствии с табл. 7.5 (четвертая

строка) на инверсном выходе триггера

логической “1” (вторая строка табл.

7.7) в соответствии с табл. 7.5 (четвертая

строка) на инверсном выходе триггера  устанавливается логический “0”.

Аналогичным образом проверяется

выполнение и первой строки табл. 7.7.

Легко также убедиться, что при логических

“1” на обоих входах триггера (третья

строка табл. 7.7) он может находиться как

в состоянии “1”, так и в состоянии “0”.

Из этого следует, что при подаче такой

информации состояние триггера не

изменяется. Например, если до подачи

двух логических “1” триггер находился

в состоянии “0”, то и после их подачи

триггер будет в том же состоянии “0”.

устанавливается логический “0”.

Аналогичным образом проверяется

выполнение и первой строки табл. 7.7.

Легко также убедиться, что при логических

“1” на обоих входах триггера (третья

строка табл. 7.7) он может находиться как

в состоянии “1”, так и в состоянии “0”.

Из этого следует, что при подаче такой

информации состояние триггера не

изменяется. Например, если до подачи

двух логических “1” триггер находился

в состоянии “0”, то и после их подачи

триггер будет в том же состоянии “0”.

Асинхронный

RS-триггер

на элементах “И-НЕ” не допускает наличия

логических “0” одновременно на обоих

входах. Действительно, в данном случае

в соответствии с табл. 7.5 на входах

каждого элемента триггера должны

установиться логические “1”, но такое

состояние не совпадает ни с одним из

двух устойчивых состояний, в которых

должен находиться триггер. Запрещение

подачи входной информации  =

=  = 0 в табл. 7.7

отмечено соответствующим знаком.

= 0 в табл. 7.7

отмечено соответствующим знаком.

Рисунок 7.13. Структурная схема синхронного RS— триггера

на логических элементах «И-НЕ»

Схема построения синхронного RS- триггера на элементах “И-НЕ” приведена на рис. 7.13. В ее состав входят четыре логических элемента, причем два элемента на выходе образуют асинхронный RS- триггер. Два элемента “И-НЕ” на входе синхронного триггера обеспечивают сохранение неизменным его состояние в отсутствии логической “1” на синхронном входе “С”. Действительно, при наличии на этом входе логического “0” на выходах обоих входных элементах устанавливаются логические “1”, а в данном случае согласно третьей строке табл. 7.7 состояние асинхронного триггера не изменится. Следовательно, ввод информации в синхронный RS- триггер достигается только при подаче на синхронный вход “С” логической “1”, т.е. тактового импульса. Только в этом случае справедлива табл. 7.8 состояний синхронного RS- триггера на элементах “И-НЕ” со схемой рис. 7.13.

Для подтверждения данных табл. 7.8 следует использовать табл. 7.5 истинности элемента “И-НЕ” и табл. 7.7 состояния асинхронного RS-триггера на этих элементах. Необходимо отметить, что для синхронного RS-триггера на элементах “И-НЕ” не допускается наличие логических “1” одновременно на всех его входах. В данном случае на выходах двух входных элементов, а, следовательно, на входах двух выходных элементов схемы рис. 7.11 устанавливаются логические “0”, что недопустимо для асинхронного RS- триггера (четвертая строка табл. 7.7). В соответствии с третьей строкой табл. 7.7 состояние синхронного RS-триггера не изменяется при одновременной подаче на входы S и R логических “0”.

Рисунок 7.14. Схемное обозначение RS— триггеров

на логических элементах «И-НЕ»:

а – асинхронного, б — синхронного

В отличие от

асинхронного триггера рис. 7.12 подача

на информационный вход S

синхронного RS-

триггера логической “1” (при R

= 0) приводит к установке на прямом

выходе Q

также логической “1”. При S

= 0 и R

= 1 триггер будет находиться в

состоянии “0”. Идентичность информации

на входе S

и на выходе Q

триггера отражено отсутствием

черты над обозначениями входов S

и R

синхронного триггера. В то время, как в

обозначениях входов асинхронного RS-

триггера над символами  и

и  вводится черта. В схемных обозначениях

этих элементов, приведенных на рис.

7.14, также имеются отличия. Входы

асинхронного RS-

триггера на элементах “И-НЕ” имеют

знаки “инверсии”, что отражает факт

противоположной информации на входе

вводится черта. В схемных обозначениях

этих элементов, приведенных на рис.

7.14, также имеются отличия. Входы

асинхронного RS-

триггера на элементах “И-НЕ” имеют

знаки “инверсии”, что отражает факт

противоположной информации на входе  и выходе Q.

Подобные знаки у информационных входов

в схематическом обозначении синхронного

RS-

триггера на элементах “И-НЕ” отсутствуют.

и выходе Q.

Подобные знаки у информационных входов

в схематическом обозначении синхронного

RS-

триггера на элементах “И-НЕ” отсутствуют.

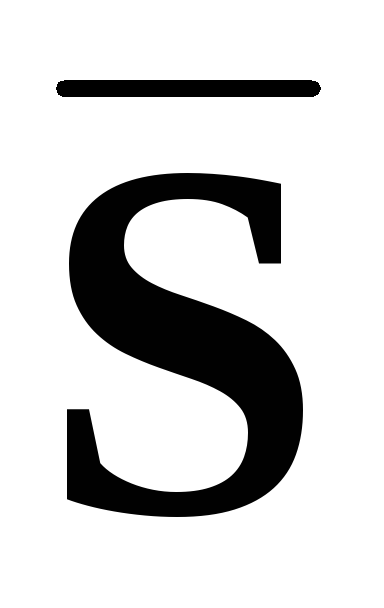

Состояния, в которых могут находиться триггеры, весьма наглядно представляются с помощью временных диаграмм. На рис. 7.15 такие диаграммы приведены для асинхронного и синхронного RS- триггеров со схемами рис. 7.12 и 7.13.

Рисунок 7.15. Временные диаграммы, иллюстрирующие работу RS— триггеров:

а – асинхронного, б — синхронного

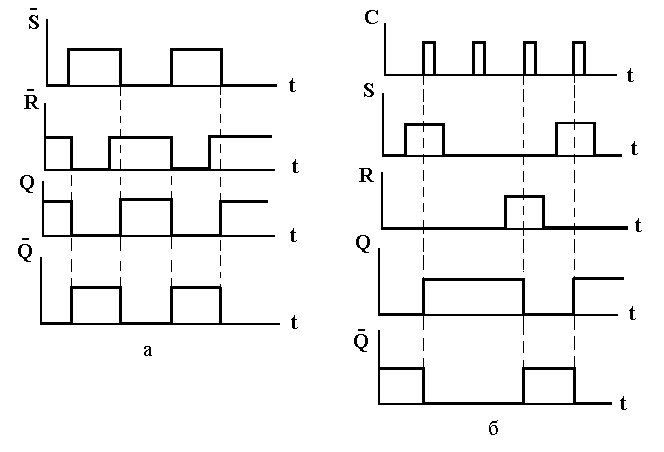

На рис. 7.16 приведены схемные обозначения синхронного D-триггера (а), Т-триггера (б) и синхронного JK-триггера (в), а на рис. 7.17-7.19 – временные диаграммы, иллюстрирующие их работу. Состояние синхронного D-триггера при наличии логической “1” на тактовом входе соответствует информации, поступающей на вход D. Состояние Т-триггера изменяется после каждого изменения информации сигнала на входе Т либо с «1» на «0», либо с «0» на «1». Этот триггер также может иметь специальные, установочные входы, которые, являясь асинхронными, обозначаются как R и S. При подаче “1” на установочный вход R (S = 0) в Т-триггере устанавливается состояние “0”, а при подаче “1” на вход S (R = 0) в триггере устанавливается состояние “1”.

Рисунок 7.16. Схемные обозначения триггеров:

а — синхронного D-триггера, б – Т-триггера, в – JK— триггера

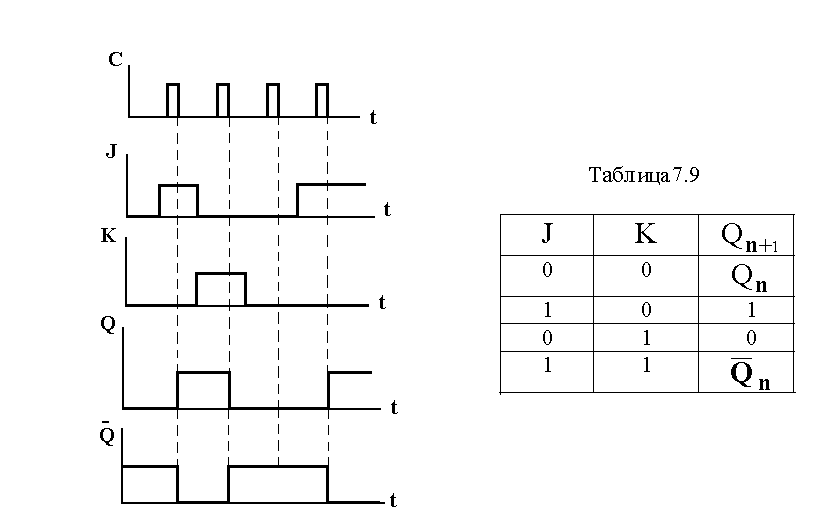

Синхронный JK-триггер имеет два информационных входа J и K, тактовый вход С, а также входы R и S для установки триггера в определенное состояние. В отличие от синхронного D-триггера состояние JK-триггера (см. табл. 7.9) под воздействием информационных сигналов устанавливается после окончания тактового импульса, т.е. при изменении информации на тактовом входе с “1” на “0”. Это иллюстрируется временной диаграммой рис. 7.19. Кроме того, для JK-триггера отсутствуют запрещенные комбинации информационных сигналов, что имеет место в RS-

Рисунок 7.17. Временные Рисунок 7.18. Временные

диаграммы, иллюстрирующие диаграммы, иллюстрирующие

работу синхронного D-триггера работу Т-триггера, в котором,

состояние изменяется после

изменения входного сигнала

с «1» на «0»

Рисунок 7.19. Временные диаграммы,

иллюстрирующие работу JK-триггера

триггерах. Определенное состояние JK-триггера может быть установлено при подаче соответствующих сигналов на установочные входы R и S. Как и в случае Т-триггера, при R = 1 и S = 0 в триггере устанавливается состояние “0”, а при S = 1 , R = 0 – состояние “1”.

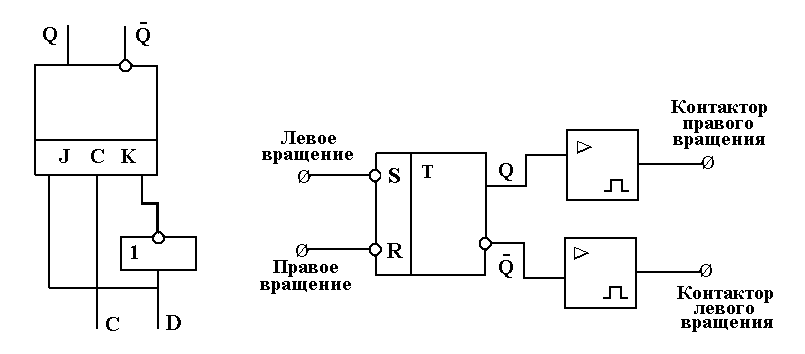

Синхронный JK-триггер является универсальным, на его основе могут быть построены другие типы триггеров. На рис. 7.20 приведена схема с использованием этого триггера, обеспечивающая состояния асинхронного D-триггера.

Рисунок 7.20. Схема на основе Рисунок 7.21 Схема на основе

JK-триггера, реализующая RS— триггера, обеспечивающая защиту

функции синхронного асинхронного двигателя в режиме реверса

D-триггера

Триггеры могут выполнять функции элементов реле, пускателей и других устройств информационной техники. В качестве примера можно рассмотреть применение асинхронного RS- триггера в системе запуска и защиты трехфазного асинхронного двигателя при его работе в режиме реверса, т.е. обеспечения и правого, и левого вращения ротора. Известно, что такой режим достигается переключением двух обмоток статора, для чего в аппаратуре имеются контакторы правого и левого вращения. При изменении направления вращения ротора во избежание короткого замыкания обмоток необходимо исключить одновременное включение двух этих контакторов. Данная задача решается с помощью схемы, приведенной на рис. 7.21. На выходе RS- триггера установлены усилители постоянного тока, которые информационные сигналы низкого напряжения усиливают до уровня, необходимого для приведения в действие контакторов двигателя.

Для включения

двигателя, например, в режим правого

вращения, т.е. для получения информационного

сигнала с выхода Q

триггера сигнал “1” подается на

его вход  ,

а на вход

,

а на вход  — “0”. Для вращения ротора в противоположном

направлении на вход

— “0”. Для вращения ротора в противоположном

направлении на вход  триггера подается “1”, а “0” – на вход

триггера подается “1”, а “0” – на вход  .

Если же одновременно поданы сигналы на

входы

.

Если же одновременно поданы сигналы на

входы  и

и  ,

то согласно табл. 7.7 состояние триггера

не изменится, что исключает одновременную

подачу напряжения на оба контактора, и

ротор двигателя будет вращаться в

прежнем направлении.

,

то согласно табл. 7.7 состояние триггера

не изменится, что исключает одновременную

подачу напряжения на оба контактора, и

ротор двигателя будет вращаться в

прежнем направлении.