Триггеры

1.6. Триггеры

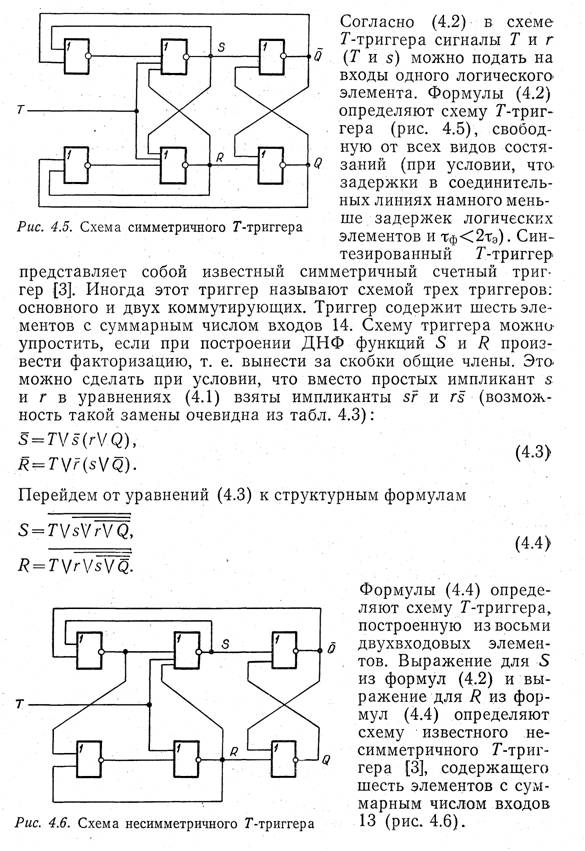

Триггеры имеют два устойчивых состояния. Эти состояния определяются по логическим уровням на выходах триггера. Триггер снабжается двумя выходами: прямым Q и инверсным Q. Состояние триггера определяет логический уровень на выходе Q. Говорят, что триггер находится в состоянии логической единицы, если на выходе Q уровень напряжения, соответствующий логической единице.

Триггеры могут иметь входы различного типа:

R (от англ. RESET) – раздельный вход установки в состояние 0;

S (от англ. SET) – раздельный вход установки в состояние 1;

К – вход установки универсального триггера в состояние 0;

J – вход установки универсального триггера в состояние 1;

V — вход разрешения;

С — синхронизирующий вход;

D — информационный вход;

Т — счетный вход

и некоторые другие.

Обычно название триггера дают по имеющимся у него входам: RS-риггер, JK-триггер, D-триггер и др.

По способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах состояние на выходе изменяется сразу же после изменения сигнала на информационных входах. В синхронных триггерах для передачи сигнала с информационных входов на выходы требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигнала с информационных входов на выходы осуществляется по фронту или по спаду синхронизирующего импульса.

Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы, к которым относятся триггеры, иногда называют последовательными схемами.

Триггеры строились по самым разнообразным электрическим схемам. В

последнее время триггеры обычно конструируют, используя логические элементы.

В

последнее время триггеры обычно конструируют, используя логические элементы.

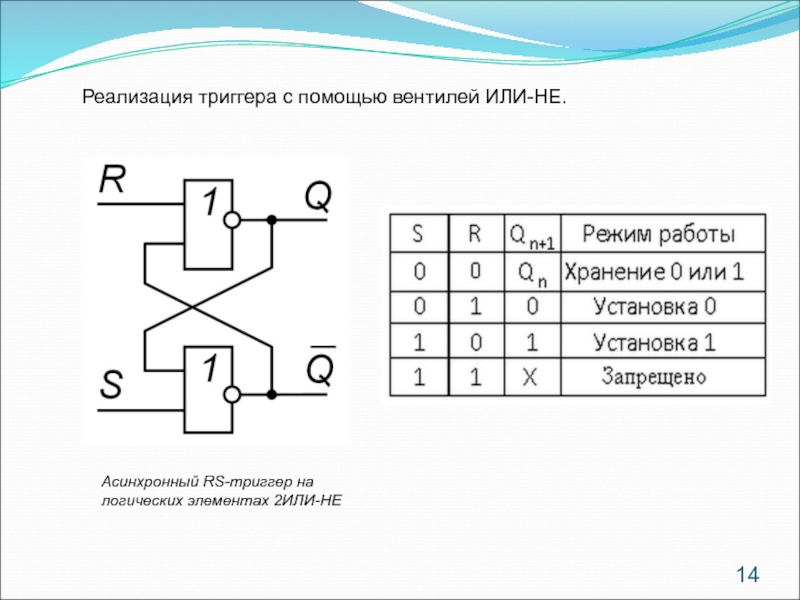

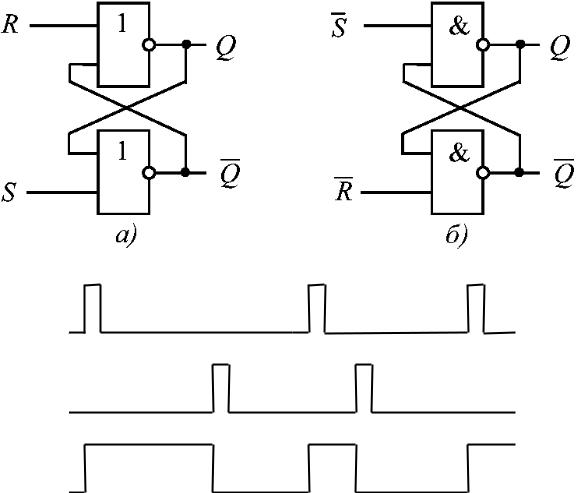

Рассмотрим два варианта RS-триггера: RS-триггер с прямыми входами и RS-триггер с инверсными входами. Установка триггера в нужное состояние осуществляется подачей уровня логической «1» на соответствующий вход для триггера с прямыми входами и подачей сигналов логического «0» для триггера с инверсными входами.

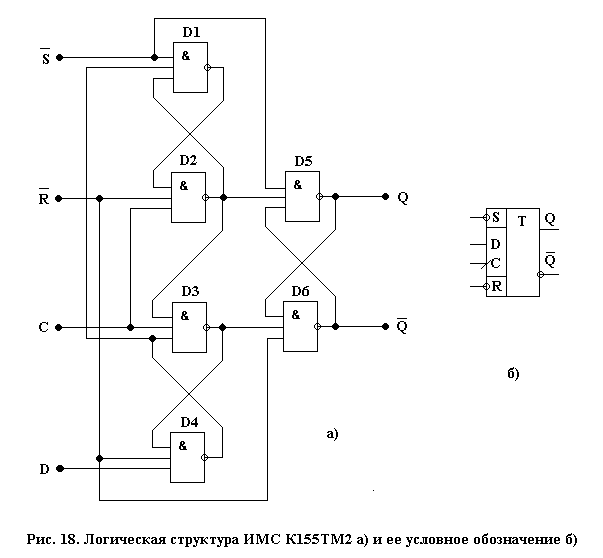

Наибольшее распространение получили RS-триггеры, построенные на логических элементах 2И-НЕ или 2ИЛИ-НЕ. На рисунке 1.36,а приведена функциональная схема RS-триггера с инверсными входами на двух логических элементах 2И-НЕ, а на рисунке 1.36,б – его условное обозначение на принципиальных схемах.

RS- триггер с

прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ.

Триггер получается путем соединения выхода первого логического элемента с одним

из входов второго и соединения выхода второго логического элемента с одним из

входов первого.

Работу RS-триггера можно описать

различными способами: аналитически с помощью формулы; с помощью таблицы, в которой записываются состояния на входах и выходах

триггера в различные моменты времени; с

помощью временных диаграмм.

Рассмотрим временную диаграмму работы RS-триггера с прямыми входами. Для RS-триггера нужно показать 4 графика

(рис. 1.38). Пусть на входах R

и S установлены

пассивные для элементов ИЛИ-НЕ уровни логического нуля (пассивные логические

уровни не могут изменить состояние триггера) и пусть триггер находится в

единичном состоянии, т.е. на выходе Q уровень логической единицы. Подадим на вход R в момент времени t1 уровень логической

единицы. Для анализа работы RS-триггера,

как и любого цифрового устройства, воспользуемся понятием активного логического

уровня. Это существенно облегчает анализ работы схемы. Если на одном входе

логического элемента действует активный логический уровень, то нет

необходимости анализировать логические состояния на других входах элемента.

Т.к. в момент времени t На входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого

элемента уровень логической единицы. Мы видим, что состояние триггера

изменилось с единичного на нулевое. В момент времени t

На входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого

элемента уровень логической единицы. Мы видим, что состояние триггера

изменилось с единичного на нулевое. В момент времени t В момент времениt5 подадим на вход S уровень логической единицы. Проведя аналогичный анализ, увидим,

что состояние триггера не изменилось: на прямом выходе Q – уровень логической единицы, а на

инверсном – уровень логического нуля. В момент времени t6 установим уровень

логической единицы на входе R. В этом случае на выходе Q появится уровень логического нуля, и уровень логического

нуля останется на выходе Q.

В момент времени t

В момент времениt5 подадим на вход S уровень логической единицы. Проведя аналогичный анализ, увидим,

что состояние триггера не изменилось: на прямом выходе Q – уровень логической единицы, а на

инверсном – уровень логического нуля. В момент времени t6 установим уровень

логической единицы на входе R. В этом случае на выходе Q появится уровень логического нуля, и уровень логического

нуля останется на выходе Q.

В момент времени t

Рассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

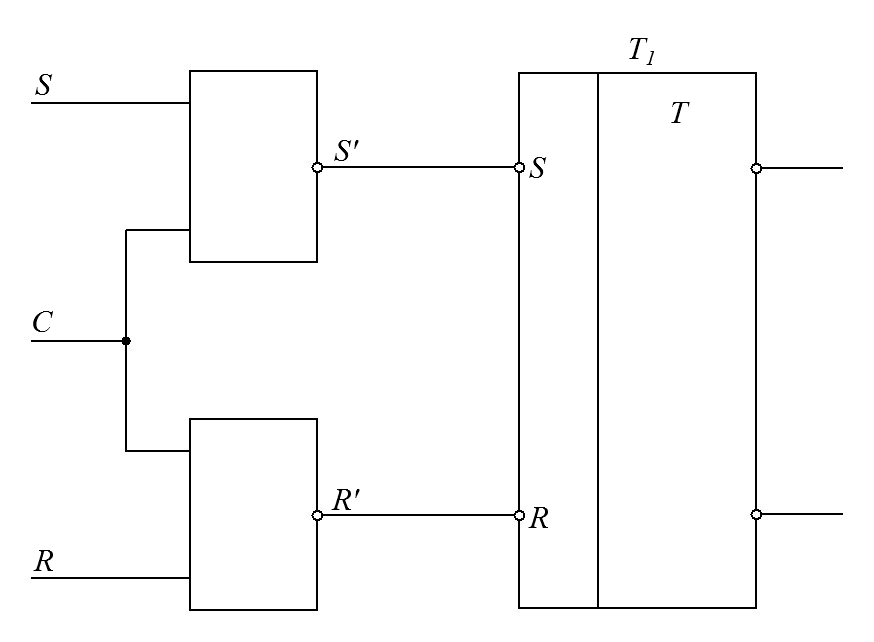

На рисунках 1.39,а,в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 1.39,б.

Рассмотрим функциональную схему синхронного RS-триггера, приведенную на рисунке 1.39а. При С=0 на входах R, S асинхронного триггера на

элементах DD1. 1 и DD1.2 действуют сигналы логического нуля

(логический нуль является пассивным логическим уровнем для логических элементов

2ИЛИ-НЕ), поэтому при любых комбинациях

сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется.

При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше

асинхронный RS-триггер

с прямыми входами. Рассмотренный только что синхронный RS-триггер относится к триггерам со

статическим управлением.

1 и DD1.2 действуют сигналы логического нуля

(логический нуль является пассивным логическим уровнем для логических элементов

2ИЛИ-НЕ), поэтому при любых комбинациях

сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется.

При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше

асинхронный RS-триггер

с прямыми входами. Рассмотренный только что синхронный RS-триггер относится к триггерам со

статическим управлением.

На рисунках 1.40,а и 1.41,а приведены функциональные схемы синхронных RS-триггеров с динамическим

управлением, а их условные обозначения на принципиальных схемах соответственно

на рисунках 1.40,б и 1.41,б. Если в обозначении синхронного RS-триггера с динамическим управлением

стрелочка на входе С направлена к триггеру, то передача сигналов с

информационных входов на выходы происходит

по фронту импульса, а если стрелочка направлена от обозначения триггера,

то передача сигнала осуществляется по

спаду импульса.

Рассмотрим синхронный RS-триггер с динамическим управлением, схема которого приведена на рисунке 1.40,а. Проанализировав функциональную схему синхронного RS-триггера с динамическим управлением, убедимся в том, что состояние триггера не меняется как при изменении сигналов на входах S и R при С=0, так и при С=1, если триггер переключился по фронту синхронизирующего импульса. При C=0 на выходах элементов DD2.1, DD2.2 будут сигналы логической единицы, и состояние на выходе триггера изменяться не будет при любых изменениях сигналов на входах R и S.

Установим на инверсном входе S уровень логического нуля, на инверсном входе R уровень логической единицы, и сигнал

на входе С изменим с логического нуля на

логическую единицу. На выходе элемента DD2.1 появится сигнал логического нуля и триггер перейдет в

единичное состояние, или состояние триггера не изменится, если он находился в

единичном состоянии. Оставляя на входе С сигнал логической единицы, перевести

триггер в нулевое состояние не удается. Для перевода триггера в противоположное состояние обязательно необходимо

подать синхронизирующий импульс.

Для перевода триггера в противоположное состояние обязательно необходимо

подать синхронизирующий импульс.

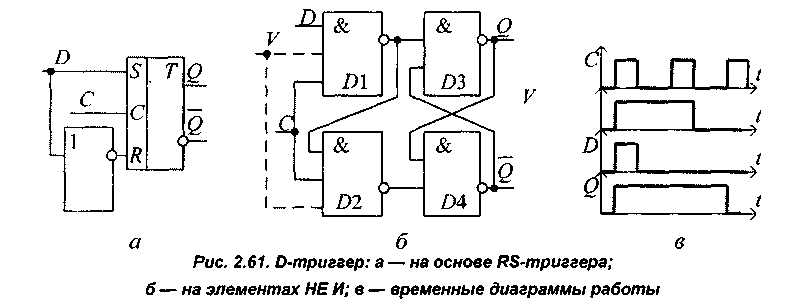

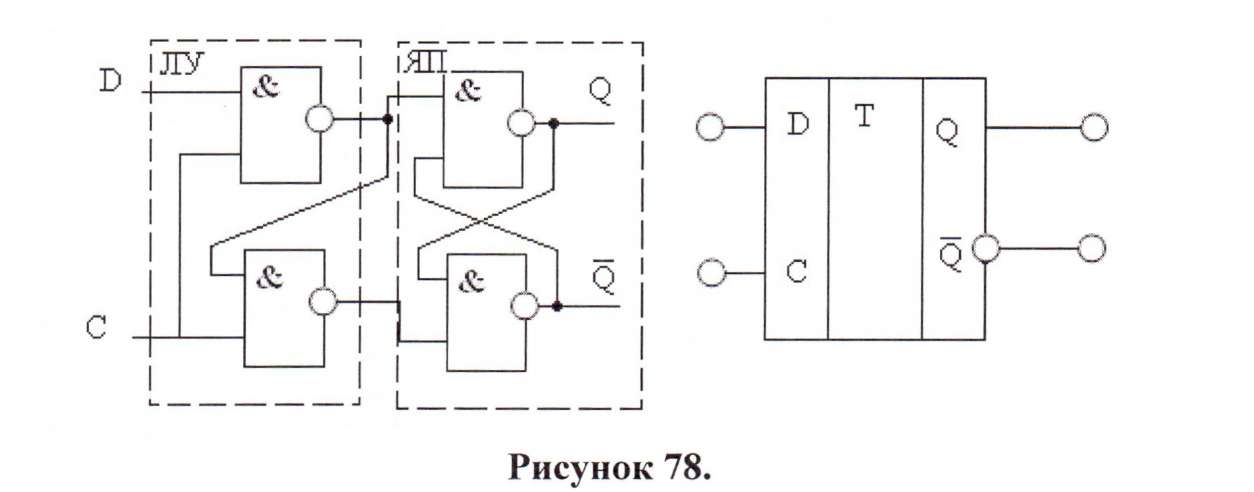

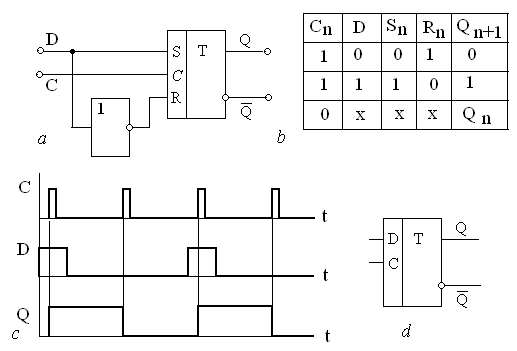

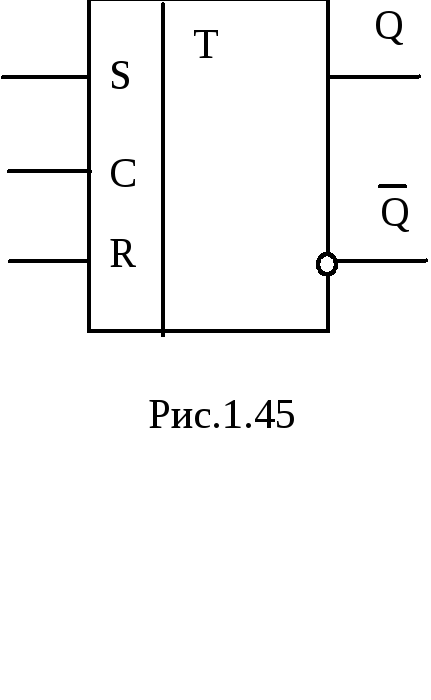

В синхронных RS-триггерах со статическим управлением остается неоднозначность состояния на выходе триггера, если с входов R, S одновременно убирать активные уровни сигналов. Для устранения неоднозначности в схему синхронного RS-триггера добавляют логический элемент «НЕ». Получившийся триггер является D-триггером со статическим управлением. Функциональная схема этого триггера приведена на рисунке 1.42,а, а его условное обозначение на принципиальных схемах – на рисунке 1.42,б.

При С=0 состояние триггера изменяться не будет какой бы ни был сигнал на

входе D, т.к. на

выходах элементов DD2.1,

DD2.2 будут сигналы

логических нулей. При С=1 и D=1

на выходе элемента DD2.1

появится сигнал логического нуля, а на прямом выходе D-триггера – сигнал логической единицы.

При С=1 и D=0 сигнал

логического нуля появится на выходе элемента DD2.2, на инверсном выходе D-триггера установится логическая единица, а на прямом выходе

–логический нуль. Таким образом, D-триггер воспринимает

информацию с входа D и

передает ее на выход Q

при C=1, и затем хранит

ее сколько угодно долго (пока подключен источник питания) при С=0. Т.е. мы

имеем ячейку памяти для хранения 1 бита информации.

Таким образом, D-триггер воспринимает

информацию с входа D и

передает ее на выход Q

при C=1, и затем хранит

ее сколько угодно долго (пока подключен источник питания) при С=0. Т.е. мы

имеем ячейку памяти для хранения 1 бита информации.

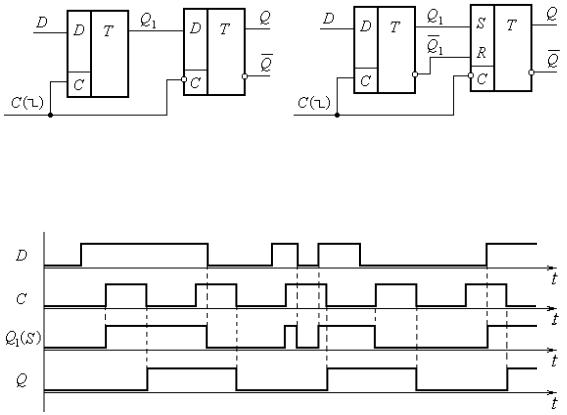

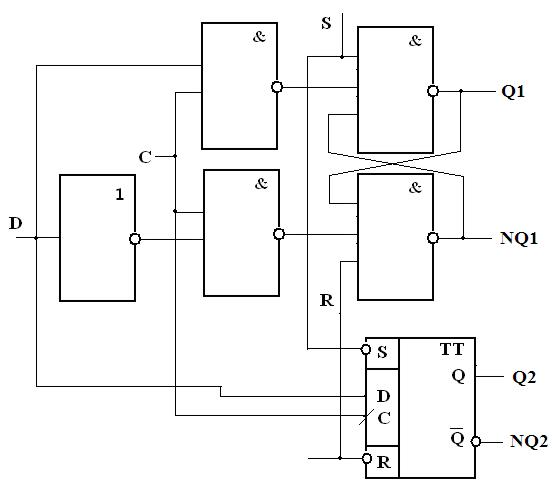

На рисунке 1.43,а приведен еще один вариант схемы D-триггера со статическим управлением. Условное обозначение обоих этих триггеров одинаковое.

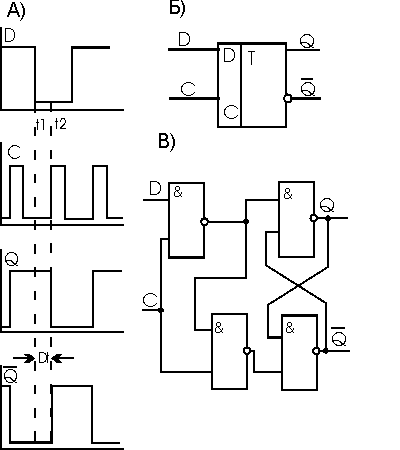

Временная диаграмма работы D-триггера со статическим управлением приведена на рисунке 1.44. Из диаграммы следует, что передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса. Счетный триггер из данного триггера путем соединения инверсного выхода с входом D получить нельзя.

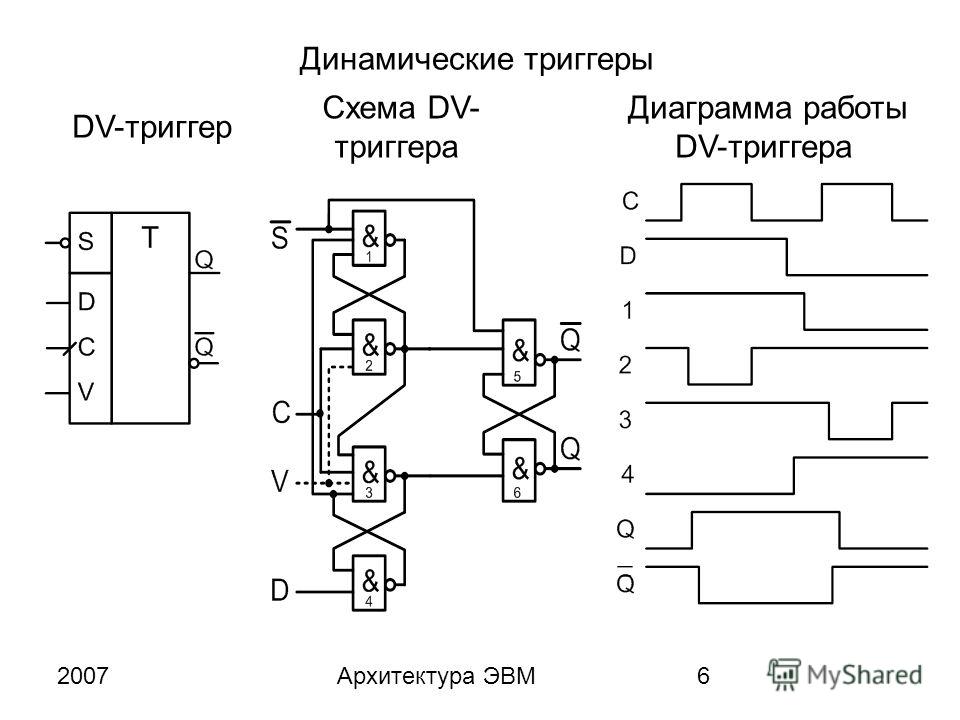

Из D-триггера можно легко получить DV-триггер. Вместо логических элементов 2И-НЕ

используют логические элементы 3И-НЕ и делают дополнительно вход разрешения V. Функциональная схема DV-триггера и его условное обозначение

на принципиальных схемах показаны соответственно на рисунке 1. 45,а-б.

45,а-б.

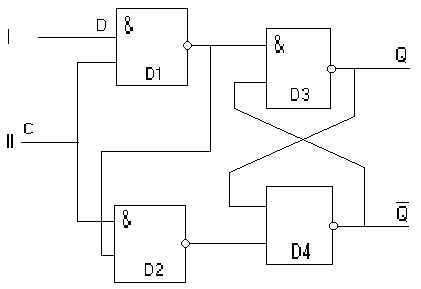

Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. Функциональная схема D-триггера с передачей информации с входа на выход триггера по фронту синхронизирующего импульса приведена на рисунке 1.46,а, а его условное обозначение на принципиальных схемах – на рисунке 1.46,б.

При С=0 на выходах

элементов DD1.3, DD1.4

будут сигналы логических единиц и состояние на выходе триггера не изменится при

любых изменениях сигнала на входе D. Установим на входе D сигнал логической единицы и изменим на входе С сигнал с логического

нуля на единицу. Перед подачей на вход С сигнала логической единицы на выходе

элемента DD1.2

логический нуль, а на верхнем входе элемента

DD1.3

логическая единица. При появлении на входе С логической единицы на выходе элемента DD1.3 установится логический нуль, а на прямом

выходе триггера – логическая единица. Сигнал логического нуля подается с выхода элемента DD1.3

на нижний вход элемент DD1.1 и на верхний вход

элемента DD1.4. Оставляя на входе С логическую единицу, изменим

сигнал на входе D с логической единицы на нуль. На выходе элемента DD1.2

установится логическая единица, а сигналы на выходах элементов DD1.1,

DD1.3 не изменятся, следовательно, не изменится

состояние на выходе триггера.

Сигнал логического нуля подается с выхода элемента DD1.3

на нижний вход элемент DD1.1 и на верхний вход

элемента DD1.4. Оставляя на входе С логическую единицу, изменим

сигнал на входе D с логической единицы на нуль. На выходе элемента DD1.2

установится логическая единица, а сигналы на выходах элементов DD1.1,

DD1.3 не изменятся, следовательно, не изменится

состояние на выходе триггера.

При D=0 изменим сигнал на входе С с логической единицы на нуль. На выходах элементов DD1.3, DD1.4 будут логические единицы, а на прямом выходе триггера останется сигнал логической единицы. Затем изменим сигнал на входе С с логического нуля на логическую единицу. На выходе DD1.4 установится логический нуль, на инверсном выходе триггера логическая единица, а прямом выходе – логический нуль. Из анализа работы данного триггера следует, что в нем передача информации с входа D на выход Q осуществляется по фронту синхронизирующего импульса, подаваемого на вход С.

Триггеры

являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением легко

превратить в счетный триггер. С этой

целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий

вход. Схема такого соединения приведена на рисунке 1.46,в.

D-триггер с динамическим управлением легко

превратить в счетный триггер. С этой

целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий

вход. Схема такого соединения приведена на рисунке 1.46,в.

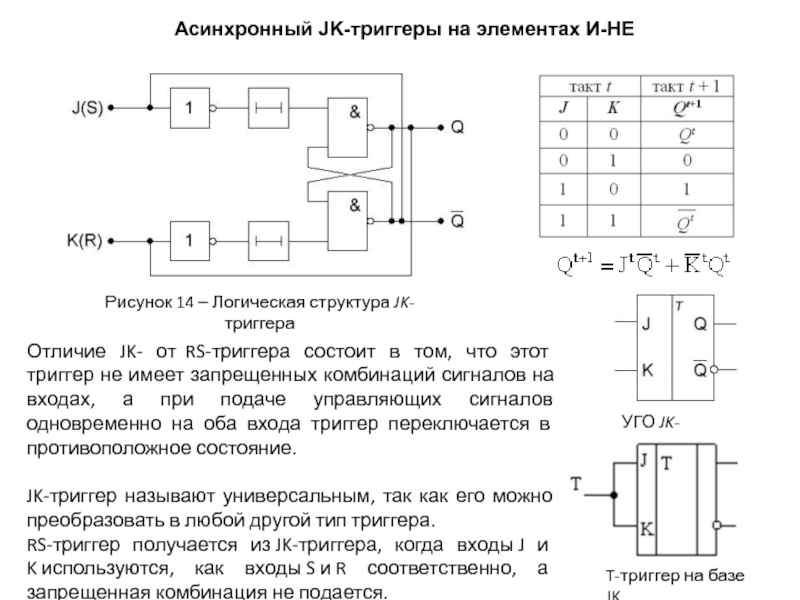

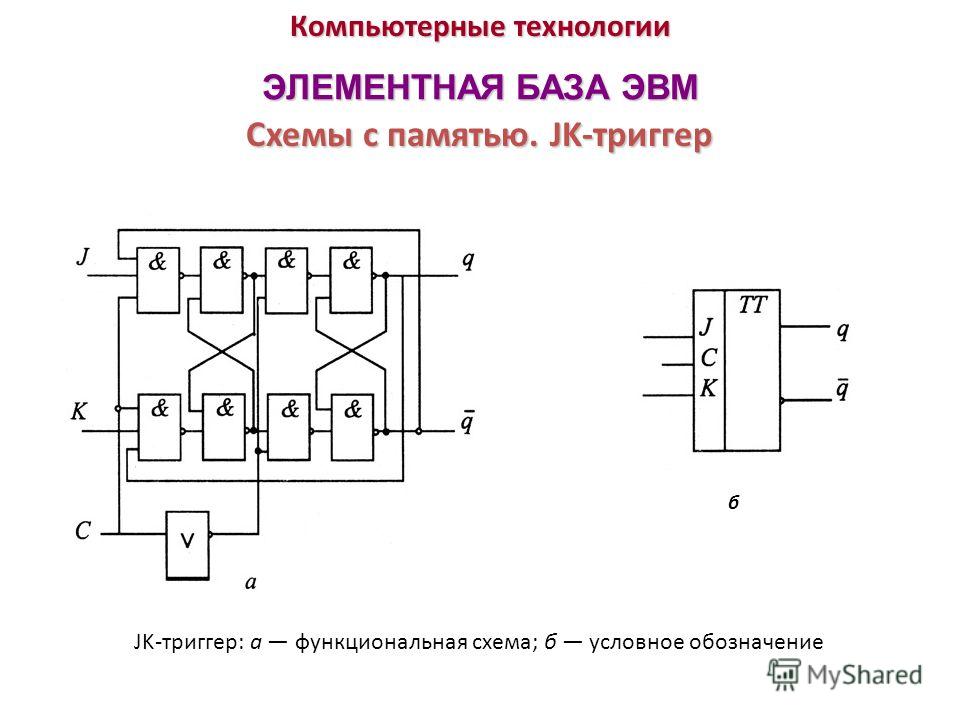

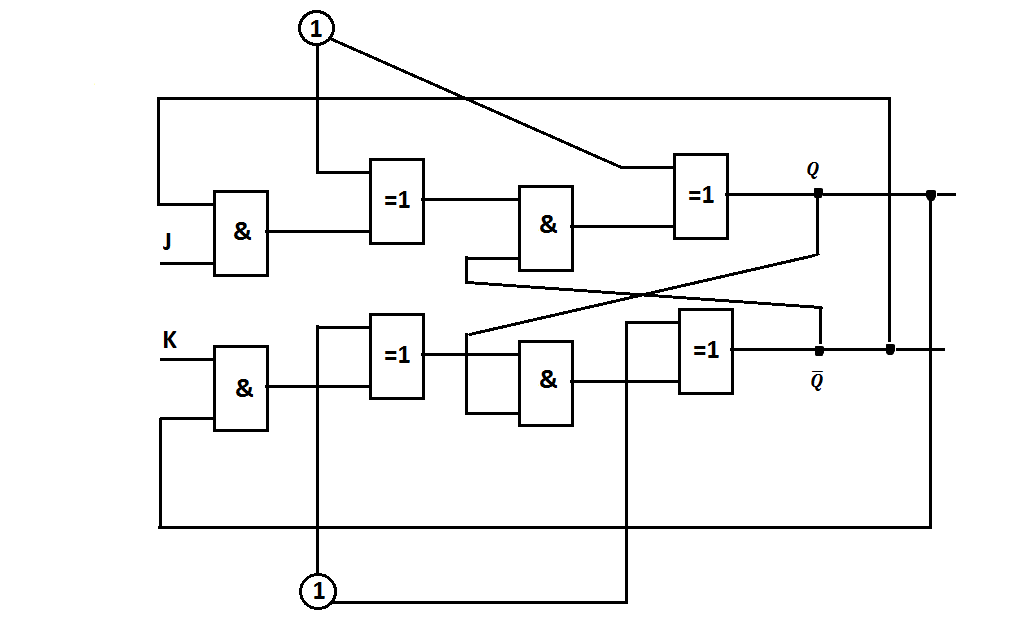

Находят применение двухтактные RS-триггеры (рис. 1.47,а). На рисунке 1.47,б приведена схема счетного триггера, построенного на основе двухтактного RS-триггера. Двухтактный RS-триггер состоит из двух триггеров: главного и вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера. Используя двухтактные RS-триггеры, можно построить JK-триггер. В JK-триггере устранена неопределенность, возникающая в RS-триггере при одновременном снятии активных логических сигналов с входов R и S.

Функциональная схема JK-триггера, построенного с использованием двухтактных (двухступенчатых) RS-триггеров, приведена на рисунке 1. 48,а, а

его условное обозначение на принципиальных схемах – на рисунке 1.48,б.

48,а, а

его условное обозначение на принципиальных схемах – на рисунке 1.48,б.

В условных обозначениях триггеров, построенных с использованием двухтактного синхронного RS-триггера, ставят две буквы Т. Если входы J и K данного триггера соединить вместе и подать на них сигнал логической единицы, а импульсы подавать на вход С, то получим счетный триггер.

Широкое распространение получили JK-триггеры, построенные с использованием синхронных RS-триггеров с динамическим управлением. На рисунке 1.49,а приведена функциональная схема JK-триггера, переключающегося по спаду синхронизирующего импульса, а условное обозначение этого триггера на принципиальных схемах приведено на рисунке 1.49,б. Элементы DD1.1, DD1.2 образуют асинхронный RS-триггер.

Функциональная схема JK-триггера, переключающегося по фронту

синхронизирующего импульса, показана на рисунке 1.50,а, а условное обозначение

приведено на рисунке 1.50,б. При С=0 на выходах элементов DD2. 1 и DD2.2 логические единицы и состояние RS–триггера DD3 не изменяется. Если на инверсных входах J и K логические единицы, то переключение сигнала на входе С с логического нуля на логическую

единицу не изменит состояние на выходе JK–триггера.

1 и DD2.2 логические единицы и состояние RS–триггера DD3 не изменяется. Если на инверсных входах J и K логические единицы, то переключение сигнала на входе С с логического нуля на логическую

единицу не изменит состояние на выходе JK–триггера.

На рисунке 1.50,в приведена схема использования JK-триггера в качестве счетного. На входы J и K подаются логические нули, а импульсы подаются на вход С. Вход С в данном случае является счетным входом Т. Частота импульсов на выходе данного счетчика в два раза меньше частоты импульсов на входе. Скважность импульсов на выходе счетчика равна двум независимо от скважности импульсов на входе счетчика.

Напомним, что

триггеры относятся к цифровым автоматам. Цифровые автоматы состоят из

комбинационных схем. Триггеры входят в состав счетчиков электрических

импульсов, регистров, запоминающих устройств. Один из универсальных сдвиговых

регистров рассмотрен в главе 2. Перейдем к рассмотрению счетчиков и

запоминающих устройств.

мир электроники — Триггеры на логических элементах

материалы в категории

Триггер на логических элементах

Собсна гря про триггеры (в том числе и триггеры на транзисторах) уже вкратце было рассказано в отдельной статье, здесь-же немного по-подробнее и о том как сделать триггер из «подручных» базовых элементов.

Итак:

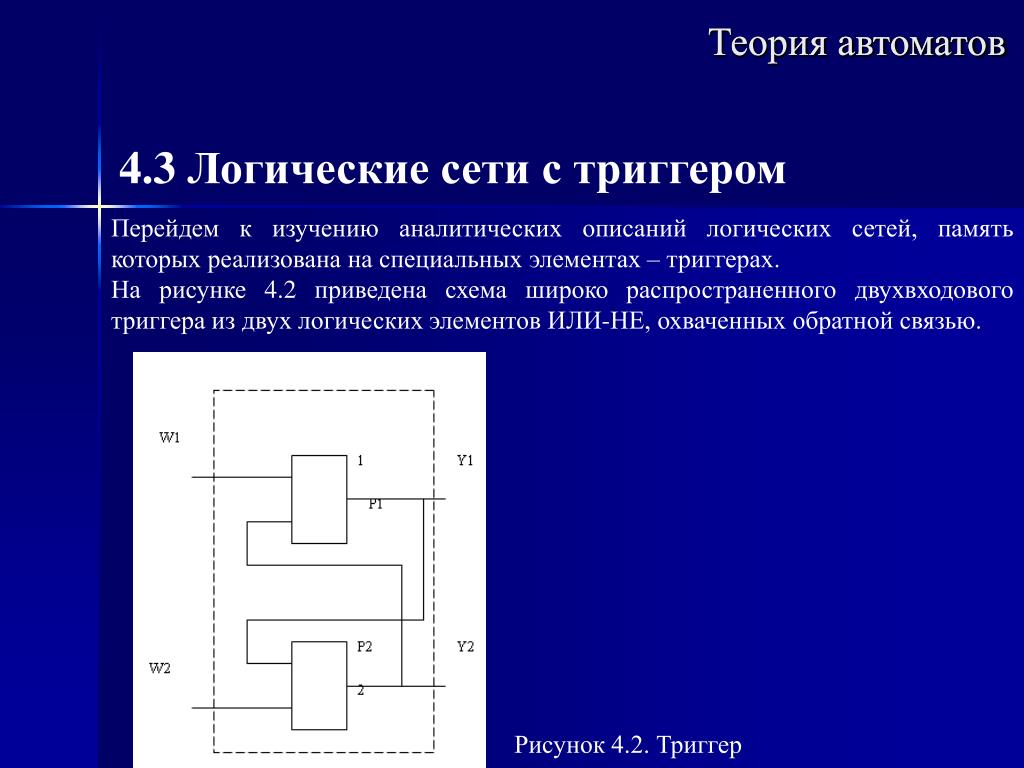

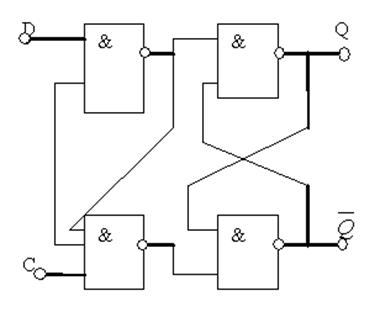

Триггер — это устройство, обладающее двумя состояниями устойчивого равновесия. Триггер еще можно назвать устройством с обратными связями. На рисунке изображена схема триггера на логических элементах ИЛИ-НЕ.

Такая схема называется асинхронным RS-триггером. Первый (сверху) выход называется прямым, второй — инверсным. Если на оба входа (R и S) подать лог. нули, то состояние выходов определить невозможно. Триггер установится как ему заблагорассудится, т. е. в произвольное состояние. Допустим, на выходе Q присутствует лог. 1, тогда на выходе не Q (Q с инверсией) обязательно будет лог. 0. И наоборот. Чтобы установить триггер в нулевое состояние (когда на прямом выходе лог. 0, на инверсном — лог. 1) достаточно на вход R подать напряжение высокого уровня.

0. И наоборот. Чтобы установить триггер в нулевое состояние (когда на прямом выходе лог. 0, на инверсном — лог. 1) достаточно на вход R подать напряжение высокого уровня.

Если высокий уровень подать на вход S, то это переведет его в состояние 1, или как говорят, в единичное состояние (на прямом выходе лог. 1, на инверсном — лог. 0). И в том, и в другом случаях напряжение соответствующего уровня может быть очень коротким импульсом — на грани физического быстродействия микросхемы. То есть, триггер обладает двумя устойчивыми состояниями, причем эти состояния зависят от ранее воздействующих сигналов, что позволяет сделать следующий вывод —триггер является простейшим элементом памяти. Буквы R и S по-буржуйски set — установка, reset — сброс (предустановка). На рис. 2 RS-триггер показан в «микросхемном исполнении».

RS-триггер можно соорудить и на элементах И-НЕ, как показано на рисунке 3. Такая конструкция встречается тоже довольно часто:

Принцип работы такой же, как у триггера на элементах ИЛИ-НЕ, за исключением инверсии управляющих сигналов, т. е. установка и сброс триггера производится не лог. 1, а лог. 0. Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными.

е. установка и сброс триггера производится не лог. 1, а лог. 0. Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными.

Если схему асинхронного триггера немного дополнить, то получим вот такое:

В таком триггере вводится дополнительный вход С, называемый тактовым или синхронизирующим. Изменение состояний триггера происходит при подаче сигналов лог. 1 на входы R и S и последующим воздействием на вход С тактового (синхронизирующего) импульса. Если на тактовый вход импульс не воздействует, то состояние триггера не изменится. Другими словами, изменение состояния триггера происходит под действием синхроимпульса, поэтому такие триггеры называются синхронными.

D-триггер

D-триггер отличается от синхронного RS-триггера тем, что у него только один информационный вход D. D-триггер показан на рисунке:

D-триггер показан на рисунке:

Если на вход D подать логическую единицу, затем на вход С подать импульс, то на выходе Q (прямой выход) установится лог. 1. Если на вход D подать лог. 0, на С импульс, то на Q установится лог. 0. Т. е. D-триггер осуществляет задержку информации, поступающей на вход D. При чем эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульса триггер переключится, т. е. если на выходе был лог. 0, то станет лог. 1. При следующем импульсе триггер снова переключится, т. е. лог. 1 сменится лог. 0. Таким образом, триггер осуществляет деление частоты входных импульсов на 2 (ведь уровень сигнала на выходе меняется в два раза реже). В таком режиме D-триггер называют счетнымили Т-триггером. Этот режим (режим деления частоты) используется довольно широко.

Нетрудно заметить, что для RS-триггера (рис. 1) существует запрещенная комбинация, когда на оба входа поданы лог. 1, на его выходах также устанавливаются лог. 1 и триггер перестает выполнять свои функции (зависает). Поэтому придумали так называемый JK-триггер. У него три входа — J, K, C. Вход J вместо R, вход К вместо S, С так и остается — синхронизацией. Если на вход J подана лог. 1, на К — лог. 0 или наоборот, то он работает как синхронный RS-триггер, если на оба входа J и К поданы лог. 1, то он работает как счетный Т-триггер.

1) существует запрещенная комбинация, когда на оба входа поданы лог. 1, на его выходах также устанавливаются лог. 1 и триггер перестает выполнять свои функции (зависает). Поэтому придумали так называемый JK-триггер. У него три входа — J, K, C. Вход J вместо R, вход К вместо S, С так и остается — синхронизацией. Если на вход J подана лог. 1, на К — лог. 0 или наоборот, то он работает как синхронный RS-триггер, если на оба входа J и К поданы лог. 1, то он работает как счетный Т-триггер.

Триггер Шмитта на логических элементах

Триггер Шмитта — это специфический вид триггера, имеющего один вход и один выход. Такой триггер Еще называют нессиметричным. В триггере Шмитта переход из одного устойчивого состояния в другое осуществляется при определенных уровнях входного напряжения, называемых пороговыми уровнями. Триггер Шмитта изображен ниже.

Если на вход триггера Шмидта подавать нарастающее напряжение (нижний график), то при некотором уровне Uп1 в момент t1 напряжение на выходе скачком переходит из состояния 0 в состояние 1. Если уменьшать напряжение на входе до некоторого напряжения Uп2 в момент t2 напряжение на выходе скачком переходит из состояния 1 в состояние 0. Явление несовпадения уровней Uп1 и Uп2 называется гистерезисом. Соответственно, передаточная характеристика триггера Шмитта обладает гистерезисным характером. Триггер Шмитта, в отличие от других триггеров, не обладает памятью и используется для формирования прямоугольных импульсов из напряжения произвольной формы.

Если уменьшать напряжение на входе до некоторого напряжения Uп2 в момент t2 напряжение на выходе скачком переходит из состояния 1 в состояние 0. Явление несовпадения уровней Uп1 и Uп2 называется гистерезисом. Соответственно, передаточная характеристика триггера Шмитта обладает гистерезисным характером. Триггер Шмитта, в отличие от других триггеров, не обладает памятью и используется для формирования прямоугольных импульсов из напряжения произвольной формы.

Примечание: основной материал взят с сайта naf-st.ru

| Обозначение | Прототип | Функциональное назначение | Тип корпуса | ||

|---|---|---|---|---|---|

| ЭКФ1533ТВ6 | SN74ALS107 | Два J-K-триггера со сбросом | 4306. 14-А 14-А | ||

| КР1533ТВ9 | SN74ALS112 | Двойной J-K-триггер | 2103Ю.16-D | ||

| ЭКФ1533ТВ9 | SN74ALS112 | Двойной J-K-триггер | 4307.16-А | ||

| КР1533ТВ10 | SN74ALS113 | Двойной J-K-триггер с установкой единицы. | 2102Ю.14-В | ||

| ЭКФ1533ТВ10 | SN74ALS113 | Двойной J-K-триггер с установкой единицы | 4306. 14-А 14-А | ||

| КР1533ТВ11 | SN74ALS114 | Двойной J-K-триггер с установкой единицы и общей установкой нуля и синхронизации | 2102Ю.14-В | ||

| ЭКФ1533ТВ11 | SN74ALS114 | Двойной J-K-триггер с установкой единицы и общей установкой нуля и синхронизации | 4306.14-А | ||

| КР1533ТВ15 | SN74ALS109 | Два J-K-триггера | 2103Ю.16-D | ||

| ЭКФ1533ТВ15 | SN74ALS109 | Два J-K-триггера | 4307. 16-А 16-А | ||

| КР1533ТЛ2 | SN74ALS14 | Шесть триггеров Шмитта-инверторов | 2102Ю.14-В | ||

| ЭКФ1533ТЛ2 | SN74ALS14 | Шесть триггеров Шмитта-инверторов | 4306.14-А | ||

| КР1533ТМ2 | SN74ALS74 | Два триггера D-синхронных с дополняющими выходами | 2102Ю.14-В | ||

| ЭКФ1533ТМ2 | SN74ALS74 | Два триггера D-синхронных с дополняющими выходами | 4306. 14-А 14-А | ||

| КР1533ТМ7 | SN74ALS75 | Четыре D-триггера с прямыми и инверсными выходами | 2103Ю.16-D | ||

| ЭКФ1533ТМ7 | SN74ALS75 | Четыре D-триггера с прямыми и инверсными выходами | 4307.16-А | ||

| КР1533ТМ8 | SN74ALS175 | Четыре D-триггера с прямыми и инверсными выходами | 2103Ю.16-D | ||

| ЭКФ1533ТМ8 | SN74ALS175 | Четыре D-триггера с прямыми и инверсными выходами | 4307. 16-А 16-А | ||

| КР1533ТМ9 | SN74ALS174 | Шесть D-триггеров | 2103Ю.16-D | ||

| ЭКФ1533ТМ9 | SN74ALS174 | Шесть D-триггеров | 4307.16-А | ||

| КР1533ТР2 | SN74ALS279 | Четыре триггера R-S | 2103Ю.16-D | ||

| ЭКФ1533ТР2 | SN74ALS279 | Четыре триггера R-S | 4307. 16-А 16-А | ||

| ЭКФ1533ЛЕ11 | SN74ALS33 | Четыре логических элемента “2ИЛИ-НЕ” с открытым коллекторным выходом с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛИ1 | SN74ALS08 | Четыре логических элемента “2И” | 2102Ю.14-В | ||

| ЭКФ1533ЛИ1 | SN74ALS08 | Четыре логических элемента “2И” | 4306.14-А | ||

| КР1533ЛИ2 | SN74ALS09 | Четыре логических элемента “2И” с открытым коллекторным выходом | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛИ2 | SN74ALS09 | Четыре логических элемента “2И” с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛИ3 | SN74ALS11 | Три логических элемента “3И” | 2102Ю.14-В | ||

| ЭКФ1533ЛИ3 | SN74ALS11 | Три логических элемента “3И” | 4306.14-А | ||

| КР1533ЛИ4 | SN74ALS15 | Три логических элемента “3И” с открытым коллекторным выходом | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛИ4 | SN74ALS15 | Три логических элемента “3И” с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛИ6 | SN74ALS21 | Два логических элемента “4И” | 2102Ю.14-В | ||

| ЭКФ1533ЛИ6 | SN74ALS21 | Два логических элемента “4И” | 4306.14-А | ||

| КР1533ЛИ8 | SN74ALS1008 | Четыре логических элемента “2И» с повышенной нагрузочной способностью. | 2102Ю.14-В | ||

| ЭКФ1533ЛИ8 | SN74ALS1008 | Четыре логических элемента “2И» с повышенной нагрузочной способностью. | 4306.14-А | ||

| КР1533ЛИ10 | SN74ALS1011 | Три буфера “3И” | 2102Ю.14-В | ||

| ЭКФ1533ЛИ10 | SN74ALS1011 | Три буфера “3И” | 4306.14-А | ||

| КР1533ЛЛ1 | SN74ALS32 | Четыре логических элемента “2ИЛИ” | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛЛ1 | SN74ALS32 | Четыре логических элемента “2ИЛИ” | 4306.14-А | ||

| КР1533ЛЛ4 | SN74ALS1032 | Четыре логических элемента «2ИЛИ» с повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКФ1533ЛЛ4 | SN74ALS1032 | Четыре логических элемента «2ИЛИ» с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛН1 | SN74ALS04 | Шесть логических элементов “НЕ” | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛН1 | SN74ALS04 | Шесть логических элементов “НЕ” | 4306.14-А | ||

| КР1533ЛН2 | SN74ALS05 | Шесть инверторов с открытым коллекторным выходом | 2102Ю.14-В | ||

| ЭКФ1533ЛН2 | SN74ALS05 | Шесть инверторов с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛН7 | SN74ALS368 | Шесть инверторов с тремя состояниями на выходе | 2103Ю. 16-D 16-D | ||

| ЭКФ1533ЛН7 | SN74ALS368 | Шесть инверторов с тремя состояниями на выходе | 4307.16-А | ||

| КР1533ЛН8 | SN74ALS1004 | Шесть инверторов с повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКФ1533ЛН8 | SN74ALS1004 | Шесть инверторов с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛН10 | SN74ALS1005 | Шесть буферов с открытым коллекторным выходом | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛН10 | SN74ALS1005 | Шесть буферов с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛП3 | Мажоритарный элемент | 2103Ю.16-D | |||

| ЭКФ1533ЛП3 | Мажоритарный элемент | 4307.16-А | |||

| КР1533ЛП5 | SN74ALS86 | Четыре двухвходовых логических элемента “Исключающее ИЛИ” | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛП5 | SN74ALS86 | Четыре двухвходовых логических элемента “Исключающее ИЛИ” | 4306.14-А | ||

| КР1533ЛП8 | SN74ALS125 | Четыре буферных элемента с тремя состояниями на выходе | 2102Ю.14-В | ||

| ЭКФ1533ЛП8 | SN74ALS125 | Четыре буферных элемента с тремя состояниями на выходе | 4306.14-А | ||

| КР1533ЛП12 | SN74ALS136 | Четыре двухвходовых логических элемента “Исключающее ИЛИ” с открытым коллекторным выходом | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛП12 | SN74ALS136 | Четыре двухвходовых логических элемента “Исключающее ИЛИ” с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛП16 | SN74ALS1034 | Шесть логических элементов “2И” с повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКФ1533ЛП16 | SN74ALS1034 | Повторитель с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛП17 | SN74ALS1035 | Шесть логических элементов “2ИЛИ” с открытым коллекторным выходом, с повышенной нагрузочной способностью | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛП17 | SN74ALS1035 | Шесть логических элементов “2ИЛИ” с открытым коллекторным выходом, с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛР4 | SN74ALS55 | Логический элемент “4-4И-2ИЛИ-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛР4 | SN74ALS55 | Логический элемент “4-4И-2ИЛИ-НЕ” | 4306.14-А | ||

| КР1533ЛР11 | SN74ALS51 | Логические элементы “2-2И-2ИЛИ-НЕ” и “3-3И-2ИЛИ-НЕ” | 2102Ю. 14-В 14-В | ||

| ЭКФ1533ЛР11 | SN74ALS51 | Логические элементы “2-2И-2ИЛИ-НЕ” и “3-3И-2ИЛИ-НЕ” | 4306.14-А | ||

| КР1533ЛР13 | SN74ALS54 | Логический элемент “3-2-2-3И-4ИЛИ-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛР13 | SN74ALS54 | Логический элемент “3-2-2-3И-4ИЛИ-НЕ” | 4306.14-А | ||

| КР1533СП1 | SN74ALS85 | Схема сравнения двух четырёхразрядных чисел | 2103Ю.16-D | ||

| ЭКФ1533СП1 | SN74ALS85 | Схема сравнения двух четырёхразрядных чисел | 4307.16-А | ||

| КР1533ТВ6 | SN74ALS107 | Два J-K-триггера со сбросом | 2102Ю.14-В | ||

| КР1533КП11А | SN74ALS257 | Четырeхразрядный селектор 2-1 с тремя устойчивыми состояниями | 2103Ю.16-D | ||

| ЭКФ1533КП11А | SN74ALS257 | Четырeхразрядный селектор 2-1 с тремя устойчивыми состояниями | 4307.16-А | ||

| КР1533КП12 | SN74ALS253 | Двухразрядный четырeхканальный коммутатор с тремя устойчивыми состояниями по выводу | 2103Ю.16-D | ||

| ЭКФ1533КП12 | SN74ALS253 | Двухразрядный четырeхканальный коммутатор с тремя устойчивыми состояниями по выводу | 4307.16-А | ||

| КР1533КП13 | SN74ALS298 | Четыре двухвходовых мультиплексора с запоминанием | 2103Ю.16-D | ||

| ЭКФ1533КП13 | SN74ALS298 | Четыре двухвходовых мультиплексора с запоминанием | 4307.16-А | ||

| КР1533КП14А | SN74ALS258 | Четырeхразрядный селектор 2-1 с тремя устойчивыми состояниями с инверсными выходами | 2103Ю.16-D | ||

| ЭКФ1533КП14А | SN74ALS258 | Четырeхразрядный селектор 2-1 с тремя устойчивыми состояниями с инверсными выходами | 4307.16-А | ||

| КР1533КП15 | SN74ALS251 | Восьмивходовый селектор-мультиплексор с тремя устойчивыми состояниями | 2103Ю.16-D | ||

| ЭКФ1533КП15 | SN74ALS251 | Восьмивходовый селектор-мультиплексор с тремя устойчивыми состояниями | 4307.16-А | ||

| КР1533КП16 | SN74ALS157 | Четырeхразрядный селектор-мультиплексор 2-1 | 2103Ю.16-D | ||

| ЭКФ1533КП16 | SN74ALS157 | Четырeхразрядный селектор-мультиплексор 2-1 | 4307.16-А | ||

| КР1533КП17 | SN74ALS353 | Сдвоенный инверсный селектор-мультиплексор 4х1 с тремя состояниями на выходе | 2103Ю.16-D | ||

| ЭКФ1533КП17 | SN74ALS353 | Сдвоенный инверсный селектор-мультиплексор 4х1 с тремя состояниями на выходе | 4307.16-А | ||

| КР1533КП18 | SN74ALS158 | Четырeхразрядный селектор-мультиплексор 2-1 с инверсными выходами | 2103Ю.16-D | ||

| ЭКФ1533КП18 | SN74ALS158 | Четырeхразрядный селектор-мультиплексор 2-1 с инверсными выходами | 4307.16-А | ||

| КР1533КП19 | SN74ALS352 | Сдвоенный инверсный селектор-мультиплексор 4х1 | 2103Ю.16-D | ||

| ЭКФ1533КП19 | SN74ALS352 | Сдвоенный инверсный селектор-мультиплексор 4х1 | 4307.16-А | ||

| КР1533ЛА1 | SN74ALS20 | Два логических элемента “4И-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛА1 | SN74ALS20 | Два логических элемента “4И-НЕ” | 4306.14-А | ||

| КР1533ЛА2 | SN74ALS30 | Логический элемент “8И-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛА2 | SN74ALS30 | Логический элемент “8И-НЕ” | 4306.14-А | ||

| КР1533ЛА3 | SN74ALS00 | Четыре логических элемента “2И-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛА3 | SN74ALS00 | Четыре логических элемента “2И-НЕ” | 4306.14-А | ||

| КР1533ЛА4 | SN74ALS10 | Три логических элемента “3И-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛА4 | SN74ALS10 | Три логических элемента “3И-НЕ” | 4306.14-А | ||

| КР1533ЛА7 | SN74ALS22 | Два логических элемента “4И-НЕ” с открытыми коллекторными выходами | 2102Ю.14-В | ||

| ЭКФ1533ЛА7 | SN74ALS22 | Два логических элемента “4И-НЕ” с открытыми коллекторными выходами | 4306.14-А | ||

| КР1533ЛА8 | SN74ALS01 | Четыре логических элемента “2И-НЕ” с открытым коллекторным выходом | 2102Ю.14-В | ||

| ЭКФ1533ЛА8 | SN74ALS01 | Четыре логических элемента “2И-НЕ” с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛА9 | SN74ALS03 | Четыре логических элемента “2И-НЕ” с открытым коллекторным выходом | 2102Ю.14-В | ||

| ЭКФ1533ЛА9 | SN74ALS03 | Четыре логических элемента “2И-НЕ” с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛА10 | SN74ALS12 | Три трeхвходовых логических элемента “И-НЕ” с открытым коллекторным выходом | 2102Ю.14-В | ||

| ЭКФ1533ЛА10 | SN74ALS12 | Три трeхвходовых логических элемента “И-НЕ” с открытым коллекторным выходом | 4306.14-А | ||

| КР1533ЛА21 | SN74ALS1000 | Четыре логических элемента “2И-НЕ”с повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКФ1533ЛА21 | SN74ALS1000 | Четыре логических элемента “2И-НЕ”с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛА22 | SN74ALS1020 | Два логических элемента “4И-НЕ”с повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКФ1533ЛА22 | SN74ALS1020 | Два логических элемента “4И-НЕ”с повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛА23 | SN74ALS1003 | Четыре логических элемента “2И-НЕ” с открытым коллекторным выходом и повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКФ1533ЛА23 | SN74ALS1003 | Четыре логических элемента “2И-НЕ” с открытым коллекторным выходом и повышенной нагрузочной способностью | 4306.14-А | ||

| КР1533ЛА24 | SN74ALS1010 | Три буфера “3И-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛА24 | SN74ALS1010 | Три буфера “3И-НЕ” | 4306.14-А | ||

| КР1533ЛЕ1 | SN74ALS02 | Четыре логических элемента “2ИЛИ-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛЕ1 | SN74ALS02 | Четыре логических элемента “2ИЛИ-НЕ” | 4306.14-А | ||

| ЭКФ1533ЛЕ1Б | SN74ALS02 | Четыре логических элемента “2ИЛИ-НЕ” | 4306.14-А | ||

| КР1533ЛЕ4 | SN74ALS27 | Три логических элемента “3ИЛИ-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛЕ4 | SN74ALS27 | Три логических элемента “3ИЛИ-НЕ” | 4306.14-А | ||

| КР1533ЛЕ10 | SN74ALS1002 | Четыре логических элемента “2ИЛИ-НЕ” | 2102Ю.14-В | ||

| ЭКФ1533ЛЕ10 | SN74ALS1002 | Четыре логических элемента “2ИЛИ-НЕ” | 4306.14-А | ||

| КР1533ЛЕ11 | SN74ALS33 | Четыре логических элемента “2ИЛИ-НЕ” с открытым коллекторным выходом с повышенной нагрузочной способностью | 2102Ю.14-В | ||

| ЭКР1533ИР27А | SN74ALS377 | Восьмиразрядный регистр с разрешением записи | 2140.20-В | ||

| ЭКФ1533ИР27А | SN74ALS377 | Восьмиразрядный регистр с разрешением записи | 4321.20-В | ||

| ЭКР1533ИР29 | SN74ALS323 | Восьмиразрядный сдвиговый регистр с тремя состояниями | 2140.20-В | ||

| ЭКФ1533ИР29 | SN74ALS323 | Восьмиразрядный сдвиговый регистр с тремя состояниями | 4321.20-В | ||

| КР1533ИР30 | SN74ALS259 | Восьмиразрядный регистр хранения с адресацией | 2103Ю.16-D | ||

| ЭКФ1533ИР30 | SN74ALS259 | Восьмиразрядный регистр хранения с адресацией | 4307.16-А | ||

| КР1533ИР32 | SN74ALS170 | 4х4 регистровый файл с открытым коллекторным выходом | 2103Ю.16-D | ||

| ЭКФ1533ИР32 | SN74ALS170 | 4х4 регистровый файл с открытым коллекторным выходом | 4307.16-А | ||

| ЭКР1533ИР33 | SN74ALS573 | Восьмиразрядный буферный регистр | 2140.20-В | ||

| ЭКФ1533ИР33 | SN74ALS573 | Восьмиразрядный буферный регистр | 4321.20-В | ||

| ЭКР1533ИР34 | SN74ALS873 | Два четырeхразрядных буферных регистра с тремя устойчивыми состояниями | 2140.20-В | ||

| ЭКФ1533ИР34 | SN74ALS873 | Два четырeхразрядных буферных регистра с тремя устойчивыми состояниями | 4322.24-А | ||

| ЭКР1533ИР35 | SN74ALS273 | Восьмиразрядный регистр с установкой в “ноль” | 2140.20-В | ||

| ЭКФ1533ИР35 | SN74ALS273 | Восьмиразрядный регистр с установкой в “ноль” | 4321.20-В | ||

| ЭКР1533ИР37 | SN74ALS574 | Регистр восьмиразрядный буферный с тремя состояниями на выходе (с импульсным управлением) | 2140.20-В | ||

| ЭКФ1533ИР37 | SN74ALS574 | Регистр восьмиразрядный буферный с тремя состояниями на выходе (с импульсным управлением) | 4321.20-В | ||

| ЭКР1533ИР38 | SN74ALS874 | Два четырeхразрядных регистра D-типа с тремя устойчивыми состояниями на выходе | 2142.24-А | ||

| ЭКФ1533ИР38 | SN74ALS874 | Два четырeхразрядных регистра D-типа с тремя устойчивыми состояниями на выходе | 4322.24-А | ||

| КР1533КП2 | SN74ALS153 | Сдвоенный цифровой селектор-мультиплексор 4-1 | 2103Ю.16-D | ||

| ЭКФ1533КП2 | SN74ALS153 | Сдвоенный цифровой селектор-мультиплексор 4-1 | 4307.16-А | ||

| КР1533КП7 | SN74ALS151 | Селектор-мультиплексор на 8 каналов со стробированием | 2103Ю.16-D | ||

| ЭКФ1533КП7 | SN74ALS151 | Селектор-мультиплексор на 8 каналов со стробированием | 4307.16-А | ||

| КР1533ИП4 | SN74ALS182 | Схема ускоренного переноса | 2103Ю.16-D | ||

| ЭКФ1533ИП4 | SN74ALS182 | Схема ускоренного переноса | 4307.16-А | ||

| КР1533ИП5 | SN74ALS280 | Девятиразрядная схема контроля чeтности | 2102Ю.14-В | ||

| ЭКФ1533ИП5 | SN74ALS280 | Девятиразрядная схема контроля чeтности | 4306.14-А | ||

| КР1533ИП6 | SN74ALS242 | Четырёхшинный приeмопередатчик с инверсными выходами | 2102Ю.14-В | ||

| ЭКФ1533ИП6 | SN74ALS242 | Четырёхшинный приeмопередатчик с инверсными выходами | 4306.14-А | ||

| КР1533ИП7 | SN74ALS243 | Четырeхшинный приeмопередатчик | 2102Ю.14-В | ||

| ЭКФ1533ИР10 | SN74ALS166 | Восьмиразрядный сдвиговый регистр | 4307.16-А | ||

| КР1533ИР15 | SN74ALS173 | Четырeхразрядный регистр с тремя состояниями выхода | 2103Ю.16-D | ||

| ЭКФ1533ИР15 | SN74ALS173 | Четырeхразрядный регистр с тремя состояниями выхода | 4307.16-А | ||

| КР1533ИР16 | SN74ALS295 | Четырeхразрядный универсальный сдвиговый регистр | 2102Ю.14-В | ||

| ЭКФ1533ИР16 | SN74ALS295 | Четырeхразрядный универсальный сдвиговый регистр | 4306.14-А | ||

| ЭКР1533ИР22 | SN74ALS373 | Восьмиразрядный регистр на триггерах с защeлкой с тремя состояниями на выходе | 2140.20-В | ||

| ЭКФ1533ИР22 | SN74ALS373 | Восьмиразрядный регистр на триггерах с защeлкой с тремя состояниями на выходе | 4321.20-В | ||

| ЭКФ1533ИР22Б | SN74ALS373 | Восьмиразрядный регистр на триггерах с защeлкой с тремя состояниями на выходе | 4321.20-В | ||

| ЭКР1533ИР23 | SN74ALS374 | Восьмиразрядный регистр на триггерах с защeлкой с тремя состояниями на выходе | 2140.20-В | ||

| ЭКФ1533ИР23 | SN74ALS374 | Восьмиразрядный регистр на триггерах с защeлкой с тремя состояниями на выходе | 4321.20-В | ||

| ЭКР1533ИР24 | SN74ALS299 | Восьмиразрядный универсальный сдвиговый регистр | 2140.20-В | ||

| ЭКФ1533ИР24 | SN74ALS299 | Восьмиразрядный универсальный сдвиговый регистр | 4321.20-В | ||

| КР1533ИР26 | SN74ALS670 | 4х4 регистровый файл с тремя состояниями | 2103Ю.16-D | ||

| ЭКФ1533ИР26 | SN74ALS670 | 4х4 регистровый файл с тремя состояниями | 4307.16-А | ||

| КР1533АГ3 | SN74ALS123 | Два одновибратора с повторным запуском | 2103Ю.16-D | ||

| ЭКФ1533АГ3 | SN74ALS123 | Два одновибратора с повторным запуском | 4307.16-А | ||

| ЭКР1533АП3 | SN74ALS240 | Два четырехканальных формирователя с тремя состояниями на выходе с инверсией сигнала с инверсным управлением | 2140.20-В | ||

| ЭКФ1533АП3 | SN74ALS240 | Два четырехканальных формирователя с тремя состояниями на выходе с инверсией сигнала с инверсным управлением | 4321.20-В | ||

| ЭКР1533АП4 | SN74ALS241 | Два четырехканальных формирователя с тремя состояниями на выходе с прямым и инверсным управлением | 2140.20-В | ||

| ЭКФ1533АП4 | SN74ALS241 | Два четырехканальных формирователя с тремя состояниями на выходе с прямым и инверсным управлением | 4321.20-В | ||

| ЭКР1533АП5 | SN74ALS244 | Два четырехканальных формирователя с тремя состояниями на выходе с инверсным управлением | 2140.20-В | ||

| ЭКФ1533АП5 | SN74ALS244 | Два четырехканальных формирователя с тремя состояниями на выходе с инверсным управлением | 4321.20-В | ||

| ЭКР1533АП6 | SN74ALS245 | Восьмиканальный двунаправленный формирователь с тремя состояниями на выходе | 2140.20-В | ||

| ЭКФ1533АП6 | SN74ALS245 | Восьмиканальный двунаправленный формирователь с тремя состояниями на выходе | 4321.20-В | ||

| ЭКР1533АП9 | SN74ALS640 | Восьмиканальный двунаправленный формирователь с тремя состояниями на выходе | 2140.20-В | ||

| ЭКФ1533АП9 | SN74ALS640 | Восьмиканальный двунаправленный формирователь с тремя состояниями на выходе | 4321.20-В | ||

| ЭКР1533АП14 | SN74ALS465 | Восьмиканальный формирователь с тремя состояниями и без инверсии на выходе | 2140.20-В | ||

| ЭКФ1533АП14 | SN74ALS465 | Восьмиканальный формирователь с тремя состояниями и без инверсии на выходе | 4321.20-В | ||

| ЭКР1533АП15 | SN74ALS466 | Восьмиканальный формирователь с тремя состояниями и инверсией на выходе | 2140.20-В | ||

| ЭКФ1533АП15 | SN74ALS466 | Восьмиканальный формирователь с тремя состояниями и инверсией на выходе | 4321.20-В | ||

| ЭКР1533АП16 | SN74ALS643 | Восьмиканальный двунаправленный формирователь с тремя состояниями и инверсией в одном направлении и без инверсии в другом направлении на выходе | 2140.20-В | ||

| ЭКФ1533АП16 | SN74ALS643 | Восьмиканальный двунаправленный формирователь с тремя состояниями и инверсией в одном направлении и без инверсии в другом направлении на выходе | 4321.20-В | ||

| ЭКР1533ИД3 | SN74ALS154 | Дешифратор 4х16 | 2142.24-А | ||

| ЭКФ1533ИД3 | SN74ALS154 | Дешифратор 4х16 | 4322.24-А | ||

| КР1533ИД4 | SN74ALS155 | Сдвоенный дешифратор демультиплексор 2-4 | 2103Ю.16-D | ||

| ЭКФ1533ИД4 | SN74ALS155 | Сдвоенный дешифратор демультиплексор 2-4 | 4307.16-А | ||

| КР1533ИД7 | SN74ALS138 | Дешифратор демультиплексор из 3 в 8 | 2103Ю.16-D | ||

| ЭКФ1533ИД7 | SN74ALS138 | Дешифратор демультиплексор из 3 в 8 | 4307.16-А | ||

| КР1533ИД14 | SN74ALS139 | Два дешифратора демультиплексора из 2 в 4 | 2103Ю.16-D | ||

| ЭКФ1533ИД14 | SN74ALS139 | Два дешифратора демультиплексора из 2 в 4 | 4307.16-А | ||

| КР1533ИЕ2 | SN74ALS90 | Двоичный десятичный четырeхразрядный счeтчик | 2102Ю.14-В | ||

| ЭКФ1533ИЕ2 | SN74ALS90 | Двоичный десятичный четырeхразрядный счeтчик | 4306.14-А | ||

| КР1533ИЕ5 | SN74ALS93 | Двоичный четырeхразрядный счeтчик | 2102Ю.14-В | ||

| ЭКФ1533ИП7 | SN74ALS243 | Четырeхшинный приeмопередатчик | 4306.14-А | ||

| КР1533ИП15 | MB502A | Схема кодека для локальных сетей ЭВМ | 2142.24-А | ||

| КР1533ИР8 | SN74ALS164 | Восьмиразрядный последовательный сдвиговый регистр с параллельным выходом | 2102Ю.14-В | ||

| ЭКФ1533ИР8 | SN74ALS164 | Восьмиразрядный последовательный сдвиговый регистр с параллельным выходом | 4306.14-А | ||

| КР1533ИР9 | SN74ALS165 | Восьмиразрядный сдвиговый регистр с параллельным вводом информации | 2103Ю.16-D | ||

| ЭКФ1533ИР9 | SN74ALS165 | Восьмиразрядный сдвиговый регистр с параллельным вводом информации | 4307.16-А | ||

| КР1533ИР10 | SN74ALS166 | Восьмиразрядный сдвиговый регистр | 2103Ю.16-D | ||

| ЭКФ1533ИЕ5 | SN74ALS93 | Двоичный четырeхразрядный счeтчик | 4306.14-А | ||

| КР1533ИЕ6 | SN74ALS192 | Двоично-десятичный реверсивный счeтчик | 2103Ю.16-D | ||

| ЭКФ1533ИЕ6 | SN74ALS192 | Двоично-десятичный реверсивный счeтчик | 4307.16-А | ||

| КР1533ИЕ7 | SN74ALS193 | Четырeхразрядный двоичный реверсивный счeтчик | 2103Ю.16-D | ||

| ЭКФ1533ИЕ7 | SN74ALS193 | Четырeхразрядный двоичный реверсивный счeтчик | 4307.16-А | ||

| КР1533ИЕ9 | SN74ALS160 | Четырeхразрядный двоично-десятичный счeтчик с асинхронной установкой в состояние” Логический 0” | 2103Ю.16-D | ||

| ЭКФ1533ИЕ9 | SN74ALS160 | Четырeхразрядный двоично-десятичный счeтчик с асинхронной установкой в состояние” Логический 0” | 4307.16-А | ||

| КР1533ИЕ10 | SN74ALS161 | Четырехразрядный двоичный счетчик с асинхронной установкой в состояние “Логический 0” | 2103Ю.16-D | ||

| ЭКФ1533ИЕ10 | SN74ALS161 | Четырехразрядный двоичный счетчик с асинхронной установкой в состояние “Логический 0” | 4307.16-А | ||

| КР1533ИЕ11 | SN74ALS162 | Четырехразрядный двоично-десятичный счетчик с синхронной установкой в состояние “Логический 0” | 2103Ю.16-D | ||

| ЭКФ1533ИЕ11 | SN74ALS162 | Четырехразрядный двоично-десятичный счетчик с синхронной установкой в состояние “Логический 0” | 4307.16-А | ||

| КР1533ИЕ12 | SN74ALS190 | Синхронный четырeхразрядный десятичный счeтчик | 2103Ю.16-D | ||

| ЭКФ1533ИЕ12 | SN74ALS190 | Синхронный четырeхразрядный десятичный счeтчик | 4307.16-А | ||

| КР1533ИЕ13 | SN74ALS191 | Синхронный четырeхразрядный двоичный реверсивный счeтчик | 2103Ю.16-D | ||

| ЭКФ1533ИЕ13 | SN74ALS191 | Синхронный четырeхразрядный двоичный реверсивный счeтчик | 4307.16-А | ||

| КР1533ИЕ18 | SN74ALS163 | Четырeхразрядный двоичный счeтчик с синхронной установкой в состояние “Логический 0” | 2103Ю.16-D | ||

| ЭКФ1533ИЕ18 | SN74ALS163 | Четырeхразрядный двоичный счeтчик с синхронной установкой в состояние “Логический 0” | 4307.16-А | ||

| КР1533ИЕ19 | SN74ALS393 | Два четырeхразрядных двоичных счeтчика с индивидуальной синхронизацией и сбросом | 2102Ю.14-В | ||

| ЭКФ1533ИЕ19 | SN74ALS393 | Два четырeхразрядных двоичных счeтчика с индивидуальной синхронизацией и сбросом | 4306.14-А | ||

| ЭКР/КР1533ИП3 | SN74ALS181 | Арифметическо-логическое устройство | 2142.24-А | ||

| ЭКФ1533ИП3 | SN74ALS181 | Арифметическо-логическое устройство | 4322.24-А |

Урок 8.4 Триггеры, регистры, счетчики

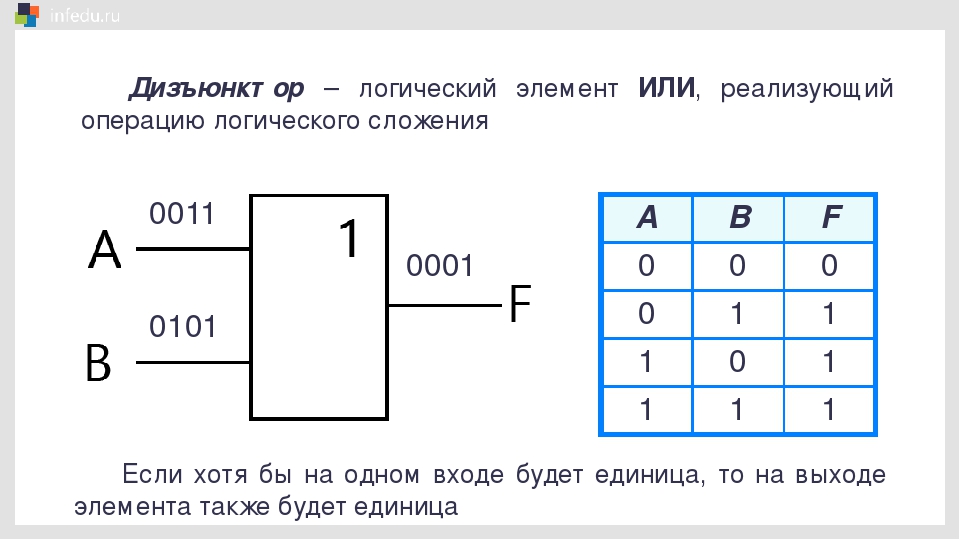

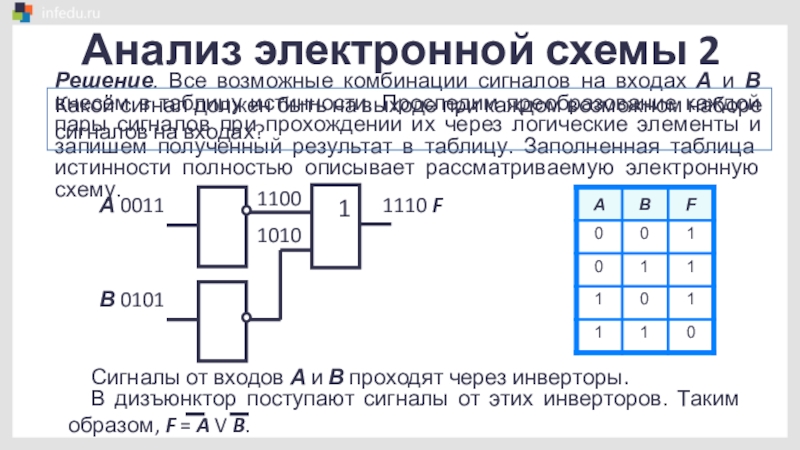

На предыдущем уроке мы рассмотрели логические элементы, состояние сигнала на выходе которых однозначно определяется состояниями сигналов на входах.

Логические элементы служат основой для создания более сложных цифровых устройств, одним из которых является триггер. Триггер – это целый класс электронных устройств, которые могут длительно находиться в одном из двух устойчивых состояний после прекращения сигнала, меняющего состояние. Состояние выхода триггера определяется не только сигналами на его входах, но и предыдущим состоянием устройства. Таким образом, триггер является простейшей однобитной ячейкой памяти.

RS-триггер

Самый простой триггер можно получить из двух логических элементов 2ИЛИ-НЕ:

Cхемотехническое обозначение:

Такая схема представляет собой асинхронный RS-триггер.

Он имеет два входа: S (set) – установка, R (reset) – сброс, и два выхода: Q (прямой) и Q с чертой сверху (инверсный, НЕ_Q).

При подаче сигнала логического нуля на оба входа триггера, его выходы будут установлены в произвольное состояние. Допустим, Q = 0, а НЕ_Q =1. Если на вход S подать «1», то состояние выхода Q скачкообразно изменится на «1», а НЕ_Q — на «0». И это состояние будет поддерживаться в независимости от того «0» или «1» подано на вход S, что и является проявлением свойства памяти.

Соответственно, при подаче уровня «1» на вход R выход Q станет «0», а НЕ_Q – «1».

Длительность устанавливающих импульсов может быть очень короткой, и ограничена физическим быстродействием логических модулей, из которых построен триггер.

Ситуация, когда на входах R и S действует высокий уровень, является недопустимой, поскольку при этом схема не может работать корректно. В этом есть недостаток RS-триггера.

RS-триггер также можно построить из двух элементов И-НЕ, такие элементы более распространены:

Установка и сброс триггера на элементах 2И-НЕ, в отличие от предыдущего, производится низким уровнем входного сигнала.

Если к последней схеме добавить еще два вентиля 2И-НЕ, то мы получим синхронный RS-триггер.

Изменение состояния такого триггера производится только при воздействии на вход С (Clock) синхронизирующего (тактового) импульса.

D-триггер

Немного изменив схему синхронного RS-триггера, можно получить D-триггер. (D-delay, задержка). У него только один информационный вход D.

Если на этот вход подать «1», а затем подать импульс на вход C, то на выходе Q будет «1», если на вход подать «0», затем импульс на C, то на выходе Q будет «0». Таким образом, D-триггер осуществляет задержку информации, поступающей на вход.

Если вход D соединить с выходом НЕ_Q, то триггер будет менять свое состояние при каждом изменении состояния входа С от «0» к «1» . При изменении от «1» к «0» состояние триггера меняться не будет. Таким образом, частота выходных импульсов будет вдвое меньше частоты входных импульсов. Такой триггер называется счетным или T-триггером. Делитель частоты используется очень широко в цифровой технике.

Существует разновидность синхронного RS-триггера, не имеющая запрещенной комбинации – JK-триггер. Он имеет три входа: J (вместо R), K (вместо S), и C. Если на оба информационных входа подана «1», то JK-триггер работает как счетный T-триггер с входом C.

Регистр хранения

На триггерах можно строить более сложные цифровые устройства, например такие, как регистры. Регистры предназначены для хранения многобитовой информации, то есть чисел, записанных в двоичном коде.

Рассмотри трех битовый регистр хранения на D-триггерах:

Каждый триггер может хранить один разряд (бит) числа. Вход R служит для установки выходов всех триггеров в нулевое (исходное) состояние перед записью числа, которое подается на входы D0,D1 и D2. При подаче импульса на вход C производится запись информации с этих входов. Информация может храниться сколь угодно долго, пока на вход С не подаются импульсы и подается питание.

Регистр сдвига

Другой разновидностью регистров является регистр сдвига. Он предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. На следующем рисунке приведена схема простейшего регистра сдвига информации вправо (по схеме):

В отличие от регистра хранения выход предыдущего триггера соединен с входом последующего. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд.

Сдвиговые регистры используются во многих схемотехнических решениях при построении цифровых устройств, прежде всего для преобразования последовательного кода в параллельный, а также для выполнения арифметических операций (умножения и деления на 2)с двоичными числами, организации линий задержки, формирования импульсов заданной длительности, генерирования псевдослучайных последовательностей (кодов) и т.п.

Счетчик

Еще один класс цифровых устройств, которые можно построить на триггерах – счетчики. Как следует из названия, они осуществляют счет входных импульсов в заданном коде и могут хранить результат.

Простейший счетчик с последовательным переносом можно получить с помощью счетных T-триггеров:

Подачей импульса на вход R счетчик приводится в исходное состояние, когда на выходах Q1-Q3 – уровень логического нуля.

На вход C подаются импульсы для счета. С приходом заднего фронта первого импульса первый (левый) по схеме триггер устанавливается в «1». Если читать код справа налево, то он соответствует единице. Для нашего трехразрядного счетчика это код 001. С приходом второго импульса в «1» переключается второй триггер, а первый переключается в «0». Таким образом, код на выходах счетчика будет 010, что соответствует десятичной цифре 2. Следующий импульс установит код 011, то есть 3. Трехразрядный счетчик может досчитать до кода 111, что соответствует десятичной цифре 7. При этом наступает так называемое переполнение счетчика, и с приходом следующего импульса счетчик обнулится.

Поскольку триггеры счетчика соединены последовательно, то и переключаться они будут также последовательно. Этот процесс отображен на графике, из которого видно, что время задержки переключения tз будет удваиваться и утраиваться. С увеличением числа разрядов задержка может оказаться неприемлемой, что является недостатком счетчиков с последовательным переносом.

Для повышения быстродействия применяются счетчики с параллельным переносом, что достигается одновременной подачей входных импульсов на входы всех триггеров счетчика. Это реализуется с помощью введения в схему логических элементов И:

Из схемы видно, что на вход второго триггера счетный импульс поступит только тогда, когда на выходе первого триггера будет «1», а на третий – когда «1» будет на выходах и первого, и второго триггеров. Очевидно, что с увеличением числа разрядов необходимо увеличивать как число логических элементов И, так и число их входов, что, в свою очередь, является недостатком такого типа счетчиков.

Регистры и счетчики, в свою очередь, могут применяться для построения более сложных цифровых устройств: сумматоров, ОЗУ и ПЗУ (оперативных и постоянных запоминающих устройств), АЛУ (арифметическо-логических устройств), входящих в состав процессоров, и так далее, к все более сложным цифровым устройствам.

В следующей серии статей мы начнем знакомство с микроконтроллерами — замечательным классом цифровых микросхем, которые являются настоящими компьютерами, умещающимися в одной микросхеме, и входящими входят в состав большинства электронных устройств, от кофемашины до космического корабля!

Изучение различных схем D-триггера и их функционирования

Лабораторная работа 3.3

D-триггер

Цель работы

Изучение различных схем D-триггера и их функционирования, приобретение навыков в определении характеристик триггеров.

Основные теоретические положения

Схема статического D-триггера представлена на рис. 1 (L3_D_01.ewb). Файлы для моделирования D-триггера расположены в папке Lab_3_3\Модели_1.

Схема D-триггера имеет один информационный вход D и тактовый вход C. На рис. 2 изображен D-триггер из поля элементов Digital и его таблица истинности (L3_D_02.ewb).

Рис. 1 D-триггер на логических элементах 2И-НЕ

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

Рис. 2 D-триггер из поля элементов Digital

Значок «Х» в таблице обозначает любую величину переменной, которая не оказывает влияния на результат.

Триггер (рис. 3), L3_D_03.ewb, имеет два приоритетных асинхронных входа установки S и сброса R (входы инверсные). Значком «Х» в таблице истинности обозначаются произвольные значения переменных D и C, которые не оказывают влияния на результат вследствие приоритета входов R, S. Комбинация R=S=0 запрещена, т.к. схема работает как асинхронный RS-триггер.

В случае еслиR=S=1, асинхронный триггер переходит в режим хранения и разрешается работа синхронного динамического D-триггера. Запись информации происходит при переходе из состояния 0 в состояние 1 сигнала на входе C.

Рис. 3 D-триггер из поля элементов Digital

На основе D-триггера можно получить другие триггеры, например, T-триггер (рис. 4), L3_D_04.ewb. Данный элемент является делителем частоты входного сигнала и используется в счетчиках. Сигнал на его вход подается с источника напряжения прямоугольной формы. Имеется служебный вход EI для разрешения его работы (E I=1).

Рис. 4 T-триггер на основе D-триггера

Схема реализации D-триггера с помощью универсального JK-триггера представлена на рисунке 5 (L3_D_05.ewb).

Рис. 5 D-триггер на основе JK-триггера

Триггер выпускается промышленностью в виде интегральных микросхем, например, микросхема 4013, содержащая два триггера (рис. 6), L3_D_06.ewb. Это синхронные динамические триггеры, таблица истинности которых представлена на рис. 6, а режим работы аналогичен ранее рассмотренным устройствам.

Рис. 6 D-триггер из поля элементов Digital

Принцип работы ячейки памяти

Триггеры могут использоваться в качестве оперативной памяти. Пример ячейки памяти приведен на рис. 7 (Модели_2\L3_M_01.ewb).

Для работы с ячейкой памяти используются шины из n проводников, по которым одновременно передается n разрядов двоичного кода (параллельная передача информации).

Обычно используются:

— адресные шины, с целью указания ячейки памяти или группы ячеек;

— шины данных, по которым обмениваются информацией отдельные устройства цифрового прибора;

— шины управления, для одновременного подключения к шине данных только двух устройств, одно передающее, другое принимающее информацию.

Вначале необходимо обратиться к конкретной ячейке согласно адресу, который представляет собой номера столбца (X) и строки (Y). На их пересечении расположена ячейка. Данная информация в виде двоичного параллельного кода X=1, Y=1 поступает по адресной шине.

Запись и считывание информации производится с шины данных (LD). Причем, при записи выход ячейки (Q) отключается от шины данных с помощью перевода буфера в закрытое состояние (F=0).

Для режима записи в ячейку, выбирается значение записываемой переменной D. Эта величина считывается с шины данных, которая для упрощения схемы не соединена с линией LD и подключена к источнику логической единицы через выключатель.

Только после этого, по шине управления (R) в ячейку передается команда записывать информацию в ячейку R=1 или считывать R=0.

Рис. 7 D-триггер в качестве ячейки памяти

Задание 1.

Определить логические сигналы на прямом и инверсном выходе триггеров, файлы L3_M_01.ewb – L3_M_08.ewb.

Задание 2.

Заполнить таблицу истинности (табл. 1) D – триггера, файл L3_D_03.ewb.

Таблица задания 2 Таблица 1

S’ | R’ | D | C | Qn+1 |

0 | 0 | Х | Х | |

0 | 1 | Х | Х | |

1 | 0 | Х | Х | |

1 | 1 | 0 | 0 | |

1 | 1 | 1 | 1 |

В таблице использовано: S’, R’ – инверсные значения S, R.Переключение по переднему фронту обозначать 0 – 1, по заднему: 1 – 0, что соответствует изменению сигнала от низкого значения до высокого значения и наоборот соответственно. Запрещенное состояние – запрет.

Задание 3. Заполнить таблицу истинности (табл. 2) для ячейки памяти, файл Модели_2\L3_M_01.ewb, в соответствии с указанными операциями в столбце Примечание.

Таблица задания 3 Таблица 2

X | Y | R | D | Q n+1 | F | LD | Примечание |

С ячейкой обмена информацией нет | |||||||

С ячейкой обмена информацией нет | |||||||

С ячейкой обмена информацией нет | |||||||

Запись в ячейку логической единицы | |||||||

Считывание из ячейки логической единицы | |||||||

Запись в ячейку логического нуля | |||||||

Считывание из ячейки логического нуля |

Использовать обозначения:Q n– предыдущее значение на выходе триггера;

X – любое значение переменной, которое не оказывает влияния на результат.

Выводы

Данный триггер является простейшей ячейкой памяти, имеет простую схему, и поэтому может использоваться в составе запоминающих устройств, требующих большого количества малогабаритных ячеек памяти. Кроме того, область применения в регистрах с последовательной записью и (или) считыванием (последовательный код) и т. д.

Динамическая работа триггеров позволяет снизить вероятность влияния помех при считывании информации из-за сокращения временного интервала записи.

виртуальных лабораторий

Проверить таблицу истинности триггеров RS, JK, T и D с помощью логических элементов И-И и И-И.

Введение

Триггер — это электронная схема с двумя стабильными состояниями, которая может использоваться для хранения двоичных данных. Сохраненные данные можно изменить, применяя различные входные данные. Триггеры и защелки являются фундаментальными строительными блоками систем цифровой электроники, используемых в компьютерах, средствах связи и многих других типах систем.

- Вьетнамки R-S

- Шлепанцы D

- Вьетнамки J-K

- T шлепанцы

1) Вьетнамки RS

Базовая схема RS-триггера логического элемента И-НЕ используется для хранения данных и, таким образом, обеспечивает обратную связь с обоих выходов обратно на входы. На самом деле триггер RS имеет три входа: SET, RESET и тактовый импульс.

Рисунок-1: Принципиальная схема R-S-триггера

Рисунок-2: Таблица характеристик R-S-триггера

D-триггер имеет единственный вход данных.Этот тип триггера получается из триггера SR путем подключения входа R через инвертор, а вход S подключается непосредственно к входу данных. Модифицированный тактовый SR-триггер известен как D-триггер и показан ниже. Из таблицы истинности триггера SR мы видим, что выход триггера SR находится в непредсказуемом состоянии, когда входы одинаковы и высоки. Во многих практических приложениях эти входные условия не требуются. Этих входных условий можно избежать, если они дополняют друг друга.

Рисунок-3: Принципиальная схема D-триггера

Рисунок-4: Таблица характеристик D-триггера

3) Вьетнамки JK

В триггере RS вход R = S = 1 приводит к неопределенному выходу. Цепь триггера RS может быть повторно соединена, если оба входа равны 1, а также выходы дополняют друг друга, как показано в таблице характеристик ниже.

Рисунок 5: Принципиальная схема триггера J-K

Рисунок 6: Таблица характеристик триггера JK

4) Тройник

ТриггерT известен как триггер с переключателем.Триггер T является модификацией триггера JK. Оба входа JK триггера JK удерживаются на уровне логической 1, и тактовый сигнал непрерывно изменяется, как показано в таблице ниже.

Рисунок-7: Принципиальная схема T-триггера

Рисунок-8: Таблица характеристик T-триггера

CSCE 436 — Конспект лекций

Шлепанцы D

Поскольку D-шлепанцы будут основной частью этой лекции, стоит потратив несколько минут на обзор их работы.Для начала выполните следующие временная диаграмма для выхода запускаемого отрицательным фронтом D-триггера с асинхронная активная линия сброса низкого уровня. Время установки, обозначенное t setup , — это время до нарастающего фронта.

часов, в которых входные данные должны быть стабильными.

Время удержания, обозначенное t hold , — это время после повышения.

край часов, в течение которого ввод данных должен быть стабильным. Наконец, распространение

задержка, обозначенная t p , — это время после нарастающего фронта тактового сигнала.

требуется, чтобы новое значение Q стало действительным.Он также известен как t CQ , что означает «часы до Q», или t FF . Эти

значения времени показаны на изображении ниже. Обратите внимание, что LH от низкого до высокого, а HL

от высокого к низкому.

Конечные автоматы

Конечный автомат (FSM) — это наиболее общая форма последовательной схемы, или схема, выход которой является функцией входа и внутреннего состояния. Логика автомата проиллюстрирована на рисунке ниже.Все сигналы X, Y, Q и Z являются векторами, состоящими из нуля или более битов.Сигнал X является входом в конечный автомат от управляемой системы — также называется битами состояния системы. Сигнал Z — это выход из конечного автомата в управляемую систему — также называется управляющими битами системы. Схема комбинационной логики, порождающая Z, называется выходными уравнениями (OE).

Состояние конечного автомата переносится по линиям Q. Каждый бит Q равен выход D-триггера, как показано на рисунке выше.Таким образом, если Q имеет ширину шесть бит, то автомат имеет шесть D-шлепанцев. Сигналы Y называются входами памяти ; они ввод данных в D-триггеры. Комбинационная логическая схема, генерирующая сигналы Y называются уравнениями ввода памяти (MIE) или «комбинированной логикой». Чтобы улучшить читаемость принципиальных схем, тактовый сигнал обычно не отображается.

Давайте переосмыслим утверждение «Результат конечного конечный автомат является функцией его входа и его внутреннего состояния «.На рисунке выше вы можете видеть, что Z = F (Q) и Q + = G (Q, X). Хотя выход Z не зависит напрямую от входа X, он зависит от состояние Q, которое, в свою очередь, зависит от входа X.

В отношении этой цифры необходимо ответить на три вопроса:

- Что такое МУИ?

- Что такое оригинальные запчасти?

- Сколько требуется D-шлепанцев?

Синхронизация конечного автомата

События, происходящие в автомате, относятся к тактовому входу D-шлепанцы внутри конечного автомата. На временной диаграмме ниже перечислены события. (пронумерованы кружками) относительно тактового сигнала, подаваемого на рисунок выше. В следующем списке объясняется, что происходит на каждом из в эти моменты времени, используя схему, обсуждавшуюся ранее.- Событие 1

- Так как вьетнамки входов на положительном фронте часов, эта точка является началом временной анализ.

- Событие 2

- Задержка распространения шлепки означают небольшую задержку между фронтом часов и флипом вывод флопа Q становится действительным. Это так называемая задержка распространения триггер и обозначен на диаграмме T FF .

- Событие 3

- Для увеличения тактовой частоты частоты конечного автомата, новые входы X на автомат должны применяться на в тот же момент, когда выходы триггера становятся действительными.

- Событие 4

- Согласно рисунку выше, изменение Q и X вызывает ввод памяти изменить (сигнал Y выше).Задержка между применением новых входов к логике MIE и вступлением Y в силу — задержка распространения комбинированной логики, обозначенная T combo .

- Событие 5 Когда значения Y действительны, происходит небольшая задержка, пока триггеры зарегистрируйте свои новые входы, обозначенные T su . По истечении этого времени настройки конечный автомат готов к другому фронту часов.

Система DAISY

Поскольку вы должны иметь некоторое представление о конечных автоматах по предыдущим курсовым работам, мы сразу перейдем к умеренно сложному примеру, который будет служить важная ступенька к важной концепции, изложенной в лекциях 10-13.В этом примере ваша задача — разработать высокотехнологичную систему отслеживания коров. система для местного молочного завода. Система называется Dairy Automated. Information SYstem, или сокращенно DAISY. Word Statement

Коровам прикреплена RFID-метка к ошейникам. Когда

корова проходит через желоб для скота на пути в коровник, RFID

считыватель считывает уникальный идентификатор, хранящийся на метке RFID, и регистрирует корову в

сарай. Система RFID выводит один бит: 1 означает, что система имеет

прочитал RFID-метку и успешно проверил корову обратно в стойло; а

0 означает, что RFID-система либо все еще обрабатывает тег, либо не обрабатывает его.

чтение тега.

Чтобы гарантировать сканирование каждой коровы, поток коров в стойло

контролируется двумя воротами на обоих концах желоба. Каждые ворота контролируются

единственный бит. Чтобы поднять ворота, на этом входе должна быть логическая 1; опустить калитку,

вход должен поддерживаться на уровне логического 0. Последовательность подъема и опускания

ворота для контроля потока коров показаны на рисунке ниже.

- Шаг 1

- Ворота 1 подняты, позволяя корове А войти в желоб.

- Шаг 2

- DAISY-система обнаружила, что корова A находится в желобе, и закрыла заслонку 1.

- Шаг 3

- Корова ждет в закрытом желобе, пока RFID-считыватель не подаст сигнал. что он прочитал тег и проверил корову A.

- Шаг 4

- Ворота 2 подняты, позволяя корове А уйти. Если корова потребляет больше, чем 30 секунд до отъезда, затем корову «сбивает» трехсекундная вспышка сжатый воздух. Воздушный удар повторяется с 30-секундными интервалами до тех пор, пока корова выходит из желоба.В любой момент, когда корова покидает желоб, выход 2 закрывается, и система возвращается к Шагу 1.

Входы в DAISY

Слово заявление предполагает существование из трех входов. Сканер RFID отправляет системе DAISY один бит который указывает, была ли обработана корова. Второй ввод сообщает Система DAISY, если корова находится в желобе.Последний ввод системы поступает от таймер, используемый для информирования DAISY системы об истечении 3 или 30 секунд. Мы дадим каждому из этих входов однобуквенное сокращение (показано на таблицу ниже), чтобы упростить построение диаграммы состояний, описывающей FSM.| Сканер RFID = r | Присутствие коровы = c | Состояние таймера = t |

| 1 — Корова зарегистрирована | 1 — Корова присутствует | 1 — Таймер включен |

| 0 — корова не обработана | 0 — корова нет | 0 — таймер работает |

Выходы из DAISY

Слово инструкция подразумевает наличие четырех отдельных выходных данных.В шлюзы в системе DAISY управляются одним битом каждый. Предположим, что логическая 1 должна постоянно применяться к воротам, чтобы они оставались поднятыми. Чтобы дать DAISY точное ощущение времени, предоставляется система. с одним таймером с двумя битами ввода и одним битом вывода. Чтобы использовать это таймер, установите таймер на 3 или 30 секунд для одного тактового цикла. Затем управляющий вход, дающий команду таймеру обратный отсчет, непрерывно применяемый. Выход таймера будет равен 0 до тех пор, пока установленный предел времени не истечет. expired, когда его выход будет оставаться на 1, пока не будет установлен новый интервал времени.Когда электронный клапан, управляющий сжатым воздухом, открыт, воздух устремляется вылезаю из коровы.| Gate1 | Gate2 | Таймер управления | Воздушный клапан |

| 1-ворота подняты | 1-ворота подняты | 00 Таймер остановки | 0 закрыто |

| 0-ворота вниз | 0-ворота вниз | 01 Установить на 30 секунд | 1 открыто |

| 10 Установить на 3 секунды | |||

| 11 Таймер работы |

Диаграмма состояния

Процесс создания диаграммы состояний DAISY система требует учета движения по этапам процесса требуется, чтобы провести одну корову через закрытый желоб.Каждый шаг в этом процессе затем становится состоянием или набором состояний. Каждое состояние утверждает некоторый вывод в управлять устройствами, подключенными к системе DAISY. Ниже приведен один из возможных список; возможны другие варианты.- Открытые ворота1

- Подождите, пока корова войдет в желоб

- Закрыть затвор 1

- Подождите, пока RFID прочитает корову

- Открытые ворота2

- Подождите, пока корова уйдет

- Если прошло 30 секунд, то «гусиная» корова; goto Шаг 6

- Иначе, если корова ушла, закройте ворота 2; goto Шаг 1

Память Уравнения ввода

Помните из первого рисунка, что уравнения ввода в память являются функцией как текущего состояния, так и входа. Входные уравнения памяти зависят от кодировки состояния — какой двоичный код присваивается каждому состоянию. Мы рассмотрим два плотных и один выстрел.Плотный Если вы решите использовать плотное кодирование, вы пытаетесь дать каждому указать двоичное представление, которое минимизирует количество переворотов. шлепки.Хотя на первый взгляд это кажется наиболее логичным ходом, мы увидим, что на самом деле это создает ряд трудностей. В качестве примера, давайте использовать кодировку состояния, указанную в Таблица ниже.

| Государственный | Код |

| WaitEnter | 000 |

| WaitRead | 001 |

| Set30 | 010 |

| ЖдатьВыйти | 011 |

| Set3 | 100 |

| Гусь | 101 |

Входной файл для эспрессо

.i 6 # .i определяет количество входов .o 3 # .o указывает количество выходов .ilb Q2 Q1 Q0 R C T # В этой строке указываются имена входов по порядку. .ob D2 D1 D0 # В этой строке указываются имена выходов по порядку. # Первые шесть цифр (перед пробелом) соответствуют # к входам, три после пробела соответствуют # к выходам, оба в указанном выше порядке. 000 -0- 000 # WaitEnter + c '=> WaitEnter 000-1-001 # WaitEnter + c => WaitRead 001 0 - 001 # WaitRead + r '=> WaitRead 001 1 - 010 # WaitRead + r => Set30 010 --- 011 # Set30 => WaitLeave 011-10 011 # WaitLeave + t'c => WaitLeave 011-11 100 # WaitLeave + tc => Set3 011-0- 000 # WaitLeave + c '=> WaitEnter 100 --- 101 # Set3 => Гусь 101 --0 101 # Гусь + t '=> Гусь 101 --1 010 # Гусь + t => Set30 .e # Обозначает конец файла.Выход

Этот уровень работы по выведению MIEs требует много времени и любые изменения означают, что нам придется переделывать всю эту работу. Честно говоря, это просто слишком больно. Давайте сравним это с другим кодирование называется горячим.

Горячие Горячее кодирование одного требует индивидуального триггера для каждого состояния. В нашем случае у нас будет 6 шлепанцев. Каждому состоянию присваивается триггер, который выводит 1, когда конечный автомат находится в этом состоянии.Таким образом термин «горячо» означает, что только одна из шлепанцев будет горячий (выход логической 1) за раз. Таблица ниже горячая кодирование для нашей диаграммы состояний.

| Государственный | Код |

| WaitEnter | 000001 |

| WaitRead | 000010 |

| Set30 | 000100 |

| WaitLeave | 001000 |

| Set3 | 010000 |

| Гусь | 100000 |

D_WaitEnter = Q_WaitEnter * c '+ Q_WaitLeave * c' D_WaitRead = Q_WaitRead * r '+ Q_WaitEnter * c D_Set30 = Q_WaitRead * r + Q_Goose * t D_WaitLeave = Q_Set30 + Q_WaitLeave * t '* c D_Set3 = Q_WaitLeave * t * c D_Goose = Q_Goose * t '+ Q_Set3

Выходные уравнения

Первым шагом в создании выходных уравнений является построение таблица управляющих слов — список таблиц, для каждого состояния, его вывод.| Состояние | Gate1 | Gate2 | Таймер | Управляющий воздух |

| 1 выход | 1 выход | 00 Таймер остановки | 0 — закрыт | |

| 0-ворота вниз | 0-ворота вниз | 01 Установлено на 30 секунд | 1 — открыто | |

| 10 Установить на 3 секунды | ||||

| 11 Таймер работы | ||||

| WaitEnter | 1 | 0 | 00 | 0 |

| WaitRead | 0 | 0 | 00 | 0 |

| Set30 | 0 | 1 | 01 | 0 |

| WaitLeave | 0 | 1 | 11 | 0 |

| Set3 | 0 | 1 | 10 | 0 |

| Гусь | 0 | 1 | 11 | 1 |

Z_Gate1Моделирование VHDL

Результаты моделирования VHDL, выполненного в ISim, можно увидеть ниже.

D-триггер (триггер задержки) Wiki — FPGAkey

Введение

D-триггер — это устройство хранения информации с функцией памяти и двумя стабильными состояниями.Это самая основная логическая единица, которая составляет множество последовательных схем, а также важная единичная схема в цифровых логических схемах.

Таким образом, D-триггеры широко используются в цифровых системах и компьютерах. Триггер имеет два стабильных состояния, а именно «0» и «1», которые можно переключать из одного стабильного состояния в другое под действием определенного внешнего сигнала.

D-триггеры состоят из интегрированных триггеров и схем затвора. Есть два режима запуска: запуск по уровню и запуск по фронту.Первый может срабатывать, когда CP (тактовый импульс) = 1, а второй чаще всего запускается по переднему фронту CP (положительный переход 0 → 1).

Второе состояние D-триггера зависит от состояния терминала D перед триггером, то есть второе состояние = D. Следовательно, у него есть две функции: установка 0 и установка 1.

Для триггеров края D, поскольку схема имеет эффект блокировки во время CP = 1, состояние данных клеммы D изменяется во время CP = 1 и не влияет на состояние выхода триггера.

D-триггеры широко используются и могут использоваться в качестве регистра цифровых сигналов, регистра сдвига, частотного деления и генератора сигналов и т. Д.

Структура

D-триггер состоит из 4-х вентилей NAND, среди которых G1 и G2 составляют базовый RS-триггер. Когда срабатывают триггеры «ведущий-ведомый», запускаемые по уровню, входной сигнал должен быть добавлен до положительного фронта.Если на входе присутствует сигнал помехи во время высокого уровня CP, то можно сделать состояние триггера неправильным. Триггер по фронту позволяет добавлять входной сигнал непосредственно перед фронтом триггера CP. Таким образом, время, в течение которого входной терминал нарушается, значительно сокращается, и уменьшается вероятность нарушения. Триггеры Edge D также называются триггерами Edge D с блокировкой сустейна. Ребро D-триггера может быть образовано путем последовательного соединения двух D-триггеров, но CP первого D-триггера необходимо поменять местами с помощью логического элемента НЕ.

Принцип работы

SD и RD подключаются к входным клеммам базового триггера RS. Это терминалы предустановки и сброса соответственно, они активны на низком уровне. Когда SD = 1 и RD = 0 (ненулевое значение SD и ненулевое значение RD равны 1, то есть значение уровня, вводимое извне в два порта управления, причина в том, что низкий уровень действует), независимо от входной клеммы D В каждом состоянии Q = 0, Q not = 1, то есть триггер установлен в 0; когда SD = 0 и RD = 1 (SD не равно 1, RD не равно 0), Q = 1, Q не = 0, триггер установлен на 1, SD и RD обычно вызываются напрямую установленными на 1 и установлен на 0.Мы предполагаем, что всем им добавлен высокий уровень, который не влияет на работу схемы.